# **Testability of VLSI**

# Lecture 07: Automatic Test Pattern Generation for Combinational Circuits

# By Dr. Sanjay Vidhyadharan

COMMUNICATION

INSTRUMENTATION

ELECTRONICS

ELECTRICAL

## **ATPG Algorithm**

Roth's **D-Algorithm** (D-ALG), established the calculus and algorithms for ATPG using D-cubes.

The next development was Goel's **PODEM** algorithm. He efficiently used path propagation constraints to limit the ATPG algorithm search space, and introduced the notion of *backtrace*.

The third significant development was Fujiwara and Shimono's **FAN** algorithm. They efficiently constrained the backtrace to speed up search, and took advantage of signal information to limit the search space.

COMMUNICATION

9/3/2023

ELECTRICAL

ELECTRONICS

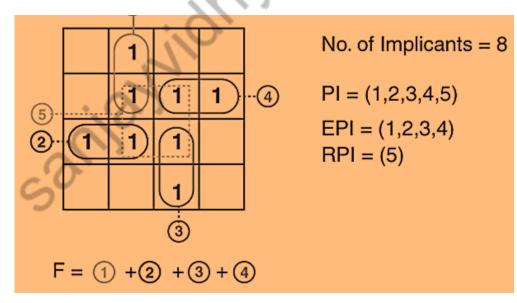

## **Prime Implicants**

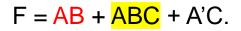

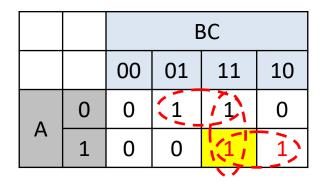

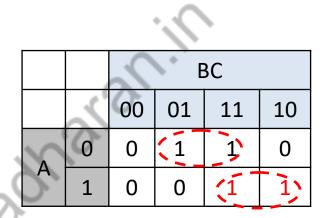

Prime Implicants = AB + BC + A'C.

**ELECTRONICS**

Essential Prime Implicants = AB + A'C.

COMMUNICATION

9/3/2023

**ELECTRICAL**

INSTRUMENTATION

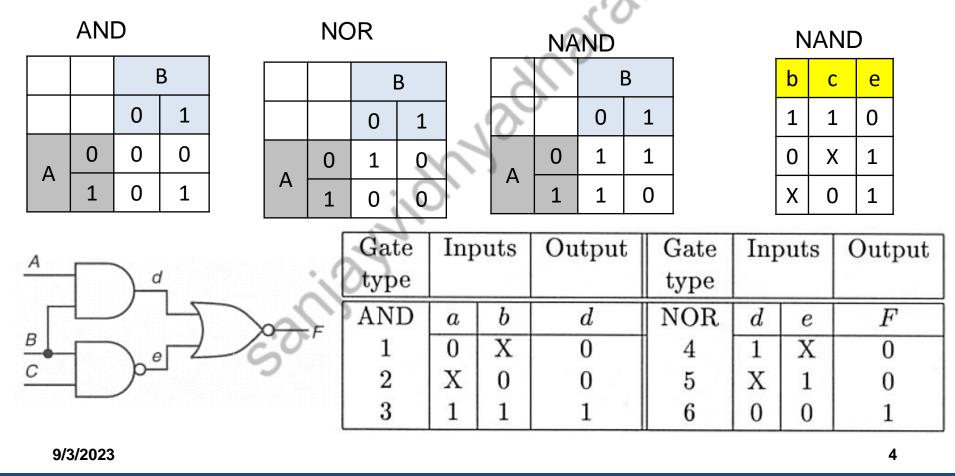

**Definition 1**. The *singular cover* of a logic gate is the minimal set of input signal assignments needed to represent *essential prime implicants* in the Karnaugh map of that logic gate, for both output cases of 0 and 1.

**Definition 2**. The *D-frontier* consists of all gates whose output value is currently x but have one or more error signals (either D's or D's) on their inputs. Error propagation consists of selecting one gate from the D-frontier and assigning values to the unspecified gate inputs so that the gate output becomes D or D. This procedure is also referred to as the D-drive operation. If the D-frontier becomes empty during the execution of the algorithm, then no error can be propagated to a PO. Thus an empty D-frontier shows that backtracking should occur.

COMMUNICATION

9/3/2023

ELECTRICAL

**ELECTRONICS**

**Definition 3**. The *Unique D-frontier*. There is only one gate in the D-frontier and the fault needs to be propagated through it.

COMMUNICATION

9/3/2023

**ELECTRICAL**

**ELECTRONICS**

**Definition 4**. The *J-frontier*. To keep track of the currently unsolved line-justification problems, we use a set called the J-frontier, which consists of all gates whose output value is known but is not implied by its input values.

COMMUNICATION

9/3/2023

**ELECTRICAL**

**ELECTRONICS**

**Definition 4**. The *J-frontier*. To keep track of the currently unsolved line-justification problems, we use a set called the J-frontier, which consists of all gates whose output value is known (requirement) but is not implied by its input values.

COMMUNICATION

9/3/2023

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

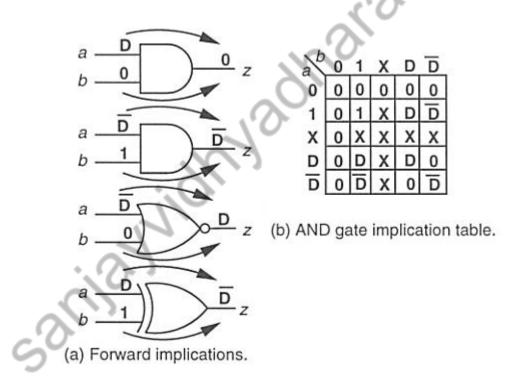

**Definition 5.** A *Propagation D-cube* is a collapsed truth table entry that can be used to characterize an arbitrary logic block.

AND gate propagation D-cube D,1,D or D', 1, D' or D,D,D or D',D',D'

OR gate *propagation* D-cube D,0,D or D',0, D' or D,D,D, or D',D',D'

NOR gate *propagation* D-cube D,0,D' or D',0, D

NAND gate *propagation* D-cube D,1,D' or D',1, D

ELECTRONICS

ELECTRICAL

COMMUNICATION

**Definition 6**. *Primitive D-cubes of failure (PDCF)* model faults in a logic circuit, and can model any (1) stuck-at-0 fault, (2) stuck-at-1 fault, (3) bridging fault (short circuit), or (4) arbitrary change in logic gate function (e.g., from AND to OR.)

AND Sa0 PCDF 11D

OR Sa0 PCDF? X1D or 1XD

**ELECTRONICS**

OR Sa1 PCDF ? 00D'

**ELECTRICAL**

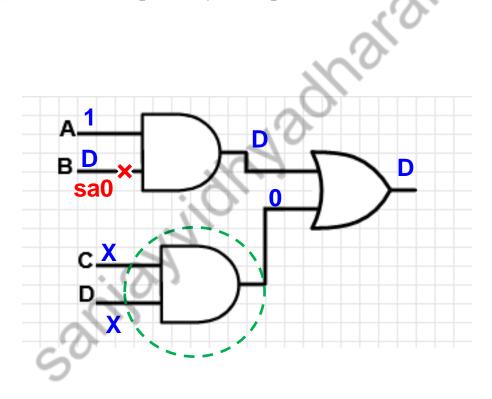

**Definition 7**. *Forward implication* results when the inputs to a logic gate are significantly labeled so that the output can be uniquely determined. Gate is removed from *D-frontier List*

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

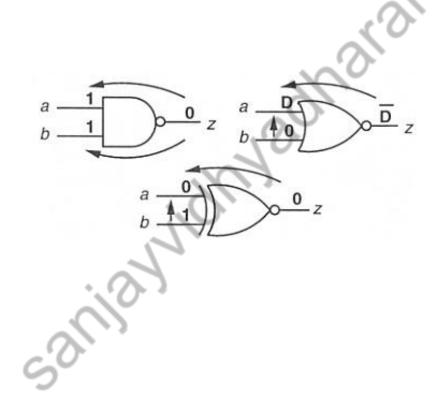

**Definition 8**. *Backward implication* is the unique determination of all inputs of a gate for given output and possibly some of the inputs.. Gate is removed from *J-frontier List*

COMMUNICATION

9/3/2023

**ELECTRICAL**

**ELECTRONICS**

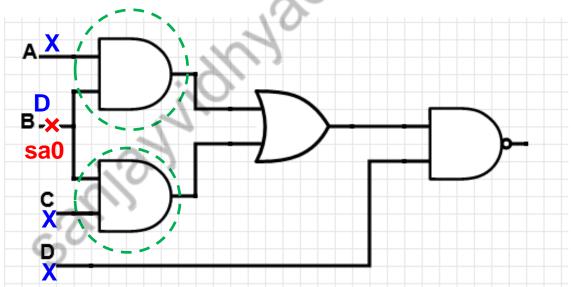

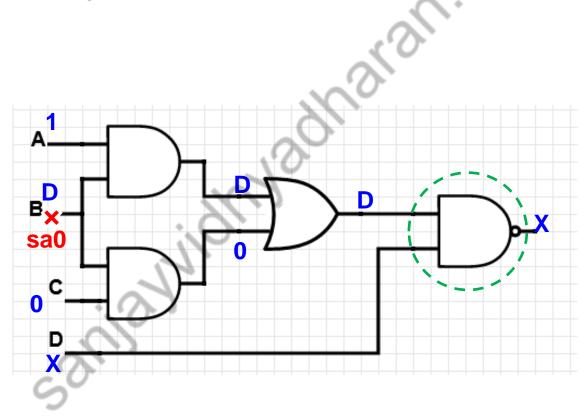

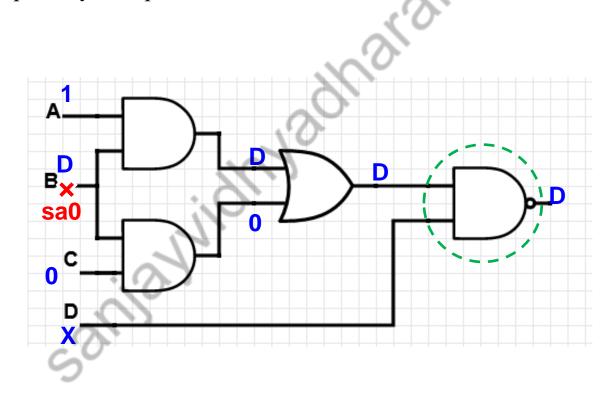

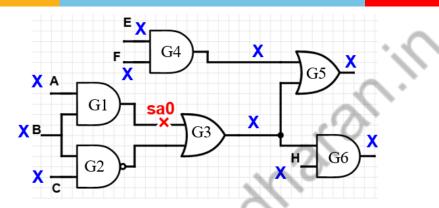

#### **Procedure**.

- 1. Pick a fault from the Fault table for a node

- 2. Select e PDCF for the fault.

- 3. D-Drive : Propagate the fault choosing from the D-frontier gates (Forward implication)

- 4. Back Propagate to get consistent inputs. If inconsistently encountered back track and chose alternate path.

COMMUNICATION

ELECTRONICS

9/3/2023

ELECTRICAL

|                                         |   |    |        |   |   |   |    |    |    |    | -  |    | -                           |

|-----------------------------------------|---|----|--------|---|---|---|----|----|----|----|----|----|-----------------------------|

| Step                                    | A | В  | C      | E | F | н | G1 | G2 | G3 | G4 | G5 | G6 |                             |

| 1. Choose a fault.<br>Sa0 at G1.        | 1 | 1  | X      | X | X | X | 8  | x  | X  | X  | X  | X  | PCDF G1<br>DF{G3}           |

| 2. Forward<br>Implication               | 1 | 1  | X      | X | X | x | D  | 0  | D  | x  | x  | x  | <b>JF{G2}</b><br>DF{G5. G6} |

| 3. Forward<br>Implication<br>Choose G5  | 1 | 1  | ×      | × | x | X | D  | 0  | D  | 0  | D  | X  | JF{G2, G4}                  |

| 4. Backward<br>Implication              | 1 | 10 | x      | 0 | X | X | D  | 0  | D  | 0  | D  | x  | JF{G2}                      |

| 5.Backward                              | 1 | 1  | 1      | 0 | Х | Х | D  | 0  | D  | 0  | D  | Х  | Done 14                     |

| Choose G5<br>4. Backward<br>Implication |   | 4  | x<br>1 |   |   |   |    |    |    |    |    |    |                             |

**ELECTRICAL**

#### ELECTRONICS

#### COMMUNICATION

#### **INSTRUMENTATION**

|                                        |   |    | - | 1 <u>A</u><br>B[<br>1 | E<br>GI<br>G2 |   | G4<br>sa0<br>× | )<br>G3> | D  | G<br>K<br>K | 8  | ×  |                             |

|----------------------------------------|---|----|---|-----------------------|---------------|---|----------------|----------|----|-------------|----|----|-----------------------------|

| Step                                   | A | В  | C | E                     | F             | н | G1             | G2       | G3 | G4          | G5 | G6 |                             |

| 1. Choose a fault.<br>Sa0 at G1.       | 1 | 1  | X | X                     | Х             | x | 5              | x        | X  | X           | X  | X  | PCDF G1<br>DF{G3}           |

| 2. Forward<br>Implication              | 1 | 1  | X | X                     | X             | x | D              | 0        | D  | X           | X  | x  | <b>JF{G2}</b><br>DF{G5. G6} |

| 3. Forward<br>Implication<br>Choose G5 | 1 | 1  | × | X                     | x             | X | D              | 0        | D  | 1           | D  | X  | JF{G2, G4}                  |

| 4. Backward<br>Implication             | 1 | 10 | x | 0                     | X             | X | D              | 0        | D  | 0           | D  | х  | JF{G2}                      |

| 5.Backward<br>9/3/2023                 | 1 | 1  | 1 | 0                     | Х             | Х | D              | 0        | D  | 1           | D  | Х  | Done<br>15                  |

**ELECTRICAL**

ELECTRONICS

#### COMMUNICATION

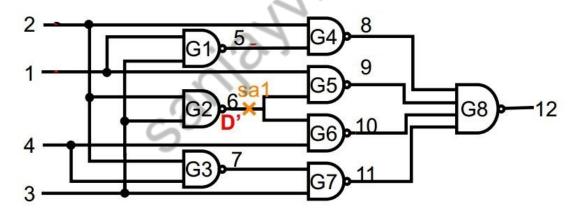

| 2 - 64 = 64 = 64 = 64 = 63 = 12 $4 - 63 = 63 = 7 = 67 = 11$ |     |     |     |        |   |     |           |      |    |    |    |     |                         |

|-------------------------------------------------------------|-----|-----|-----|--------|---|-----|-----------|------|----|----|----|-----|-------------------------|

| Step                                                        | 1   | 2   | 3   | 4      | 5 | 6   | 7         | 8    | 9  | 10 | 11 | 12  |                         |

| 1. Choose a fault.<br>Sa0 at G2.                            | X   | 1   | 1   | X      | X | 0,  | Х         | Х    | Х  | Х  | Х  | x   | PCDF G2<br>DF{G5,G6}    |

| 2. Choose G5.<br>Forward Implication                        | 1   | 1   | 1   | X      | x | D'  | Х         | х    | D  | Х  | x  | x   | DF{G8}                  |

| 3. Forward Implication.                                     | 1   |     | 1   | x      | X | D'  | Х         | 1    | D  | 1  | 1  | D'  | JF{G4, G6,G7}           |

| 4.Backward<br>Implication                                   | 1   | 5   | 1   | 0      | 0 | D'  | 0         | 1    | D  | 1  | 1  | D'  | JF{G1, G3}              |

| 5.Backward<br>Im <b>pligatio</b> n                          | 1   | 1   | 1   | 0<br>1 | 0 | D'  | 0         | 1    | D  | D  | 1  | X   | Contention for G7<br>16 |

| ELECTRICAL E                                                | LEC | ſRO | NIC | 'S     |   | CON | <b>IW</b> | INIC | AT | ON |    | INS | RUMENTATION             |

|                                  | 2 -<br>1 -<br>4 -<br>3 - |   |   |   | G |    | a <u>1</u><br>€ |   |   | 8<br>9<br>10 |    | 68) | 12                   |

|----------------------------------|--------------------------|---|---|---|---|----|-----------------|---|---|--------------|----|-----|----------------------|

| Step                             | 1                        | 2 | 3 | 4 | 5 | 6  | 7               | 8 | 9 | 10           | 11 | 12  |                      |

| 1. Choose a fault.<br>Sa0 at G2. | X                        | 1 | 1 | X | X | Ď  | x               | X | X | X            | X  | X   | PCDF G2<br>DF{G5,G6} |

| 6. Choose G5 & G6                | 1                        | 1 | 1 | 1 | X | D' | x               | Х | D | D            | х  | Х   | DF{G8}               |

| 7. Forward<br>Implication.       | 1                        | 1 | 1 | 3 | x | D' | Х               | 1 | D | D            | 1  | D'  | JF{G4, G7}           |

| 8.Backward<br>Implication        | 1                        | ŝ | 1 | 1 | 0 | D' | 0               | 1 | D | D            | 1  | D'  |                      |

|                                  |                          |   |   |   |   |    |                 |   |   |              |    |     |                      |

9/3/2023

COMMUNICATION

#### Advantage

1. D algorithm is *complete ATPG* Guarantee to generate a pattern for a testable fault

#### Disadvantage

1. Internal nodes are also assigned values hence the search space is large 2. Does not help in choosing best D-Frontier and relies on back tracking

**ELECTRONICS**

9/3/2023

**ELECTRICAL**

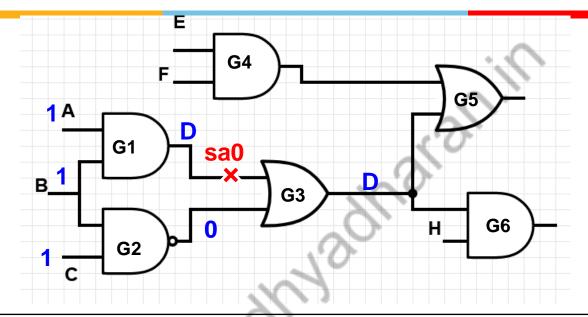

### PODEM

COMMUNICATION

- 1. Only allow assignments to *PI only* Doesn't assign internal nodes Greatly reduces search tree

- 2. Assigned PI are then forward implication No justification needed

- 3. Flip last PI assignment when two conditions:

**ELECTRONICS**

A. Fault not activatedB. No propagation path to any output

**ELECTRICAL**

### PODEM

- 1. Choose A=1 B=1 to det D at the desired fault location

- 2. Use G3 to Propagate. Single Option. C=1

3. Choose G6 easiest path to propagate . Level or SCOAP analysis will give the easiest path.

4.H=1. C=1 Depth First

ELECTRICAL

Minimum number of logic gates between the start of the path and any PO. Objectives were selected by level to pick the *easiest* objective to achieve. After objectives were selected, backtracing determined PI assignments to justify these objectives.

### PODEM

The basic idea of PODEM is to limit the search space to primary inputs without compromising the completeness. That is done by using the backtrace

COMMUNICATION

**ELECTRONICS**

9/3/2023

**ELECTRICAL**

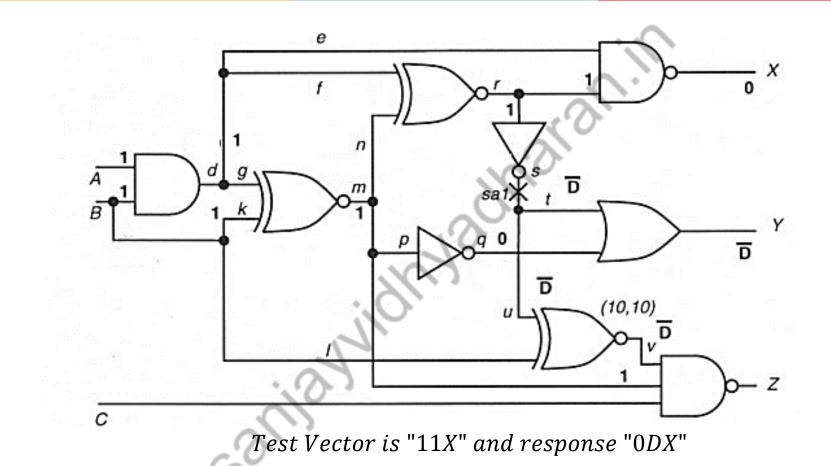

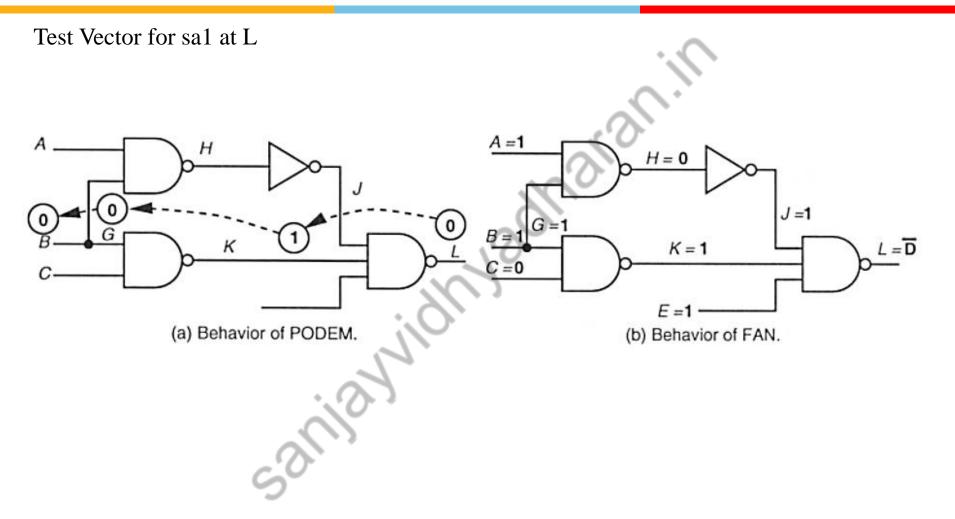

ELECTRICAL

ELECTRONICS

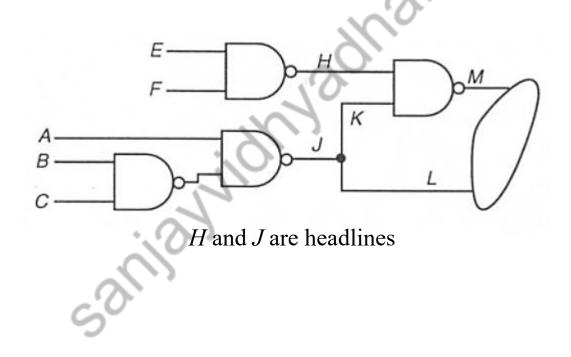

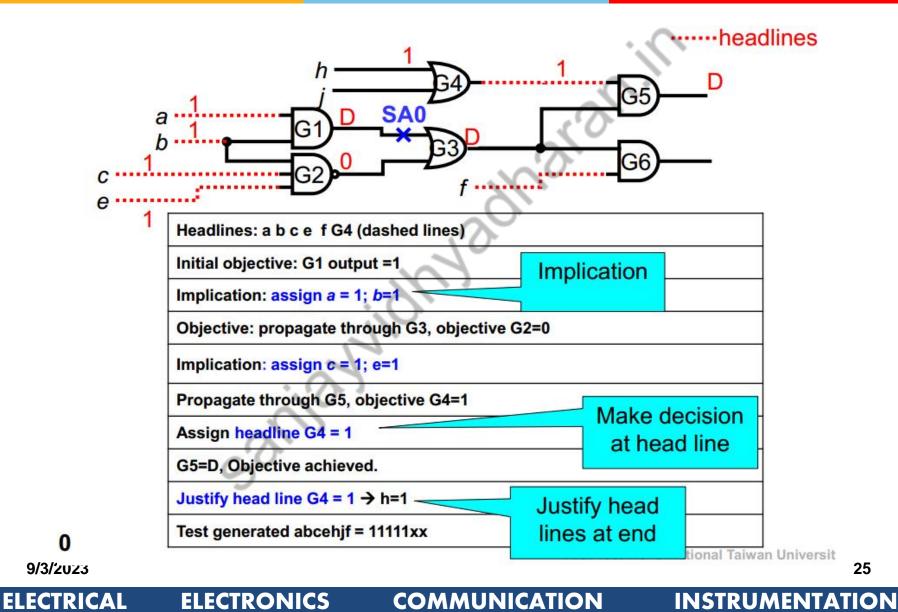

**Headlines.** Fujiwara and Shimono developed the notion of *headlines*, which are points where the circuit can be partitioned such that a cone of logic driven by PIs can be isolated from the rest of the circuit by cutting a single line, called the *headline*. This means that either a logic 0 or a logic 1 can be justified from the headline back to the circuit PIs.

COMMUNICATION

9/3/2023

ELECTRICAL

ELECTRONICS

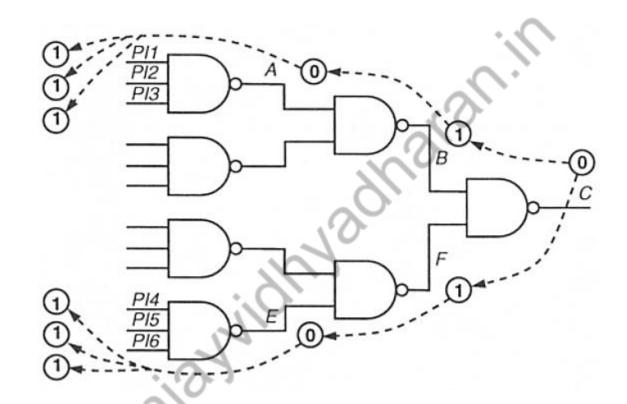

PODEM will make six backtraces to justify C=0. The first backtrace sets objectives of B=1 and A=0 and finally assigns PI1 as 1. This process is laboriously repeated five more times until we have PI2 =1, PI3 =1, PI4=1 PI5=1 and PI4=1 as internal node are not assigned any value. This is happening because PODEM backtraces in a depth-first fashion. 9/3/2023 24

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

**INSTRUMENTATION**

## References

"Essentials of Electronic Testing, for Digital, Memory and Mixed-Signal VLSI Circuits", Michael L. Bushnell and Vishwani D. Agrawal, – Kluwer Academic Publishers (2000).

Video lectures by Professor James Chien-Mo Li

Lab. of Dependable Systems Graduate Institute of Electronics Engineering National Taiwan University

https://www.youtube.com/watch?v=yfcoKOUV5DM&list=PLvd8d-SyI7hjk\_Ci0zpTqImAtpEjdK5JF&index=1

ELECTRICAL

ELECTRONICS

3. NPTEL Lectures https://www.youtube.com/watch?v=M8VEEaYwlQ&list=PLbMVogVj5nJTClnafWQ9F K2nt3cGG8kCF&index=31

COMMUNICATION

INSTRUMENTATION

**INSTRUMENTATION**

**ELECTRONICS**

**ELECTRICAL**

COMMUNICATION