# **Testability of VLSI**

# **Lecture 4: Logic Simulation**

# By Dr. Sanjay Vidhyadharan

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

**INSTRUMENTATION**

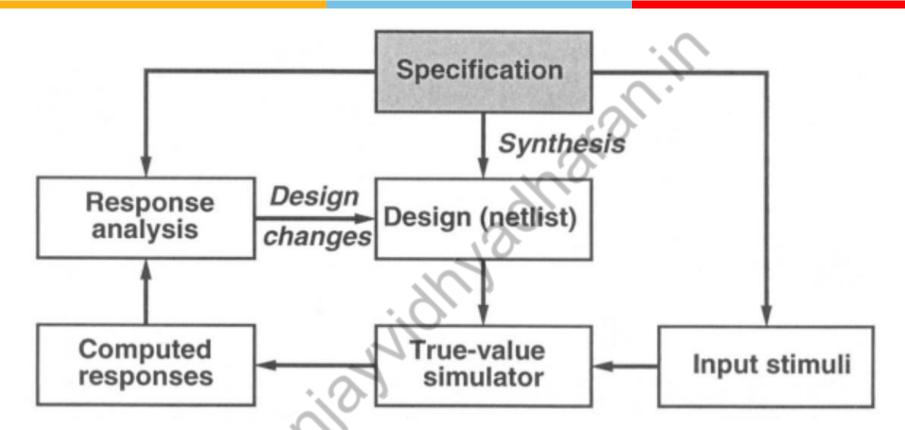

### **Simulation for Design Verification**

True-value means that the simulator will compute the response for given input stimuli without injecting any faults in the design. The input stimuli are also based on the specification.

A frequently used strategy is to exercise all functions with only *critical* data patterns. This is because the simulation of the exhaustive set of data patterns can be too expensive

8/13/2023

ELECTRICAL

#### **Simulation for Design Verification**

1. Why learn Design verification now?

2. Many concepts of verification like event driven simulation etc. representation of unknown as X etc. is used in Fault simulation algorithms also.

8/13/2023

**ELECTRONICS**

### **True Value Simulation**

- A design can be first simulated at a higher behavior level (such as C). Netlist not required Does not contain the detailed timing information.

- No electrical behavior

ELECTRONICS

- 2, Once this design is verified, higher-level blocks are replaced by logic-level netlists. At this point, a **logic simulator** is used for verification.

- 3. The process may be repeated by replacing some or all portions by transistor-level or circuit-level implementations.

COMMUNICATION

Simulation is used in this way for verifying very large electronic systems.

The weakness of this method is its dependence on the designer's heuristics used in generating the input stimuli.

8/13/2023

**ELECTRICAL**

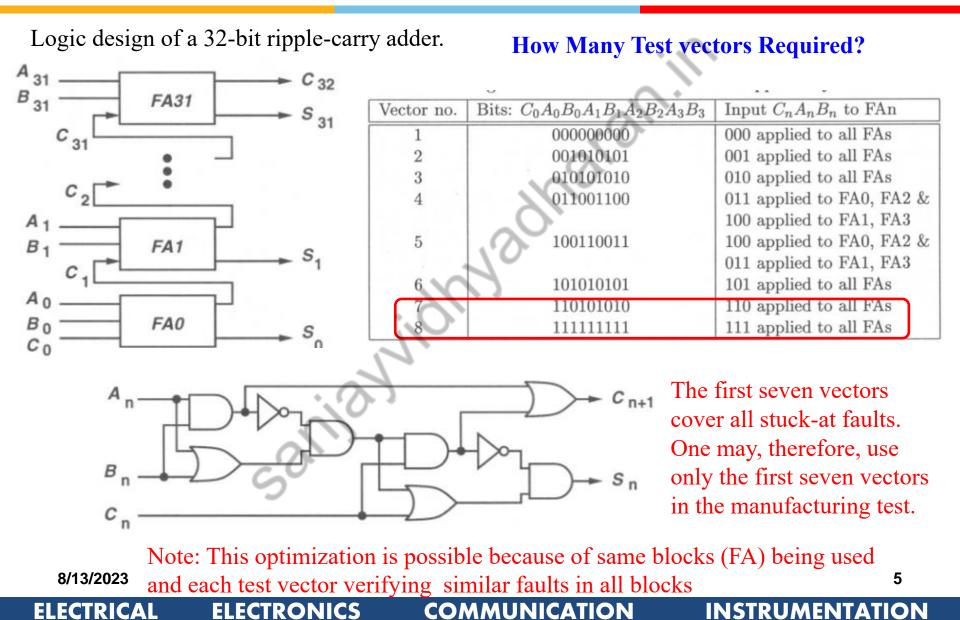

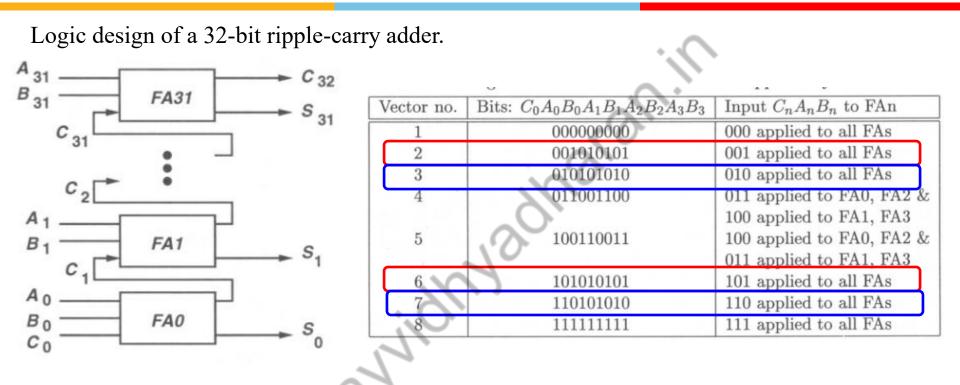

### **Simulation for Design Verification**

#### **Simulation for Design Verification**

Timing analysis of 2 followed by 6 or 3 followed by 7 where carry propagates through the chain . Only Possible for Modular Structure

COMMUNICATION

8/13/2023

ELECTRICAL

**ELECTRONICS**

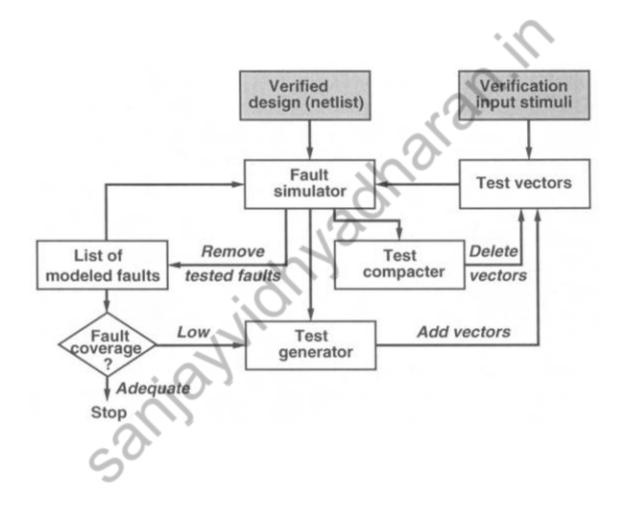

#### **Fault simulation for test generation**

COMMUNICATION

8/13/2023

**ELECTRICAL**

**ELECTRONICS**

8/13/2023

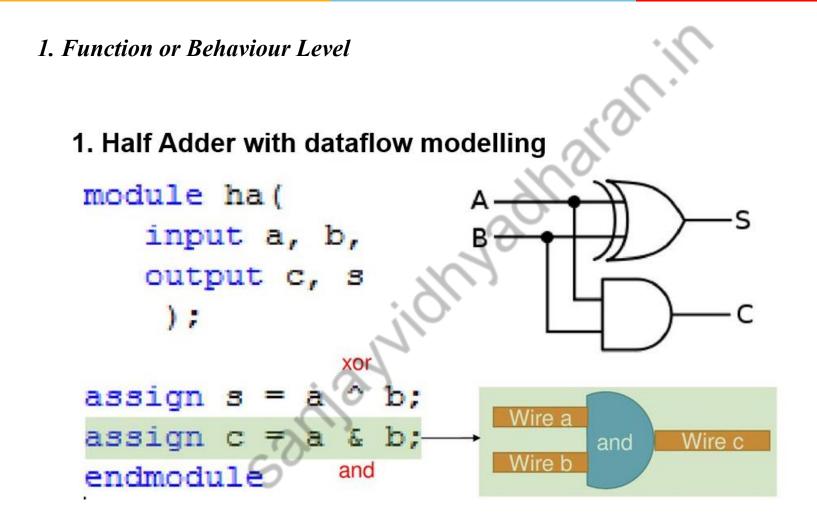

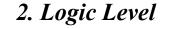

**Gate Level Modelling**

module Simple\_circuit (input A, input B, input C, output x, output y); wire w1;

and g1 (w1,A,B); // and gate instance not g2 (y,C); or g3 (x,w1,y);

#### endmodule

8/13/2023

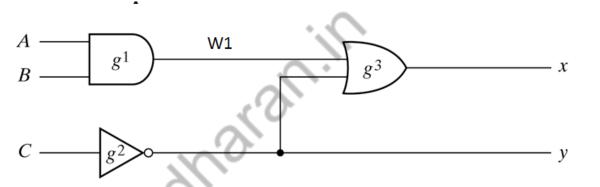

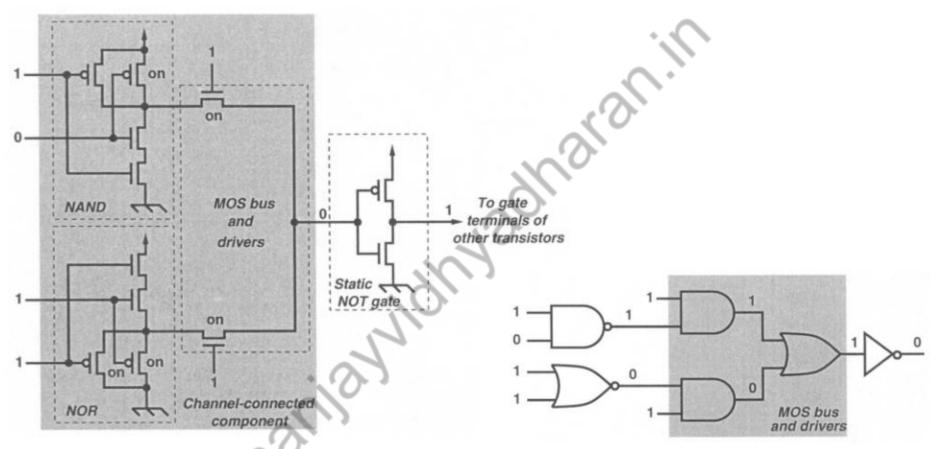

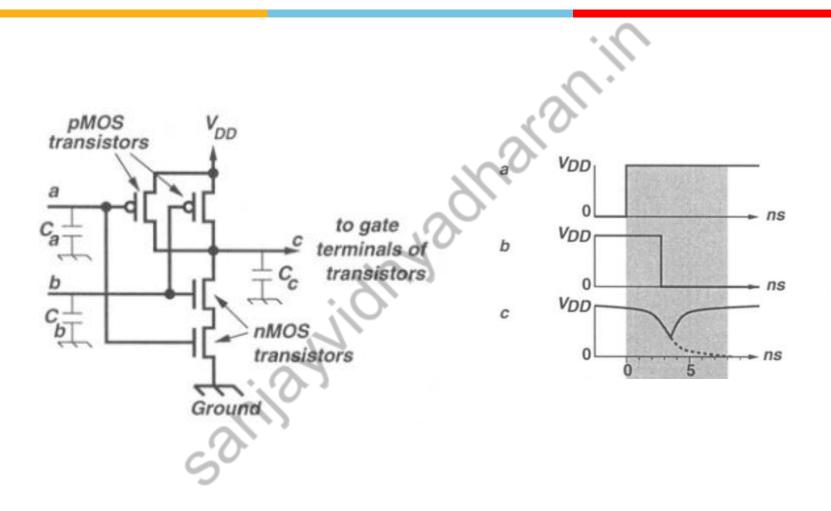

3. Switch Level

MOS transistors, which are treated as ideal switches

8/13/2023

#### 4. Circuit Level

This is the lowest level and represents the ultimate in accuracy for the simulation of electronic systems. The circuit is assumed to be composed of electrical elements such as resistors, capacitors, inductors, and transistors. Equations relating branch or loop currents and node voltages are developed and solved by numerical methods

COMMUNICATION

ELECTRONICS

8/13/2023

ELECTRICAL

**5.** *Timing Level* That is, the connectivity of transistors, their sizes and types, and node capacitances are needed. In addition, technology data specifying the transistor voltage-current characteristics are also used to compute charging or discharging currents for the nodes.

COMMUNICATION

8/13/2023

ELECTRICAL

#### **Transistor level Modelling**

ELECTRONICS

# **Why Circuit Level Modeling Is Important**

COMMUNICATION

If both control inputs are turned on, Results in High Currents

**ELECTRONICS**

If both control inputs are turned on, as, the 1 input will dominate.

8/13/2023

ELECTRICAL

### **Modeling Signal States**

| Inputs |   | Output     |            |                         |  |  |  |  |

|--------|---|------------|------------|-------------------------|--|--|--|--|

| a      | b | AND $(ab)$ | OR $(a+b)$ | $\mathbb{N}OT(\bar{a})$ |  |  |  |  |

| 0      | 0 | 0          | 0 2        | 1                       |  |  |  |  |

| 0      | 1 | 0          | 1          | 1                       |  |  |  |  |

| 0      | Х | 0          | 8.         | 1                       |  |  |  |  |

| 1      | 0 | 0          | 1          | 0                       |  |  |  |  |

| 1      | 1 | 1 :        | 0 1        | 0                       |  |  |  |  |

| 1      | Х | X          | 1          | 0                       |  |  |  |  |

| Х      | 0 | .00        | X          | X                       |  |  |  |  |

| X<br>X | 1 | (K)        | 1          | X                       |  |  |  |  |

| Х      | Х | X          | X          | X                       |  |  |  |  |

8/13/2023

COMMUNICATION

ELECTRICAL

**ELECTRONICS**

**INSTRUMENTATION**

16

ELECTRICAL

**ELECTRONICS**

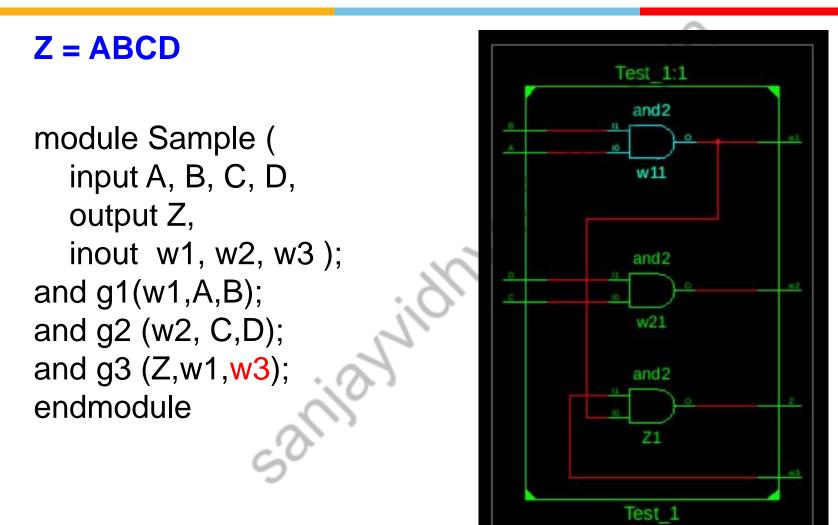

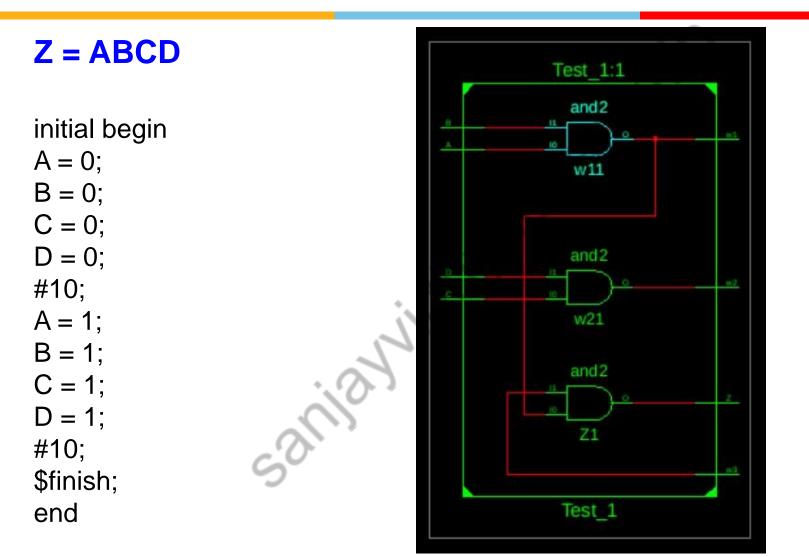

#### Z = ABCD

|          |            |                  |         |       |       | 20.000 ns      |  |

|----------|------------|------------------|---------|-------|-------|----------------|--|

| Name     | Value      | 0 ns             | 5 ns    | 10 ns | 15 ns | , , , <u>,</u> |  |

| ll₀ z    | x          |                  |         |       |       |                |  |

| 10 w1    | 1          | -                |         |       |       |                |  |

| 16 w2    | 1          |                  |         |       |       |                |  |

| 10 w3    | Z          |                  |         |       |       |                |  |

| 16 А     | 1          | -                |         |       |       |                |  |

| В        | 1          |                  |         |       |       |                |  |

| 16 C     | 1          |                  |         |       |       |                |  |

| 16 р     | 1          |                  |         |       |       |                |  |

|          |            |                  |         |       |       |                |  |

|          |            |                  |         |       |       |                |  |

|          |            |                  |         |       |       |                |  |

|          |            |                  |         |       |       |                |  |

|          |            |                  |         |       |       |                |  |

|          |            | X1: 20.000 ns    |         |       |       |                |  |

|          |            |                  |         |       |       |                |  |

| X (in re | ed) stands | s for Forcing Ur | nknown. |       |       | 17             |  |

**ELECTRICAL**

**ELECTRONICS**

18

ELECTRICAL

**ELECTRONICS**

19

ELECTRICAL

**ELECTRONICS**

2.1

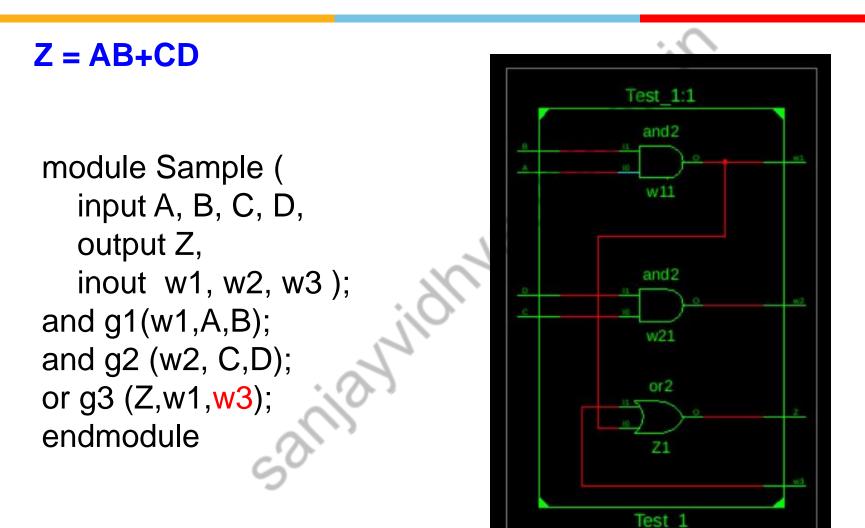

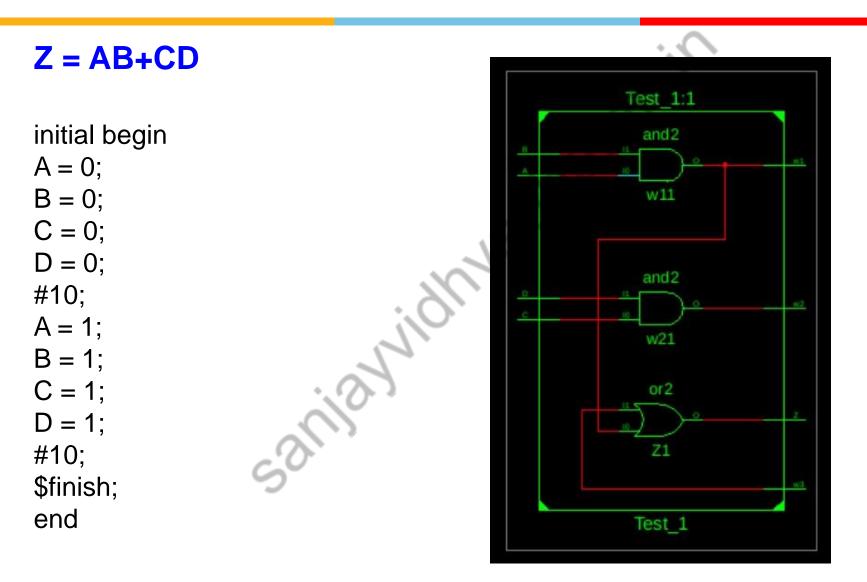

#### Z = AB+CD

|      |       |               |      |       | 20.000 ns |

|------|-------|---------------|------|-------|-----------|

| Name | Value | 0 ns          | 5 ns | 10 ns | 15 ns     |

| lo z | 1     |               | -    | 0     |           |

| 🔓 wl | 1     |               |      |       |           |

| w2   | 0     |               |      |       |           |

| 🐻 w3 | z     |               |      |       |           |

| 6 A  | 1     |               |      |       |           |

| 🧓 В  | 1     |               |      |       |           |

| ο C  | Θ     |               |      |       |           |

| g D  | Θ     |               |      |       |           |

|      |       |               |      |       |           |

|      |       |               |      |       |           |

|      |       |               |      |       |           |

|      |       |               |      |       |           |

|      |       |               |      |       |           |

|      |       |               |      |       |           |

|      |       | X1: 20.000 ns |      |       |           |

#### How is the Simulation tool identifying State X ??

**ELECTRICAL**

ELECTRONICS

COMMUNICATION

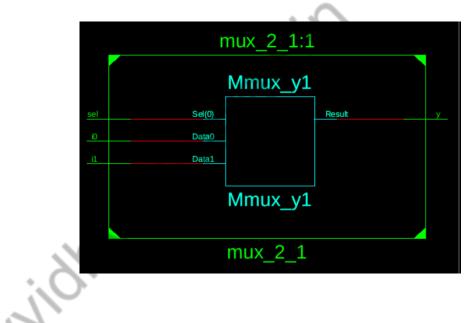

module mux\_2\_1( input sel, input i0, i1, output y); assign y = sel ? i1 : i0; endmodule

**ELECTRICAL**

|       |       |      |      |       | 20.000 ns |

|-------|-------|------|------|-------|-----------|

| Name  | Value | 0 ns | 5 ns | 10 ns | 15 ns     |

| 16 у  | 1     |      |      |       |           |

| 🎼 sel | 1     |      |      |       |           |

| 16 i0 | Θ     |      |      |       |           |

| i1    | 1     |      |      |       |           |

|       |       |      |      |       |           |

COMMUNICATION

**ELECTRONICS**

**INSTRUMENTATION**

Wadharanil

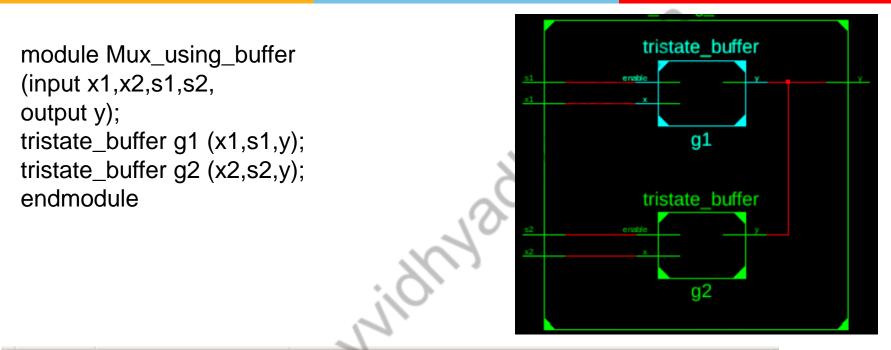

module tristate\_buffer(

input x,

input enable,

output y);

assign y = enable? x : 'bz;

endmodule

**ELECTRICAL**

**ELECTRONICS**

|          |       |      |      |       | 20.000 ns |

|----------|-------|------|------|-------|-----------|

| Name     | Value | 0 ns | 5 ns | 10 ns | 15 ns     |

| 16 у     | 1     |      |      |       |           |

| 16 ×     | 1     |      |      |       |           |

| 🍈 enable | 1     |      |      |       |           |

|          |       |      |      |       |           |

COMMUNICATION

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

**INSTRUMENTATION**

#### **Modeling Gates for Z and X inputs**

|     | _ | _ |   | _ |     |    |   |   |   |   |     |   |

|-----|---|---|---|---|-----|----|---|---|---|---|-----|---|

| AND | 0 | 1 | Ζ | Х |     | OR | 0 | 1 | Z | Х | NOT |   |

| 0   | 0 | 0 | 0 | 0 |     | 0  | 0 | 1 | X | X | 0   | 1 |

| 1   | 0 | 1 | Х | X |     | 1  | 1 | 1 | 1 | 1 | 1   | 0 |

| Z   | 0 | X | X | X |     | Z  | X | 1 | Χ | X | Z   | Х |

| Х   | 0 | X | X | X |     | X  | X | 1 | Х | X | Х   | Χ |

| 1   |   |   |   |   | • 6 |    |   |   |   |   |     |   |

Saulanne

**ELECTRONICS**

**ELECTRICAL**

#### **Modeling XOR/NOR Gate**

COMMUNICATION

| XOR | 0 | 1 | Z   | Х   |                             | XN |

|-----|---|---|-----|-----|-----------------------------|----|

| 0   | 0 | 1 | X   | X   |                             | (  |

| 1   | 1 | 0 | X   | X   | Ś                           | 0  |

| Z   | Х | Х | X   | X   | 3                           | -  |

| Х   | Х | X | X   | X   | $\mathcal{C}_{\mathcal{O}}$ |    |

|     |   |   | . 9 | i'r | 0.                          |    |

|     |   | S |     |     |                             |    |

**ELECTRONICS**

**ELECTRICAL**

|   | <b>XNOR</b> | 0 | 1 | Ζ | Х |

|---|-------------|---|---|---|---|

|   | 0           | 1 | 0 | X | X |

| 2 | 1           | 0 | 1 | X | X |

|   | Z           | X | X | X | X |

|   | Х           | X | X | X | X |

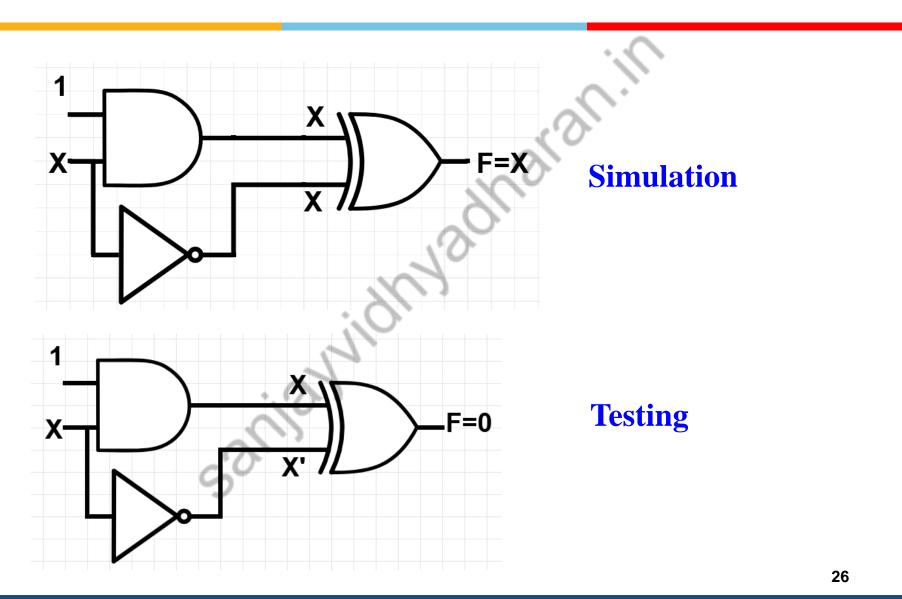

#### **Limitation in Simulation**

**ELECTRICAL**

**ELECTRONICS**

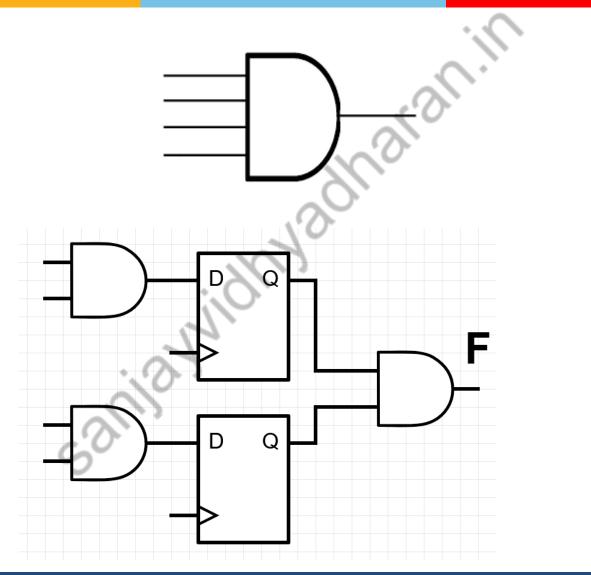

#### **Design for Testing**

**ELECTRICAL**

ELECTRONICS

COMMUNICATION

**INSTRUMENTATION**

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

**INSTRUMENTATION**

COMMUNICATION

#### INSTRUMENTATION

29

**ELECTRONICS**

#### **ELECTRICAL**

## **Algorithms for True-Value Simulation**

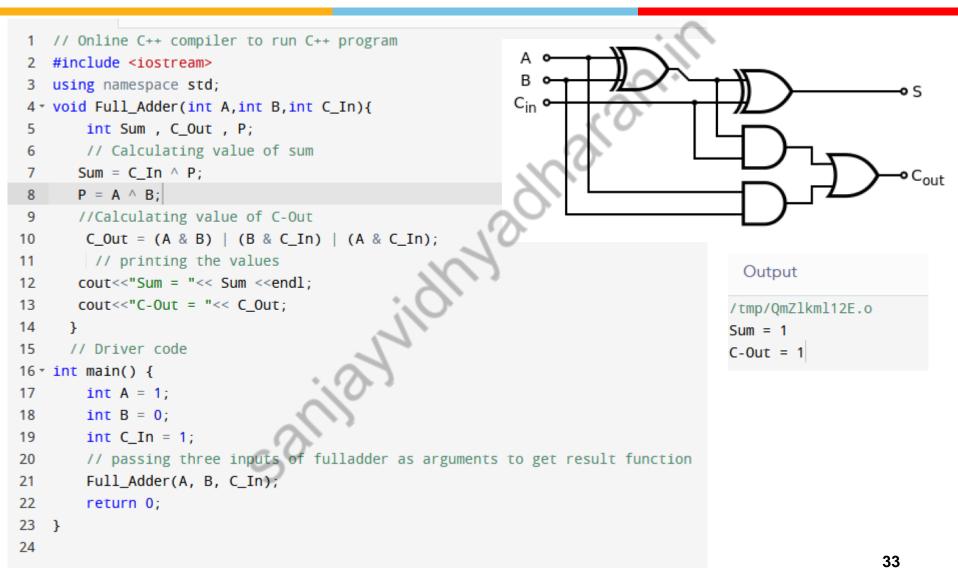

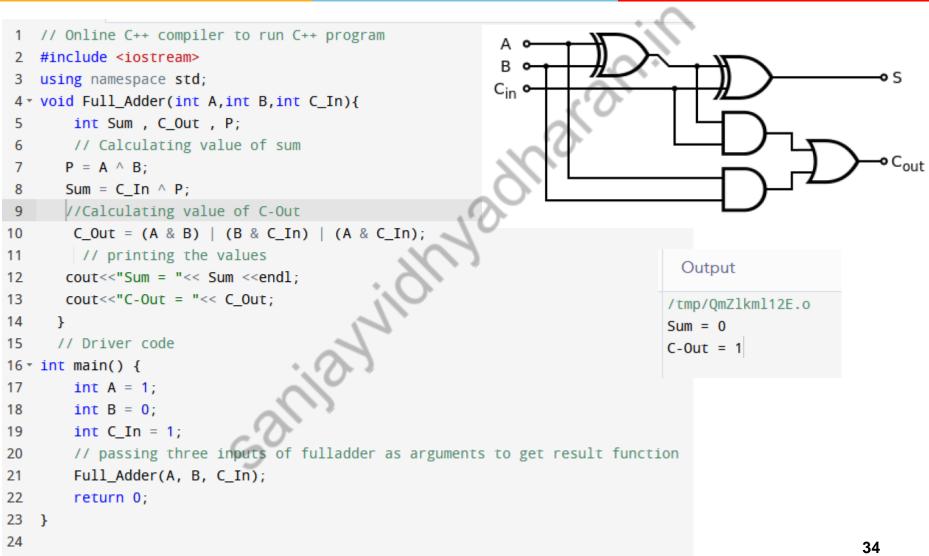

- Step 1: Levelize circuit and produce compiled code

- Step 2: Initialize data variables (flip-flops and other memory)

- Step 3: For each input vector Set primary input variables Repeat until steady-state or maximum iteration-count reached Execute compiled-code Report or save variable values

Normally in an HDL such as VHDL or Verilog

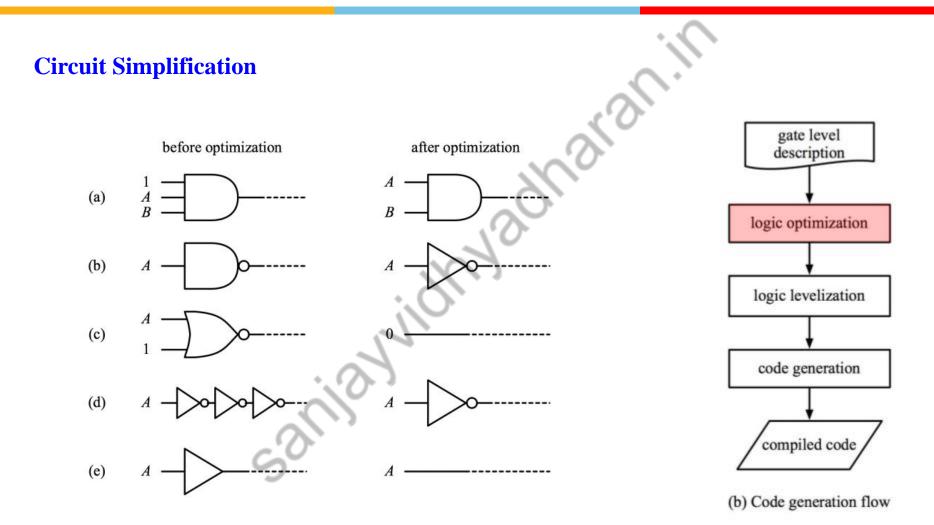

- 1. Circuit Simplification

- 2. Circuit Levelized

- 3. Signals are treated as variables in the code

- 4. For every input vector, the code is repeatedly executed until all variables have attained steady values

- 5. Compiled-code simulators are very effective where two-state (0,1) simulation suffices

- 6. Timing are not modeled in a compiled-code simulator

Video lectures by Professor James Chien-Mo Li

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

**INSTRUMENTATION**

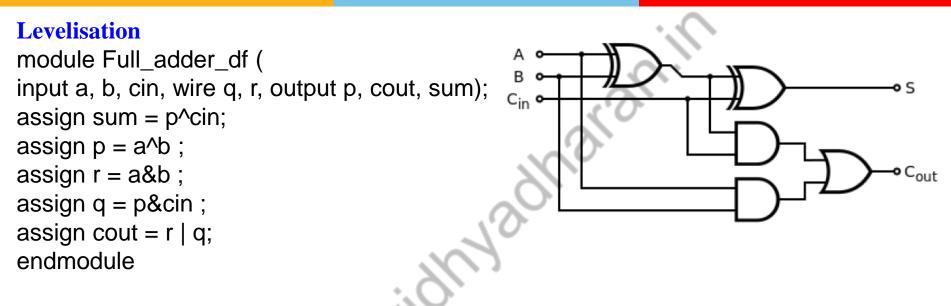

#### Levelisation

#### ELECTRICAL

ELECTRONICS COMMUNICATION

#### Levelisation

COMMUNICATION

**ELECTRONICS**

INSTRUMENTATION

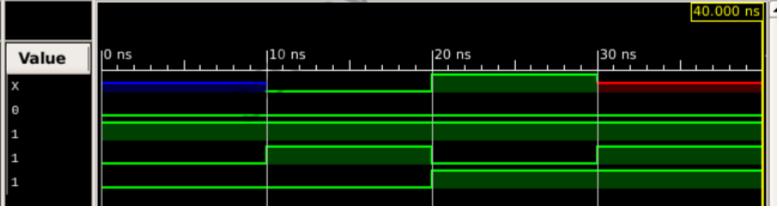

|        |       |      |        | 300.000 H3 |

|--------|-------|------|--------|------------|

| Name   | Value | 0 ns | 100 ns | 200 ns     |

| 16 р   | 1     |      |        |            |

| 🎼 sum  | 1     |      |        |            |

| 퉪 cout | 0     |      |        |            |

|        | 1     |      |        |            |

| 16 b   | Θ     |      |        |            |

| lo cin | Θ     |      |        |            |

|        |       |      |        |            |

**ELECTRICAL**

**ELECTRONICS**

#### COMMUNICATION

#### **INSTRUMENTATION**

Compiled-code simulation: convert gates into codes for evaluation

- Optimization: simplifies logic

- Levelization: sort gates in order (*i.e.* topological sort of graph)

- Code generated: 1.high-level, 2.machine, 3.interpreted

- © Pros

- Simple to implement

- Can speed-up by parallelism

- \* see parallel simulation

- 😕 Cons

ELECTRICAL

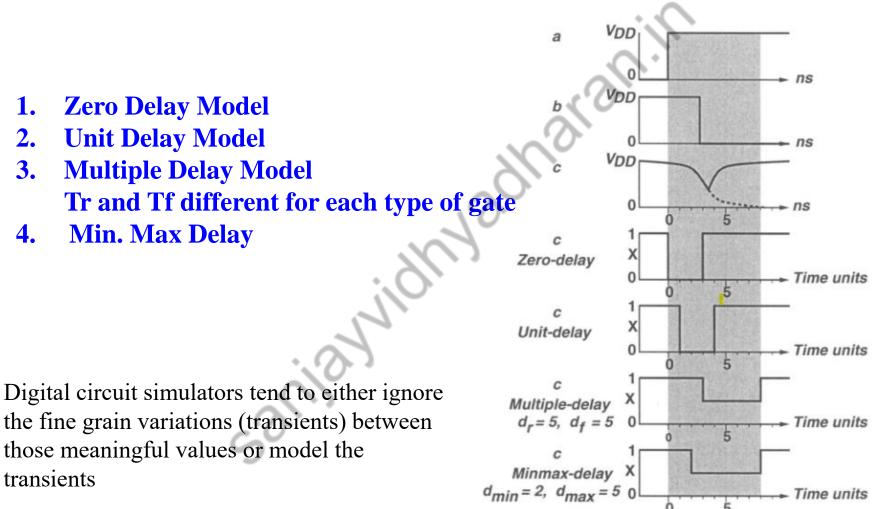

- Only cycle-based accuracy, no timing (zero gate delay)

- Need to evaluate whole circuit even only small portion changed

COMMUNICATION

\* see event-driven simulation

**ELECTRONICS**

\* Zero delay

\* Nominal delay

\* Data structure

#### **Event-driven Faster then CC**

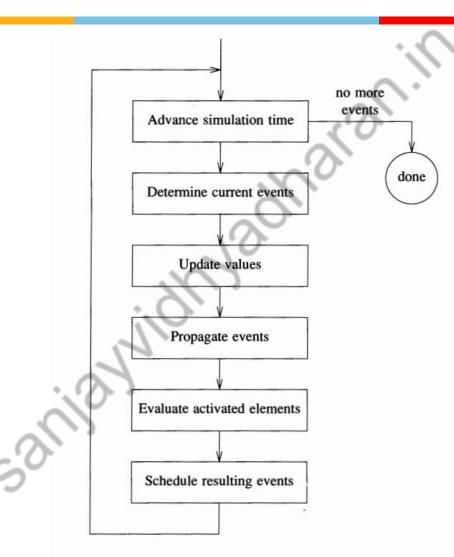

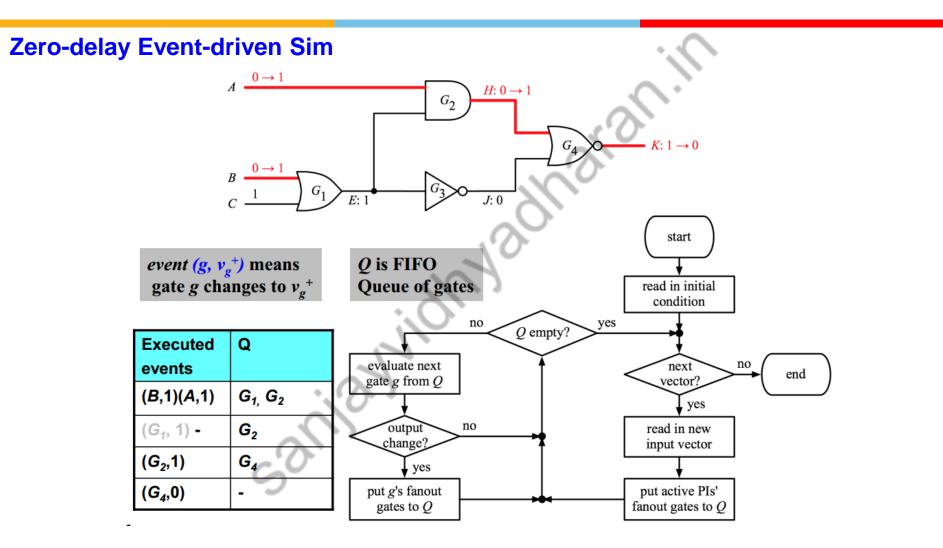

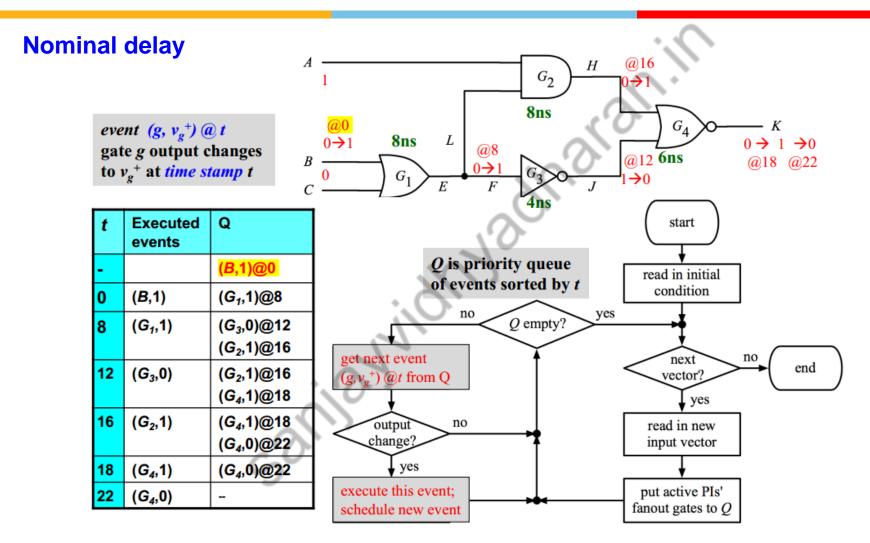

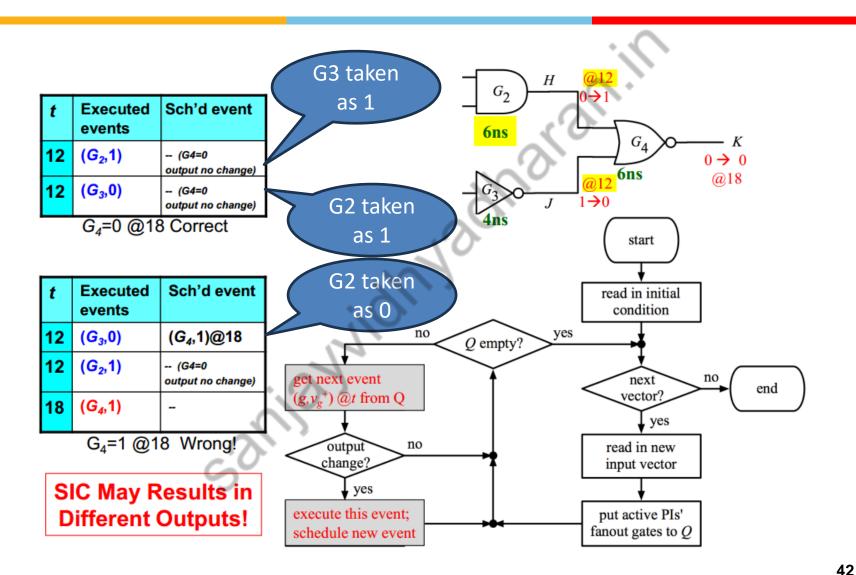

It is based on the recognition that any signal change (event) must have a *cause*, which is also an event. Thus, an event causes new events, which in turn may cause more events. An event-driven simulator follows the path of events.

Gates whose inputs now have events are called *active* and are placed in an *activity list*. The simulation proceeds by removing a gate from the activity list and evaluating it to determine whether its output has an event.

An event-driven simulator only does the necessary amount of work.

For logic

circuits, in which typically very few signals change at a time, this can result in significant savings of computing effort. However, the biggest advantage of this technique is in its ability to simulate any arbitrary delays. This is done by a procedure known as *event scheduling*.

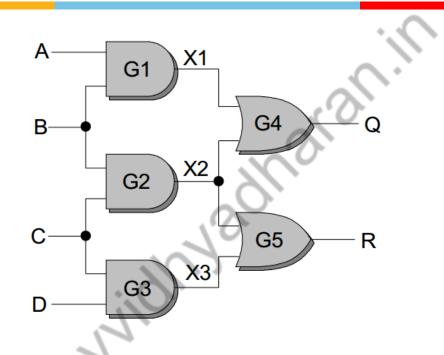

Suppose the circuit is simulated with two consecutive input vectors, (0,0,0,0) and (0,0,0,1). Since A, B, and C have not changed, it is not necessary to simulate gates G1 and G2. Since neither G1 nor G2 have been simulated, it is not necessary to test X1 or X2 for changes. The simulation of G4 can be bypassed without testing X1 or X2.

39

#### ELECTRONICS

**ELECTRICAL**

#### COMMUNICATION

#### **INSTRUMENTATION**

[2]. Video lectures by Professor James Chien-Mo Li

**INSTRUMENTATION**

**ELECTRICAL**

ELECTRONICS

[2]. Video lectures by Professor James Chien-Mo Li

**ELECTRICAL**

ELECTRONICS

COMMUNICATION

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

**INSTRUMENTATION**

#### References

"Essentials of Electronic Testing, for Digital, Memory and Mixed-Signal VLSI Circuits", Michael L. Bushnell and Vishwani D. Agrawal, – Kluwer Academic Publishers (2000).

COMMUNICATION

Video lectures by Professor James Chien-Mo Li Lab. of Dependable Systems Graduate Institute of Electronics Engineering National Taiwan University https://www.youtube.com/watch?v=yfcoKOUV5DM&list=PLvd8d-SyI7hjk\_Ci0zpTqImAtpEjdK5JF&index=1

ELECTRONICS

ELECTRICAL

**INSTRUMENTATION**

**ELECTRONICS**

**ELECTRICAL**