# **Testability of VLSI Lecture 2: Fault Modelling** By Dr. Sanjay Vidhyadharan

ELECTRICAL

**ELECTRONICS**

COMMUNICATION

# **Defects, Errors, and Faults**

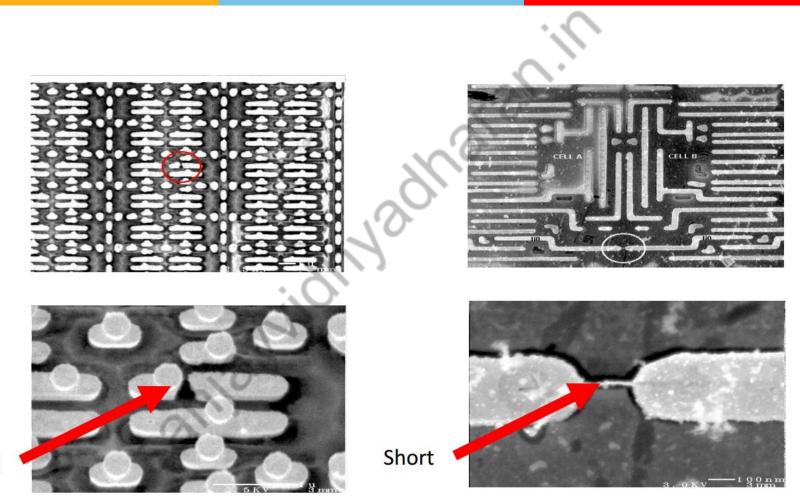

Defect. A defect in an electronic system is the unintended difference between the implemented hardware and its intended design.Example : unwanted wire (short to ground)

1. Process Defects – missing contact windows, parasitic transistors, oxide breakdown, etc.

2. Material Defects – bulk defects (cracks, crystal imperfections), surface impurities, etc.

3. Package Defects – contact degradation, seal leaks, etc

4. Age Defects – dielectric breakdown, electromigration, etc.

*Fault*. A representation of a "defect" at the abstracted function level is called a fault **Example: Stuck to Zero Fault**

*Error.* A wrong output signal produced by a defective system is called an error. An error is an "effect" whose cause is some "defect. Example: output = 0, when a=b=1 for a AND gate

Failure : Deviation from expected behavior Example: computer crash

#### Defect $\rightarrow$ Fault $\rightarrow$ Error $\rightarrow$ Failure

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

#### **Fabrication Faults**

COMMUNICATION

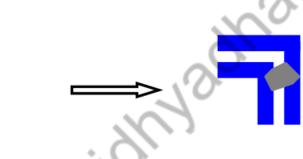

**OPEN**

**ELECTRICAL**

ELECTRONICS

#### **Fabrication Faults**

- Random defects

- Caused by random factors such as particles, scratches, …

- No correlation across wafers, dies

#### • Systematic defects

ELECTRICAL

Caused by deterministic factors such as mask, lithography, …

COMMUNICATION

Strong correlation across wafers, dies

ELECTRONICS

#### **Fault Models**

Why Fault Modelling?

1. Defects are hard to handle

How many possible defects in a circuit ? Way too many Number of faults can be easily calculated in a circuit

2. Fault models makes test automation possible

Automatic test pattern generation (ATPG) generate test patterns Fault simulation Evaluate test quality Automatic diagnosis Locate defects

#### **Fault Models**

**1. Assertion Fault:** An assertion expresses a property of a high-level function in the form: "antecedent consequent," where antecedent and consequent can be simple predicates like "line L takes symbolic value v" or conjunctions of simple predicates.

**2. Behavioural Faults (***Functional* or *High level***):** When the behavior of an electronic system is described in computer-readable form, it is generally written in a programming language (such as C) or some other hardware description language that resembles a programming language.

**3. Structural Faults:** The structure of a circuit may refer to its topology or to physical geometry. Examples of structural faults are single stuck-at faults and bridging faults. **Focus is on manufacturing defects not functional aspect of DUT.**

#### > Please refer to other types of faults in the textbook

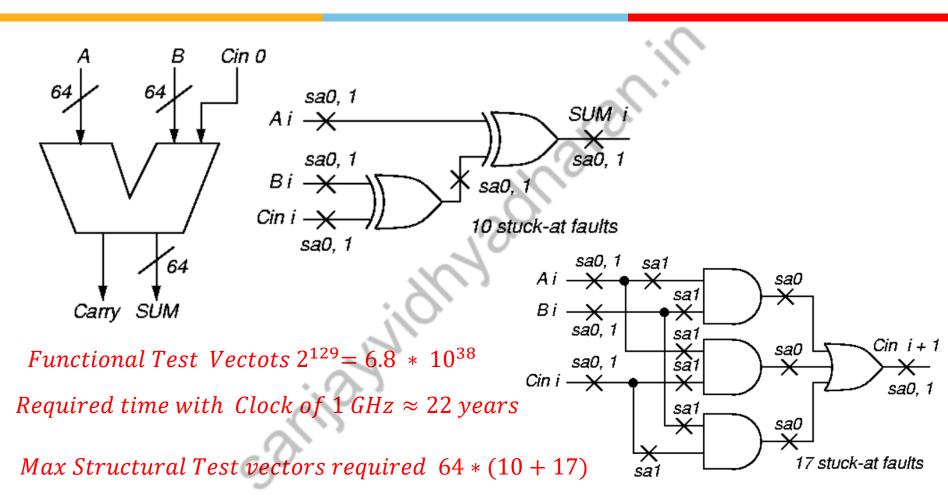

#### **Functional Versus Structural Testing**

Actaul Structural Test vectors required could be smuch lesseras multiple sa faults gets detected with single vector

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

**INSTRUMENTATION**

#### **Common Structural Fault Models**

Single stuck-at faults

Transistor open and short faults

Bridging Faults

Delay faults (transition, path)

Analog faults

ELECTRICAL

> Please refer to other types of faults in the textbook

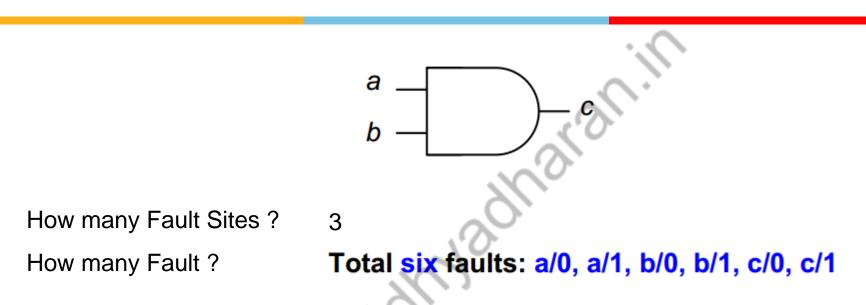

Minimum test length for 100% SSF fault coverage ? 3

**ELECTRONICS**

ELECTRICAL

| Input | Fault-free | Faulty Output Value with SSF |             |             |             |             |             |  |  |  |  |  |

|-------|------------|------------------------------|-------------|-------------|-------------|-------------|-------------|--|--|--|--|--|

| a b   | Output     | <i>a</i> /0                  | <i>a</i> /1 | <i>b</i> /0 | <i>b</i> /1 | <i>c</i> /0 | <i>c</i> /1 |  |  |  |  |  |

| 0 0   | 0          | 0                            | 0           | 0           | 0           | 0           | 1           |  |  |  |  |  |

| 0 1   | 0          | 0                            | 1           | 0           | 0           | 0           | 1           |  |  |  |  |  |

| 11    | 7          | <u>0</u>                     | 1           | <u>0</u>    | 1           | <u>0</u>    | 1           |  |  |  |  |  |

| 10    | 0          | 0                            | 0           | 0           | 1           | 0           | 1           |  |  |  |  |  |

COMMUNICATION

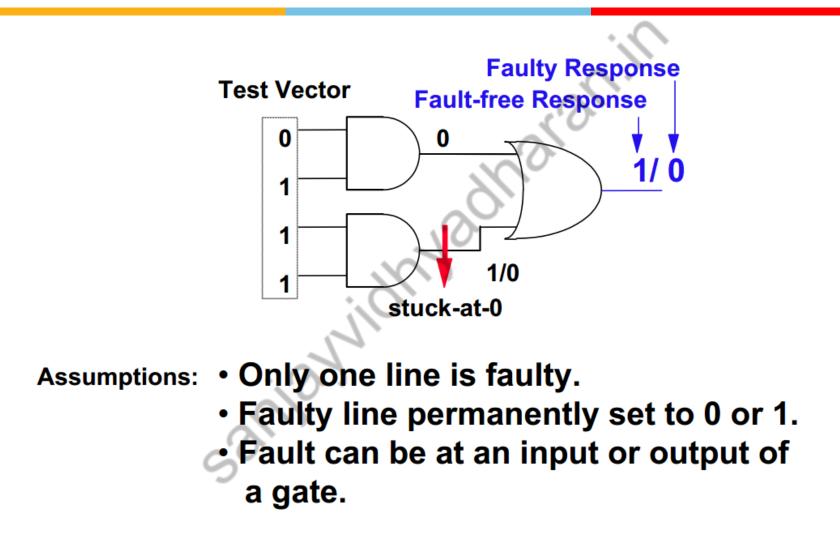

#### Properties of single stuck-at fault

• Only one line is faulty

ELECTRICAL

- The faulty line is permanently set to 0 or 1

- The fault can be at an input or output of a gate

COMMUNICATION

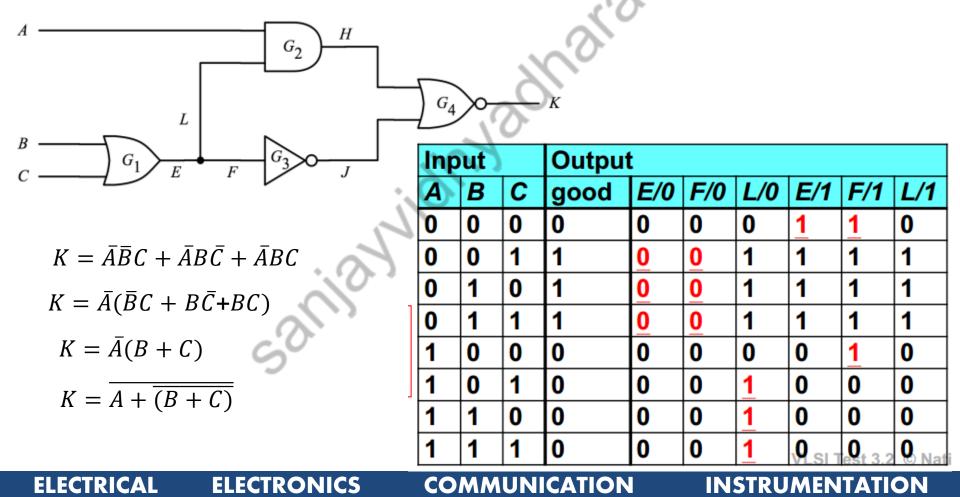

XOR circuit has 12 fault sites (•) and 24 single stuck-at faults

**ELECTRONICS**

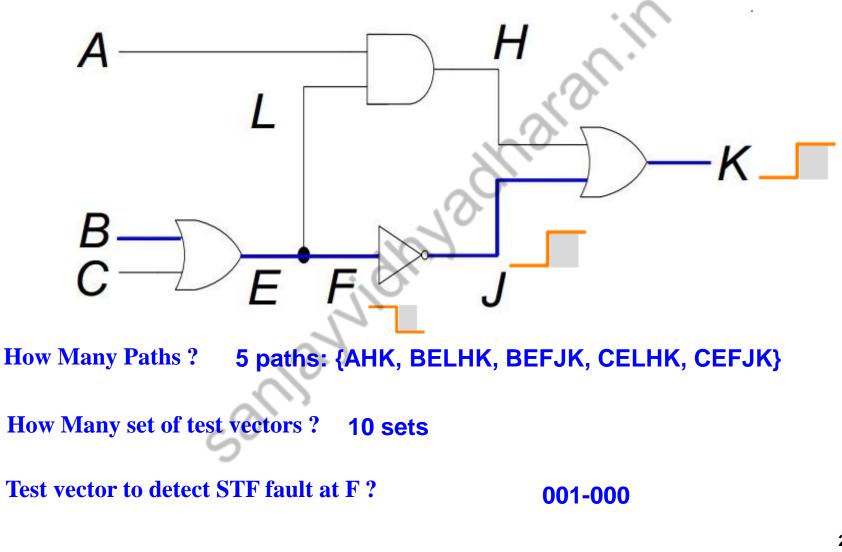

SSF on fanout wires *not equivalent* to SSF on fanout branches Faults on stems and faults on branches are **counted separately** Example: *E* is fanout stem; *L*,*F* are fanout branches

- Several stuck-at faults occur at the same time

- Important in high density circuits

ELECTRONICS

ELECTRICAL

If there are N possible fault locations in a circuit Total possibilities is  $3^N$  as a line be be sa0, sa1 or good One possibility of circuit being good 2N possibilities of single fault Possibilities of multiple fault  $3^N$  - 1- 2N

**MSF Not Considered in Practice**

COMMUNICATION

- How effective is SSF test sets for multiple stuck-at faults?

- 14-input ALU 74LS181 circuit

- 400 single stuck-at faults

- 79,600 double stuck-at faults

- 16 different test sets

ELECTRONICS

**ELECTRICAL**

|              |    |    |    |    |      |    |     |    |    |    |    |    |    |     |     | N   |

|--------------|----|----|----|----|------|----|-----|----|----|----|----|----|----|-----|-----|-----|

| Test Set     | 1  | 2  | 3  | 4  | 5    | 6  | 176 | 8  | 9  | 10 | 11 | 12 | 13 | 14  | 15  | 16  |

| Length       | 12 | 12 | 12 | 12 | 12   | 12 | 12  | 14 | 14 | 14 | 14 | 17 | 35 | 124 | 135 | 352 |

| Undetected   | 9  | 8  | 1  | 9  | 28   | 13 | 19  | 4  | 14 | 11 | 3  | 30 | 0  | 0   | 0   | 0   |

| Double-      |    |    |    |    | •. ( |    |     |    |    |    |    |    |    |     |     |     |

| stuck faults |    |    |    |    | 1    |    |     |    |    |    |    |    |    |     |     |     |

- Observation #1: Some shorter tests are better than longer tests

- Smart test generation/selection is important

- Observation #2: Most double SA faults are detected by SSF test sets

COMMUNICATION

Hughes, J.L.A., and E.J. McCluskey, "An Analysis of the Multiple Fault Detection Capabilities of Single Stuck-at Fault Test Sets," Proc. of Int'l Test Conf, Philadelphia, PA, Oct. 1984, pp. 52–58.

INSTRUMENTATION

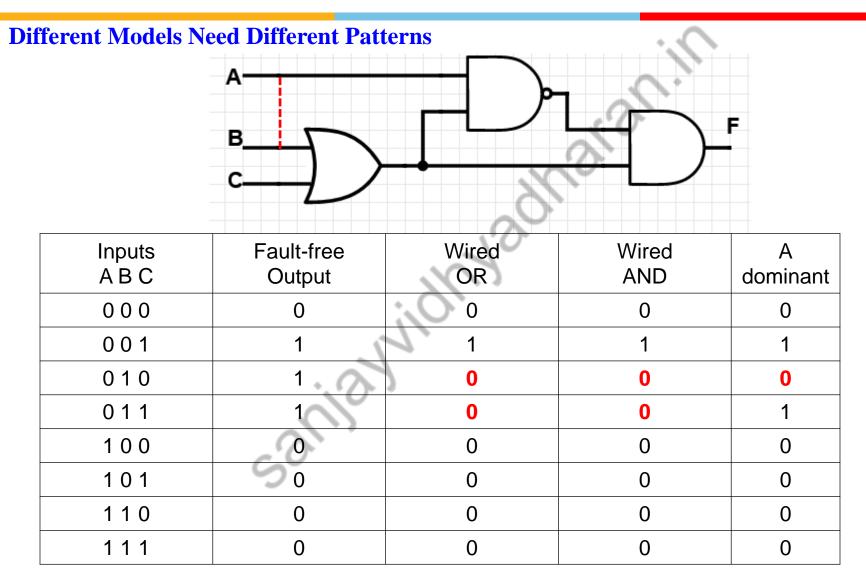

Different

Algorithms

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

15

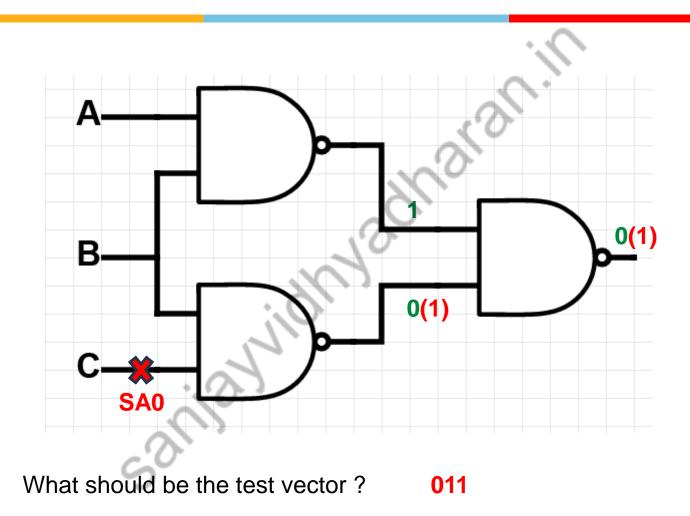

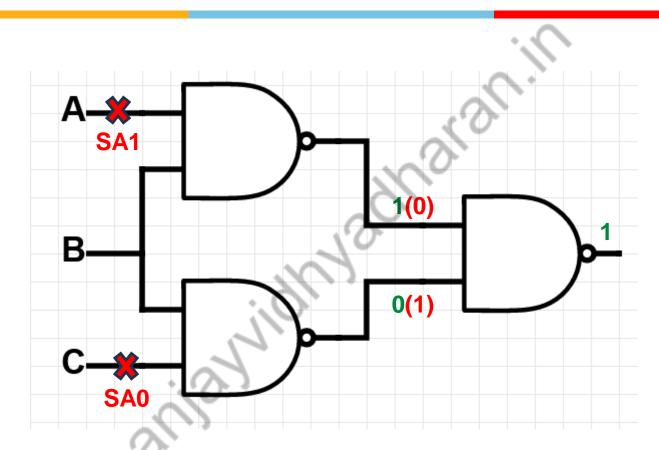

What should be the test vector ? **011 SA1 is Masking SA0**

**ELECTRONICS**

**ELECTRICAL**

What should be the test vector ? 010 detects the MSF {c SA0, a SA1}.

COMMUNICATION

#### 16

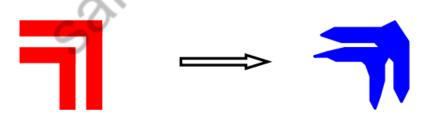

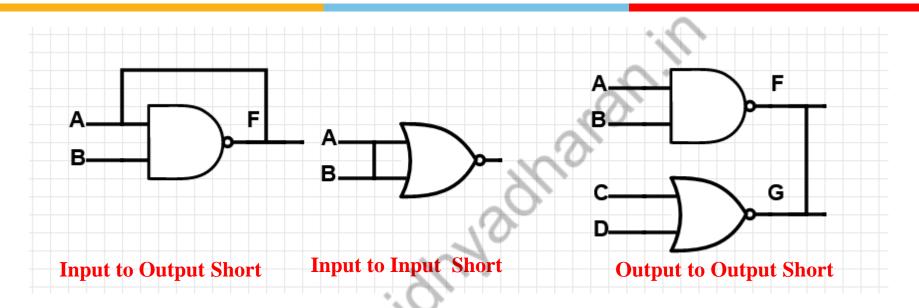

- Improper masking or etching

- Loose or excess bare wires

- Defective printed circuit boards

**ELECTRONICS**

Shorting of pins of a chip

**ELECTRICAL**

Test Vectors for Input and Output Stuck-at Faults cover Input-to-Output Shorts

COMMUNICATION

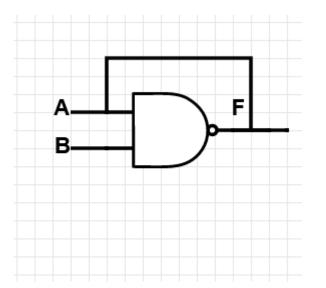

#### **Input to Output Short**

**ELECTRICAL**

**ELECTRONICS**

- 1. Can cause oscillations

- 2. Creates Memory

COMMUNICATION

**Test Vectors for Input and Output Stuck-at Faults cover Input-to-Output Shorts**

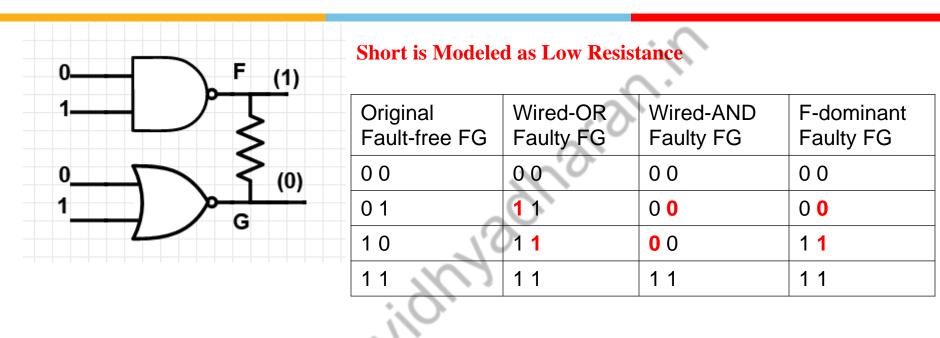

If F,G = 0,0 can be detected as F s-a-0 If F,G = 1,1 can be detected as G s-a-1

**ELECTRONICS**

ELECTRICAL

High Resistance Bridges do not affect the logic value, and hence are undetectable by a static logic test.

COMMUNICATION

19

**ELECTRICAL**

| Table 1. Results of 74LS181 simulations. |       |       |       |       |       |       |       |  |  |  |

|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Test Set                                 | Bry2  | Bry6  | Goel  | Hugh  | Krish | McC4  | Micz2 |  |  |  |

| Test Length                              | 14    | 12    | 35    | 135   | 12    | 124   | 17    |  |  |  |

| Number of<br>missed<br>AND faults        | 24    | 28    | 4     | 00    | 33    | 0     | 46    |  |  |  |

| Number of<br>missed<br>OR faults         | 35    | 44    | 5     | 0     | 66    | 1     | 18    |  |  |  |

| Coverage<br>of AND<br>faults (%)         | 99.18 | 99.04 | 99.86 | 100.0 | 98.87 | 100.0 | 98.43 |  |  |  |

| Coverage<br>of OR<br>faults (%)          | 98.79 | 98.48 | 99.83 | 100.0 | 97.72 | 99.97 | 99.38 |  |  |  |

| Total number of each type of fault 2926  |       |       |       |       |       |       |       |  |  |  |

[Millman 88] S.D. Millman, McCluskey, "Detecting bridging faults with stuck-at test sets," ITC 1988.

21

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

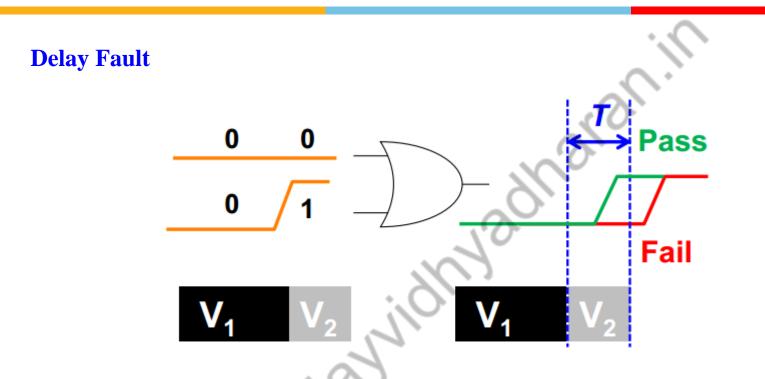

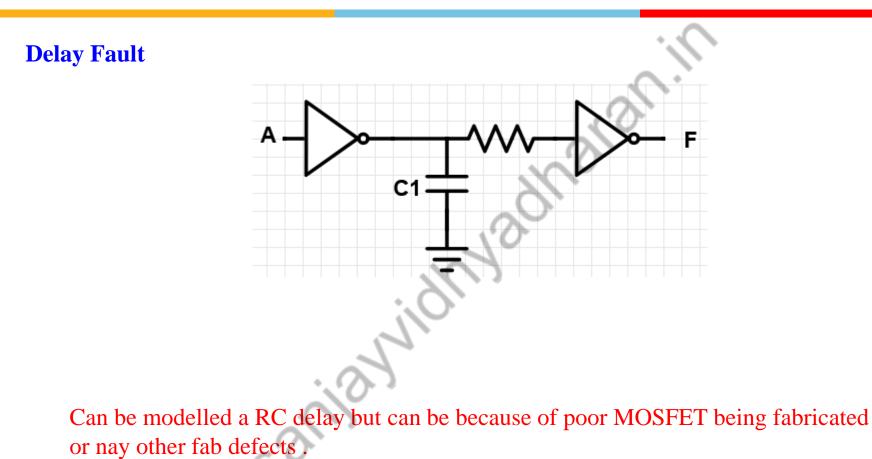

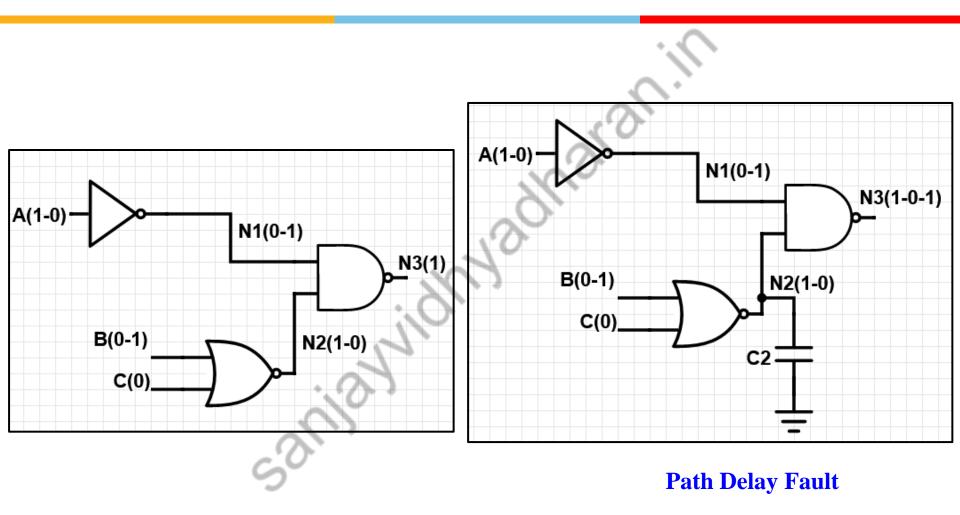

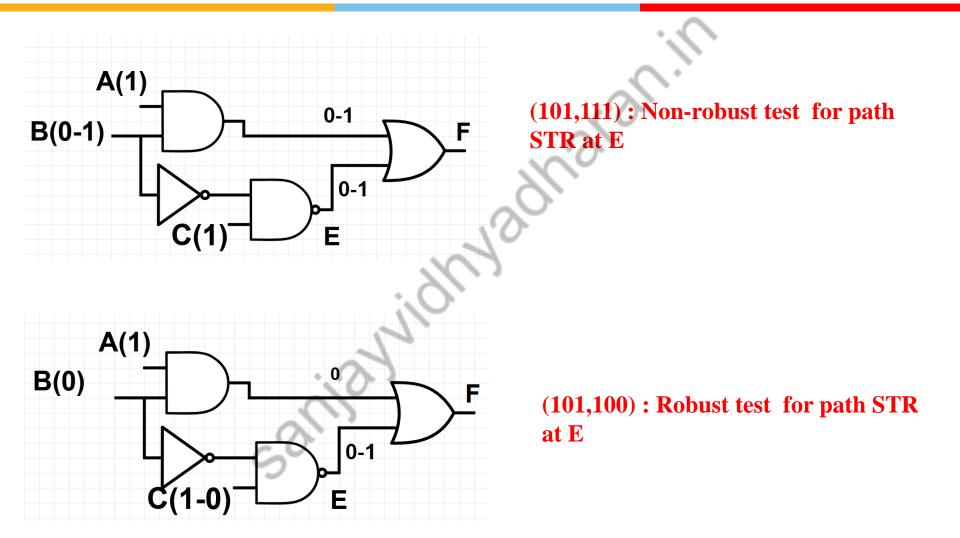

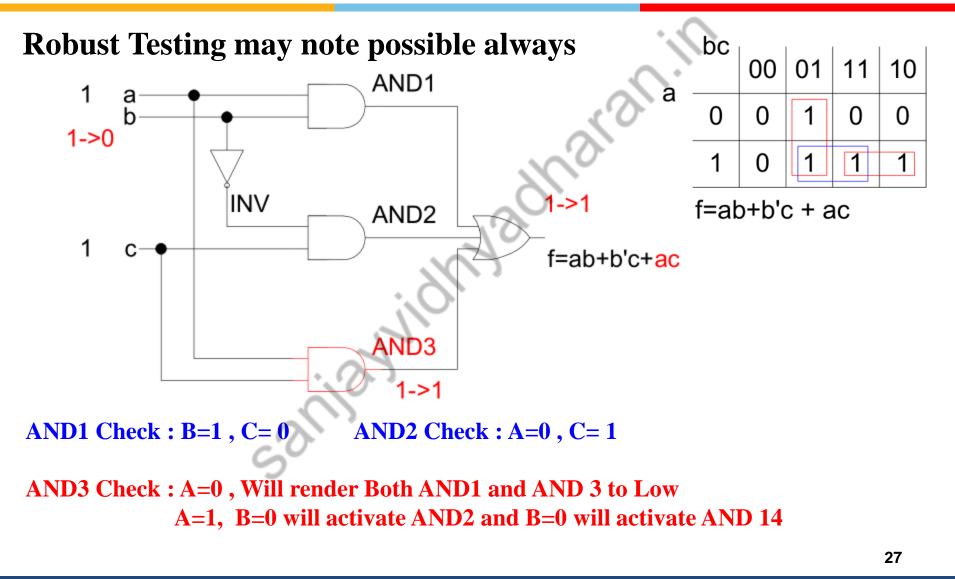

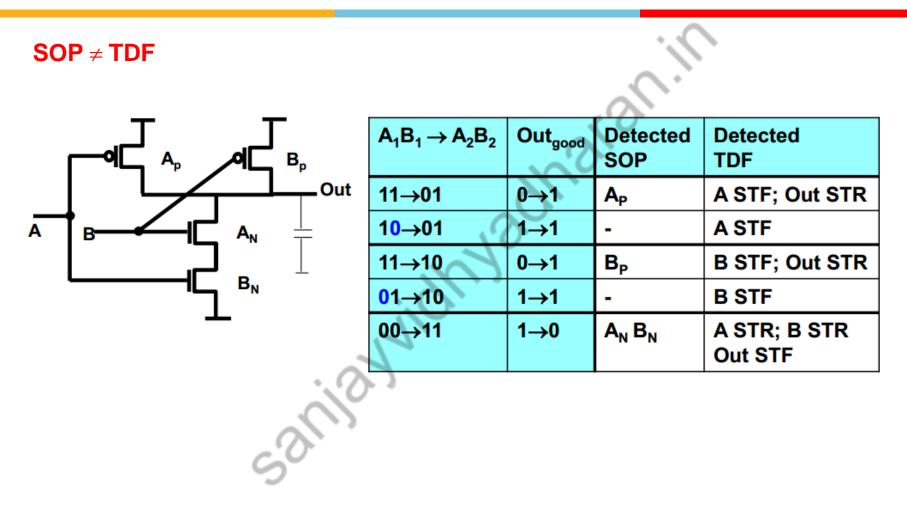

Slow to rise (**STR**), slow to fall Transition (**STF**), faults due to Vt Variation, Doing Variation, Improper contacts etc

No fault detected at static and low frequency operation but glitches can be there at high operating frequencies and cause errors in sequential circuits

COMMUNICATION

**Delay Faults requires two test vectors**

**ELECTRONICS**

ELECTRICAL

**Delay Faults requires two test vectors**

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

26

ELECTRICAL EL

ELECTRONICS

COMMUNICATION

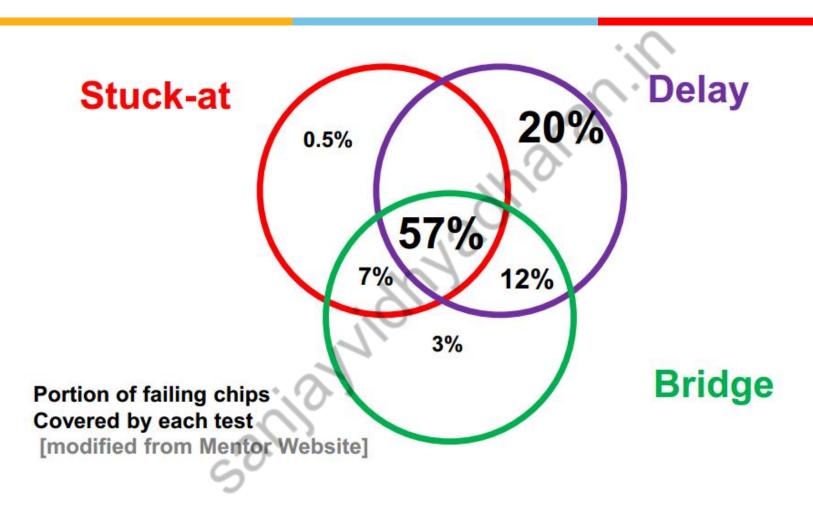

#### **Experimental Results**

[2]/ Video lectures by Professor James Chien-Mo Li

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

#### **Fault Models**

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

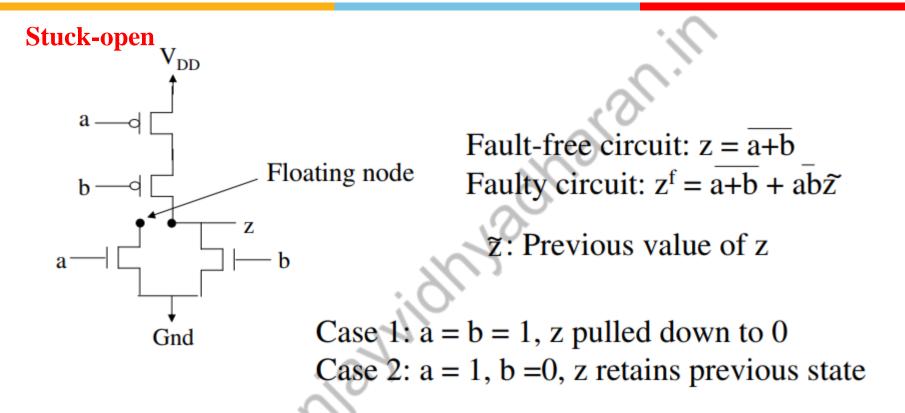

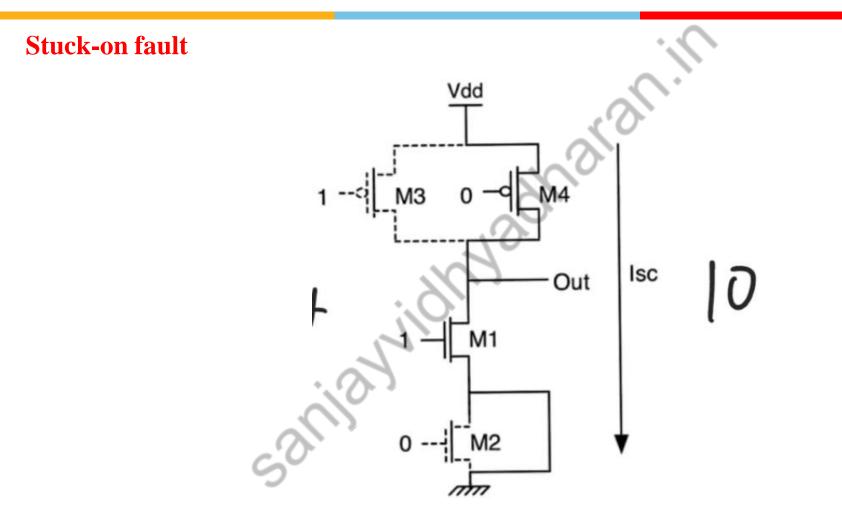

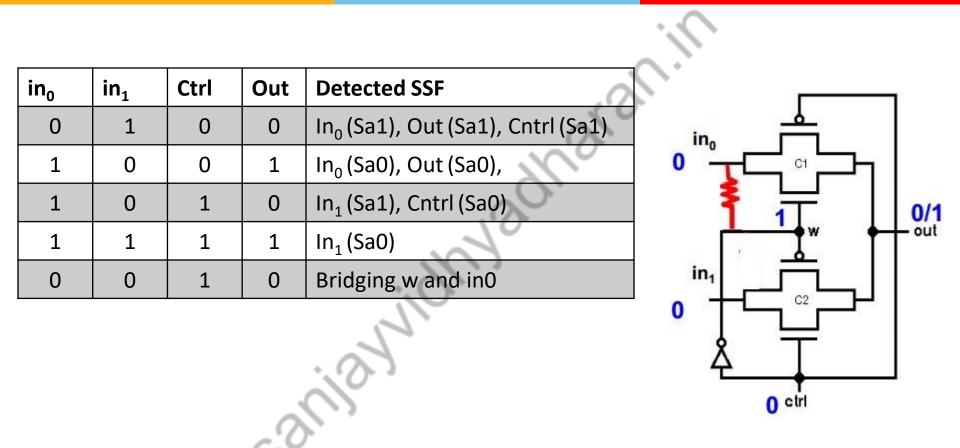

Two types of Transistor Faults

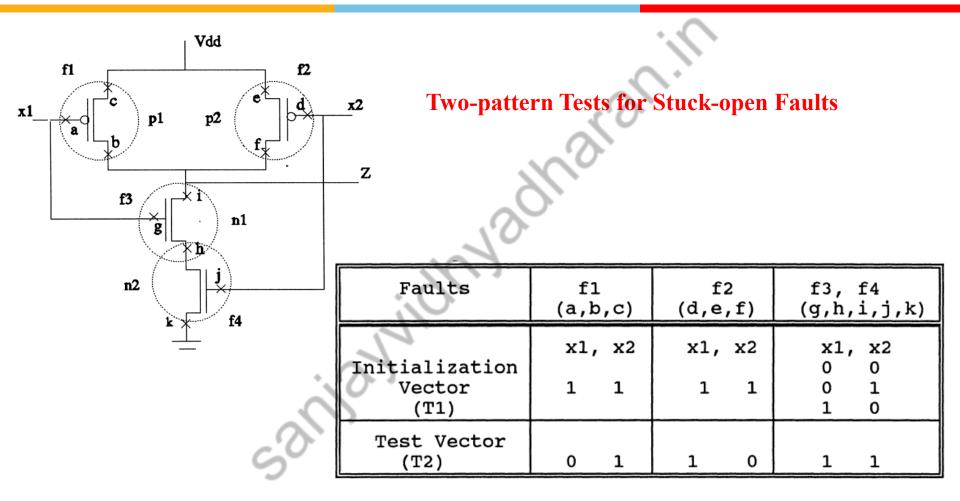

- Stuck-open -- a single transistor is permanently stuck in the open state irrespective of its gate voltage. Single Stuck-open detection requires two test patterns

- Stuck-short -- a single transistor is permanently shorted irrespective of its gate voltage. Detection by quiescent I<sub>DD</sub>

http://ece-research.unm.edu/jimp/vlsi\_test/slides/html/faults2.html

A test for a stuck-open fault requires two patterns  $\{ab = 00, ab = 10\}$

Automation available to optimize Stuck-at and Stuk-open Fault

**ELECTRICAL**

32

ELECTRONICS COMMUNICATION

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

[2]. Video lectures by Professor James Chien-Mo Li

**ELECTRONICS**

**ELECTRICAL**

COMMUNICATION

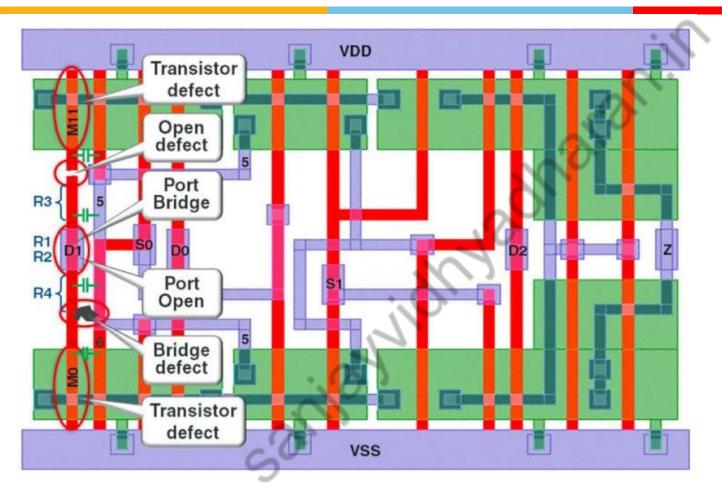

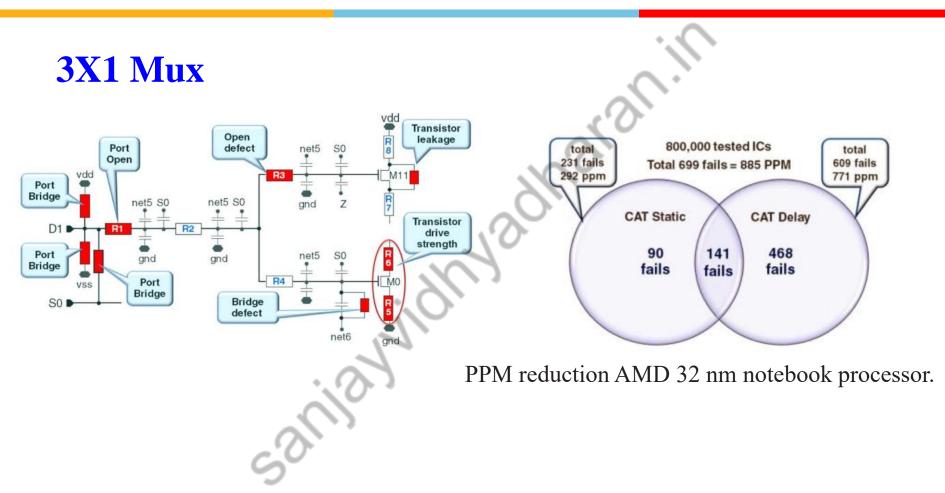

#### **Cell Aware Fault Model**

**ELECTRONICS**

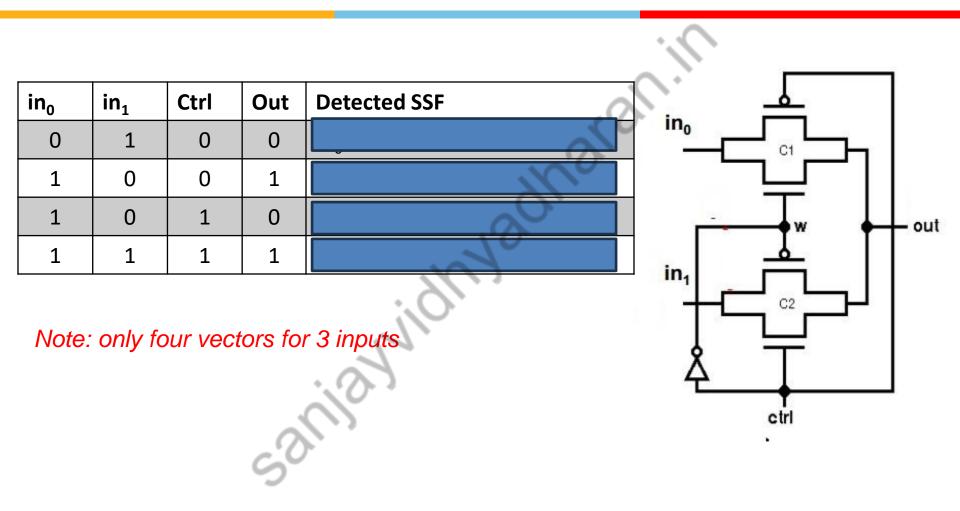

**3X1 Mux**

Hapke, Friedrich & Redemund, Wilfried & Glowatz, Andreas & Rajski, Janusz & Reese, M. & Hustava, Marek & Keim, Martin & Schlöffel, Jürgen & Fast, Anja. (2014). Cell-Aware Test. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on. 33. 1396-1409. 10.1109/TCAD.2014.2323216.

COMMUNICATION

INSTRUMENTATION

**ELECTRICAL**

#### **Cell Aware Fault Model**

Hapke, Friedrich & Redemund, Wilfried & Glowatz, Andreas & Rajski, Janusz & Reese, M. & Hustava, Marek & Keim, Martin & Schlöffel, Jürgen & Fast, Anja. (2014). Cell-Aware Test. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on. 33. 1396-1409. 10.1109/TCAD.2014.2323216.

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

37

## **Cell Aware Fault Model**

Hapke, Friedrich & Redemund, Wilfried & Glowatz, Andreas & Rajski, Janusz & Reese, M. & Hustava, Marek & Keim, Martin & Schlöffel, Jürgen & Fast, Anja. (2014). Cell-Aware Test. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on. 33. 1396-1409. 10.1109/TCAD.2014.2323216.

#### ELECTRONICS COMMUNICATION

**ELECTRICAL**

## References

"Essentials of Electronic Testing, for Digital, Memory and Mixed-Signal VLSI Circuits", Michael L. Bushnell and Vishwani D. Agrawal, – Kluwer Academic Publishers (2000).

2. Video lectures by Professor James Chien-Mo Li Lab. of Dependable Systems Graduate Institute of Electronics Engineering National Taiwan University https://www.youtube.com/watch?v=yfcoKOUV5DM&list=PLvd8d-SyI7hjk\_Ci0zpTqImAtpEjdK5JF&index=1

3. http://ece-research.unm.edu/jimp/vlsi\_test/slides/html/faults2.html

**INSTRUMENTATION**

**ELECTRONICS**

**ELECTRICAL**

COMMUNICATION