# Microprocessor Programming and Interfacing

**Lecture-1: Introduction**

Dr. Sanjay Vidhyadharan

## **About the Course**

- 8086 Architecture

- 8086 Addressing modes

- 8086 Instructions sets.

- Concept of Interrupts.

- Memory Interfacing.

- Programmable peripheral devices.

### **Text Books**

#### **Text Book:**

Barry B Brey, The Intel Microprocessors .Pearson, Eight Ed. 2009.

#### **Reference Book:**

Douglas V Hall, Microprocessor and Interfacing, TMH, Second Edition.

# Introduction to Microprocessors

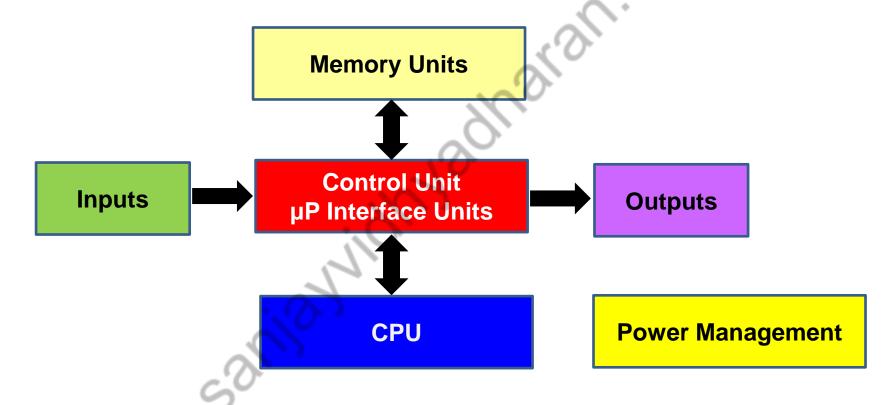

#### **Basic Block Diagram of a Computer**

# Introduction to Microprocessors

#### First Gen 1971 INTEL 4004

4-bit μP.

108 KHz.

Represent signed numbers in the range -8 to +7

#### Second Gen 1972 INTEL 8008

8-bit µP.

500 KHz.

Represent signed numbers in the range -128 to +127

Based on NMOS technology

#### Third Gen Intel 8080

8-bit µP.

2 MHz.

#### Third Gen INTEL 8085

8-bit µP.

3 MHz.

8-bit data bus and 16-bit address bus

5 V compatible with TTL

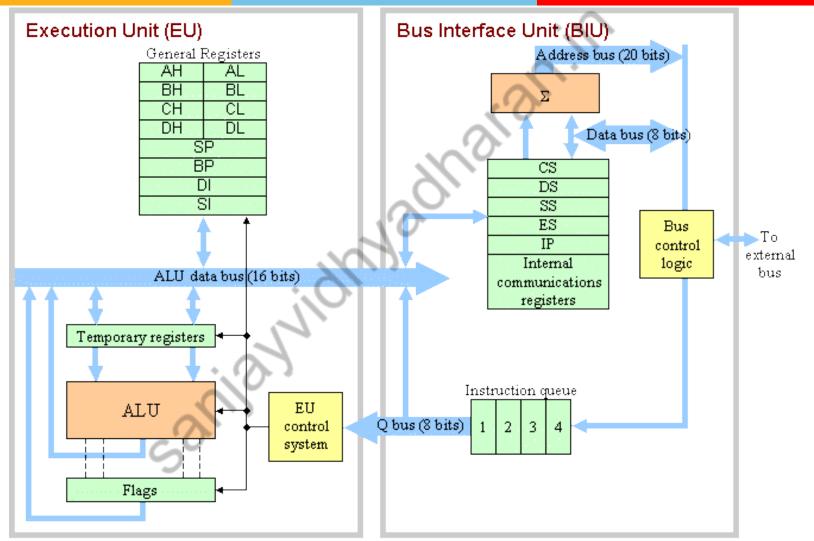

#### Third Gen Intel 8086 (1978)

16-bit µP.

4.77 MHz, 8 MHz and 10 MHz, depending on the version

16-bit data bus and 20-bit address bus

1 MB of memory

Range of -32,768 to +32,767

**CMOS Technology**

#### Fourth Gen

32-bit µP. 80386 range ±2×109

32-bit µP Pentium 4. 1.5 GHz Year 2000

#### Fifth Gen

64-bit µP. INTEL CORE 2 Year 2000

64-bit μP. INTEL i7 1.3-3.5 GHz

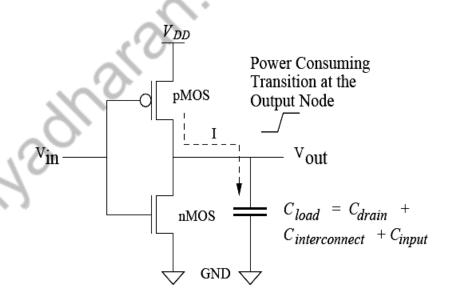

## **Advantages of CMOS Scaling**

Faster

Lower Power

Higher packing density

## **Limitations of CMOS Scaling**

High Power

```

Increase in Freq due to improvement in:

Technology + Architecture

Higher Packing Density due to improvement in:

Technology + Routing Algo

```

- Low Noise Margins

- V<sub>DD</sub> reduced to keep Electrical Field Constant

- High Static Currents

# **Limitations of CMOS Scaling**