# Analog IC Design : 2022-23 Lecture 11 Operational Amplifiers

# By Dr. Sanjay Vidhyadharan

ELECTRICAL ELECTRONICS

COMMUNICATION

**INSTRUMENTATION**

## **Operational Amplifiers**

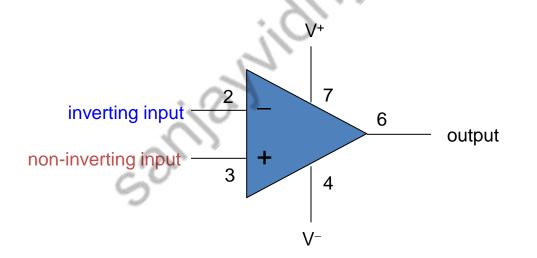

Op-amps (amplifiers/buffers in general) are drawn as a triangle in a circuit schematic There are two inputs inverting and non-inverting And one output Also power connections (note no explicit ground)

COMMUNICATION

**ELECTRONICS**

10/22/2022

ELECTRICAL

# **The Ideal Operational Amplifiers**

- Infinite voltage gain

- a voltage difference at the two inputs is magnified infinitely

- in truth, something like 200,000

- means difference between + terminal and terminal is amplified by 200,000!

- Infinite input impedance

- no current flows into inputs

- in truth, about  $10^{12} \Omega$  for FET input op-amps

- Zero output impedance

- rock-solid independent of load

- roughly true up to current maximum (usually 5–25 mA)

- Infinitely fast (infinite bandwidth)

- in truth, limited to few MHz range

- slew rate limited to 0.5–20 V/ $\mu$ s

10/22/2022

# **Op-amp without feedback**

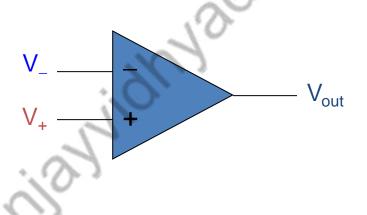

• The internal op-amp formula is:

ELECTRONICS

$V_{out} = gain \times (V_+ - V_-)$

- So if  $V_{+}$  is greater than  $V_{-}$ , the output goes positive

- If  $V_{-}$  is greater than  $V_{+}$ , the output goes negative

• A gain of 200,000 makes this device (as illustrated here) practically useless

COMMUNICATION

10/22/2022

ELECTRICAL

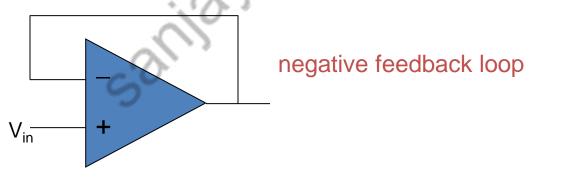

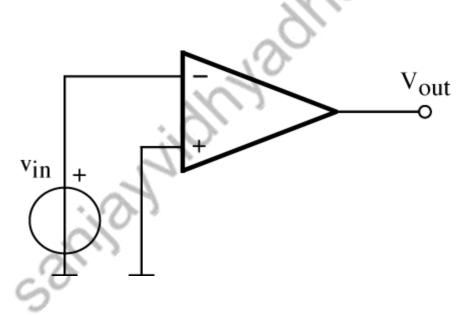

# **Negative feedback**

- Infinite gain would be useless except in the self-regulated negative feedback regime

- negative feedback seems bad, and positive good—but in electronics positive feedback means runaway or oscillation, and negative feedback leads to stability

- Imagine hooking the output to the inverting terminal:

- If the output is less than  $V_{in}$ , it shoots positive

ELECTRONICS

10/22/2022

ELECTRICAL

- If the output is greater than V<sub>in</sub>, it shoots negative

- result is that output quickly forces itself to be exactly  $V_{in}$

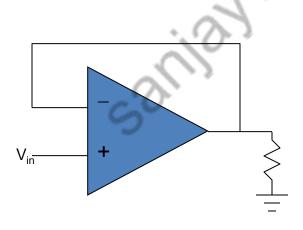

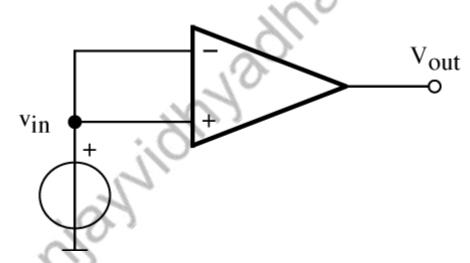

# **Negative feedback**

- Even if we load the output (which as pictured wants to drag the output to ground)...

- the op-amp will do everything it can within its current limitations to drive the output until the inverting input reaches  $V_{in}$

- negative feedback makes it self-correcting

- in this case, the op-amp drives (or pulls, if  $V_{in}$  is negative) a current through the load until the output equals  $V_{in}$

- so what we have here is a buffer: can apply  $V_{in}$  to a load without burdening the source of  $V_{in}$  with *any* current!

COMMUNICATION

ELECTRONICS

10/22/2022

ELECTRICAL

Important note: op-amp output terminal sources/sinks current at will: not like inputs that have no current flow

INSTRUMENTATION

# **Op-Amp "Golden Rules"**

- When an op-amp is configured in *any* negativefeedback arrangement, it will obey the following two rules:

- The inputs to the op-amp draw or source no current (true whether negative feedback or not)

- The op-amp output will do whatever it can (within its limitations) to make the voltage difference between the two inputs zero

COMMUNICATION

10/22/2022

ELECTRICAL

ELECTRONICS

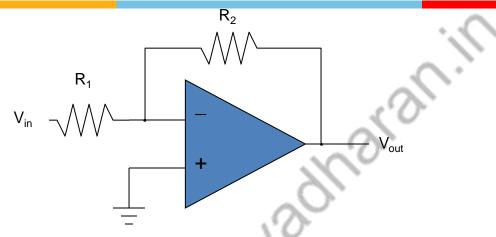

# **Inverting amplifier**

- Applying the rules:

terminal at "virtual ground"

- so current through  $R_1$  is  $I_f = V_{in}/R_1$

- Current does not flow into op-amp (one of our rules)

- so the current through  $R_1$  must go through  $R_2$

- voltage drop across  $R_2$  is then  $I_f R_2 = V_{in} \times (R_2/R_1)$

- So  $V_{out} = 0 V_{in} \times (R_2/R_1) = -V_{in} \times (R_2/R_1)$

- Thus we amplify  $V_{in}$  by factor  $-\frac{R_2}{R_1}$

- negative sign earns title "inverting" amplifier

- Current is *drawn into* op-amp output terminal

10/22/2022

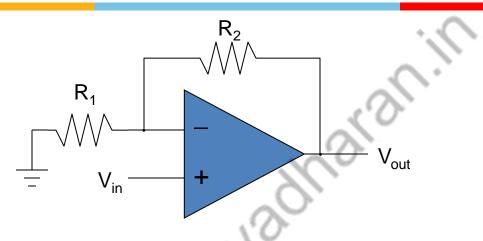

# **Non-inverting Amplifier**

- Now neg. terminal held at V<sub>in</sub>

- so current through  $R_1$  is  $I_f = V_{in}/R_1$  (to left, into ground)

- This current cannot come from op-amp input

- so comes through  $R_2$  (delivered from op-amp output)

- voltage drop across  $R_2$  is  $I_f R_2 = V_{in} \times (R_2/R_1)$

- so that output is higher than neg. input terminal by  $V_{in} \times (R_2/R_1)$

- $V_{out} = V_{in} + V_{in} \times (R_2/R_1) = V_{in} \times (1 + R_2/R_1)$

- thus gain is  $(1 + R_2/R_1)$ , and is positive

- Current is sourced from op-amp output in this example

COMMUNICATION

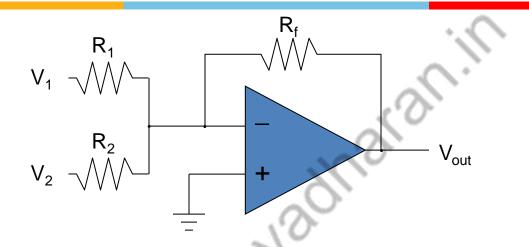

# **Summing Amplifier**

- Much like the inverting amplifier, but with two input voltages

- inverting input still held at virtual ground

- $-I_1$  and  $I_2$  are added together to run through  $R_f$

- so we get the (inverted) sum:  $V_{out} = -R_f \times (V_1/R_1 + V_2/R_2)$

- if  $R_2 = R_1$ , we get a sum proportional to  $(V_1 + V_2)$

- Can have any number of summing inputs

- we'll make our D/A converter this way

10/22/2022

COMMUNICATION

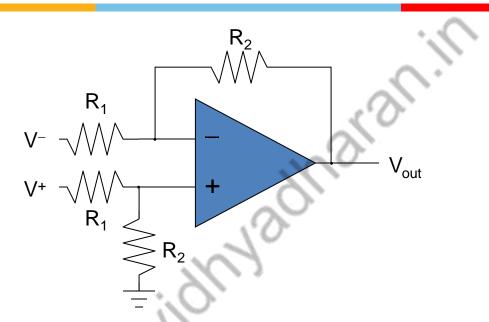

# **Differencing Amplifier**

• The non-inverting input is a simple voltage divider:

$$- V_{\rm node} = V^+ R_2 / (R_1 + R_2)$$

• So

$$I_{\rm f} = (V^- - V_{\rm node})/R_1$$

$$- V_{\text{out}} = V_{\text{node}} - I_f R_2 = V^+ (1 + R_2/R_1)(R_2/(R_1 + R_2)) - V^-(R_2/R_1)$$

- so

$$V_{\text{out}} = (R_2/R_1)(V^+ - V^-)$$

therefore we difference V<sup>+</sup> and V<sup>-</sup>

10/22/2022

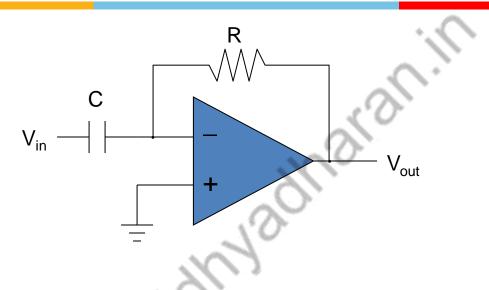

# **Differentiator** (high-pass)

- For a capacitor, Q = CV, so  $I_{cap} = dQ/dt = C \cdot dV/dt$

- Thus  $V_{out} = -I_{cap}R = -RC \cdot dV/dt$

- So we have a differentiator, or high-pass filter

- if signal is  $V_0 \sin \omega t$ ,  $V_{out} = -V_0 RC \omega \cos \omega t$

- the  $\omega$ -dependence means higher frequencies amplified more

10/22/2022

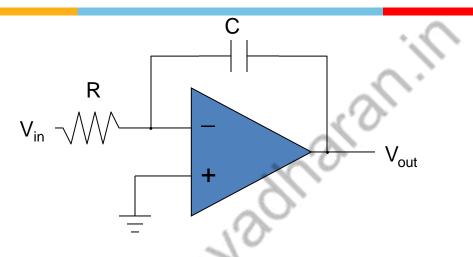

## **Low-pass filter (integrator)**

•

$$I_f = V_{in}/R$$

, so  $C \cdot dV_{cap}/dt = V_{in}/R$

and since left side of capacitor is at virtual ground:

$$-dV_{out}/dt = V_{in}/RC$$

- so  $V_{out} = -\frac{1}{RC} \int V_{in} dt$

and therefore we have an integrator (low pass)

10/22/2022

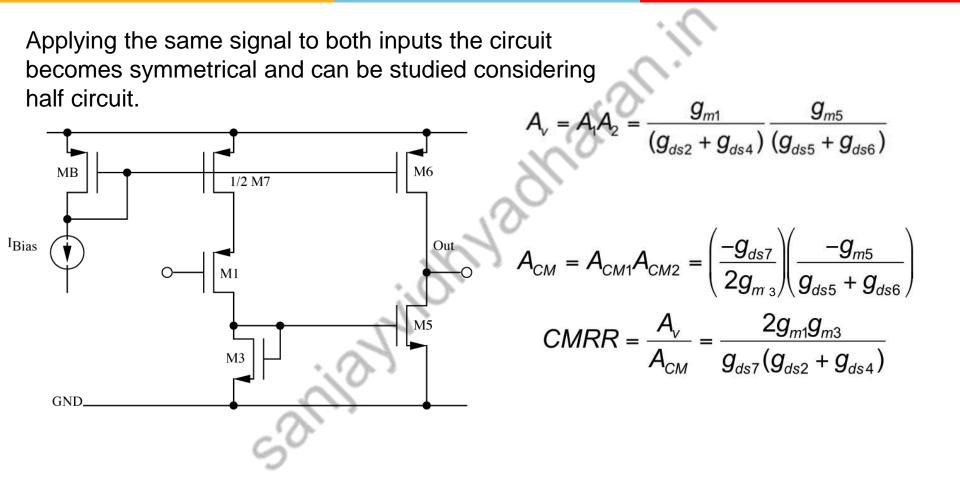

#### DC differential gain:

It is the open-loop voltage gain measured at DC with a small differential input signal. Typically Ad = 80 - 100 dB.

Analog Design for CMOS VLSI Systems Franco Maloberti

10/22/2022

#### Common mode gain:

It is the open-loop voltage gain measured at DC with a small differential input signal. Typically Ad = 20 - 40 dB.

Common mode Rejection Ratio:

**ELECTRONICS**

It is defined as the ratio between the differential gain and the common mode gain. Typically CMRR = 40 - 80 dB.

COMMUNICATION

10/22/2022

**ELECTRICAL**

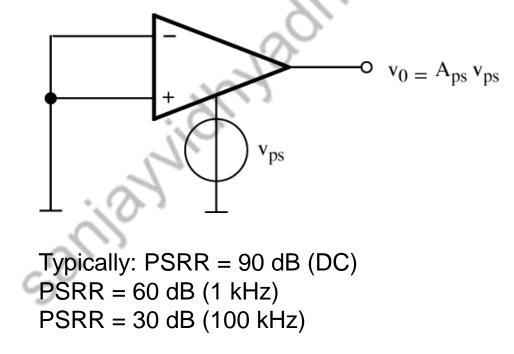

#### Power supply rejection ratio:

If a small signal is applied in series with the positive (or negative) power supply, it is transferred to the output with a given gain A ps+ (or A ps-).

The ratios between differential gain and power supply gains furnish the two PSRRs.

10/22/2022

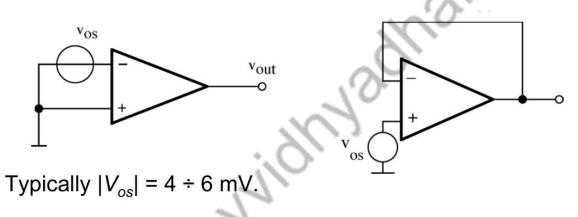

#### Input offset voltage:

In real circuits if the two input terminals are set at the same voltage the output saturates close to VDD or to VSS

#### Input common mode range:

**ELECTRONICS**

It is the maximum range of the common-mode input voltage which do not produce a significant variation of the differential gain.

COMMUNICATION

#### 10/22/2022

ELECTRICAL

#### Output voltage swing:

It is the swing of the output node without generating a defined amount of harmonic distortion.

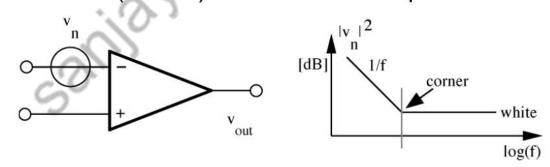

#### Equivalent input noise:

The noise performances can be described in terms of an equivalent voltage source at the input of the op-amp.

Typically  $v_n = 40 - 50 \text{ nV}/\sqrt{\text{Hz}}$  at 1 kHz, in a wide band (1 MHz) it results 10 - 50 µV RMS.

10/22/2022

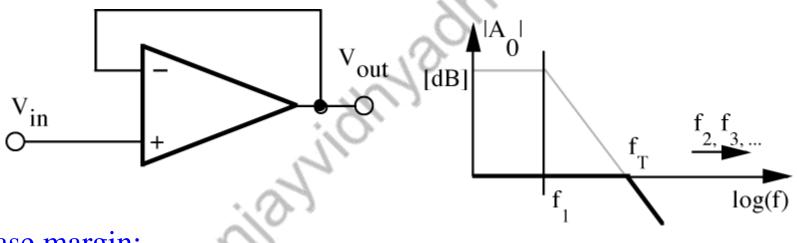

### Unity gain frequency:

It is the frequency where the open-loop gain is zero. It is also the -3 dB bandwidth in unity-gain closed loop conditions. Typically,  $f_T = 200$  MHz.

#### Phase margin:

**ELECTRONICS**

It is the phase shift of the small-signal differential gain measured at the unity gain frequency. A phase margin smaller than 60° causes ringing in the output response.

COMMUNICATION

10/22/2022

**ELECTRICAL**

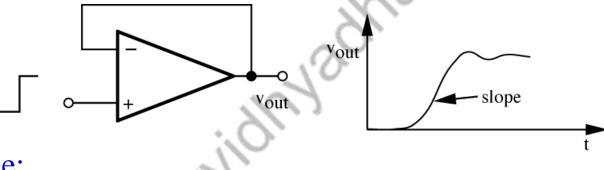

#### Slew rate:

It is the maximum slope of the output voltage. Usually it is measured in the buffer configuration. The positive slew rate can be different from the negative slew rate. Typically SR =  $50 - 200 \text{ V/}\mu\text{s}$  (lower values for micropower operation).

#### Settling time:

The settling time is the time required to settle the output within a given range (usually  $\pm 0.1\%$ ) of the final value.

### Power dissipation:

It depends on speed and bandwidth requirements. Typically, for 1.8 V supply, it is around 600  $\mu$ W.

10/22/2022

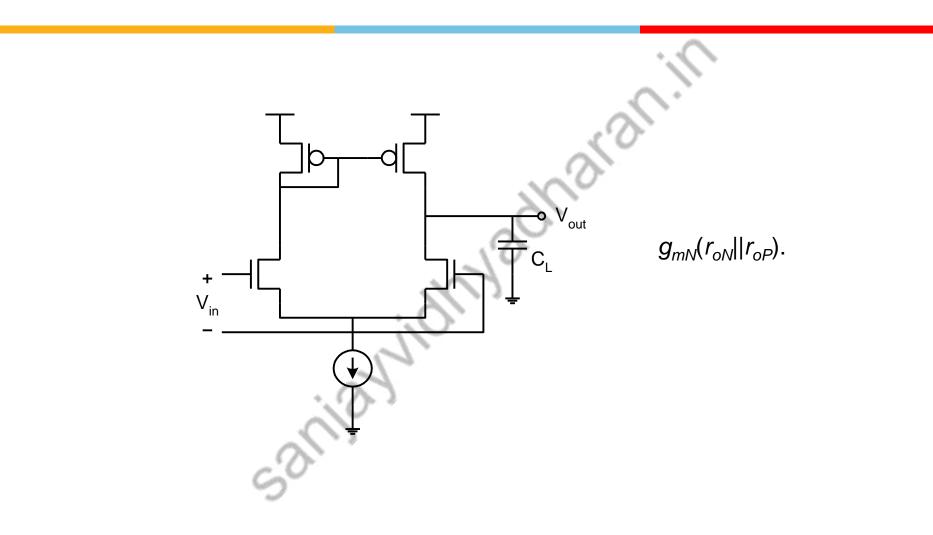

### **Single Stage Op-Amp**

10/22/2022

**ELECTRONICS**

COMMUNICATION

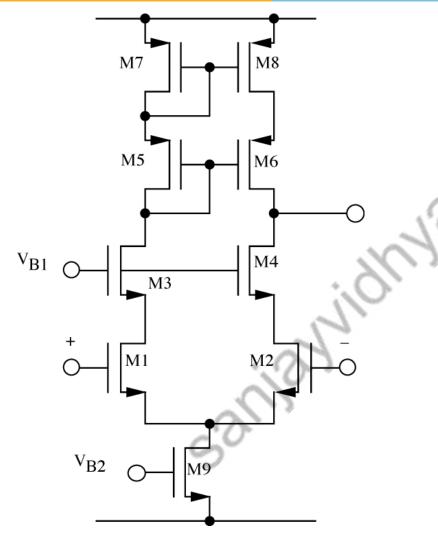

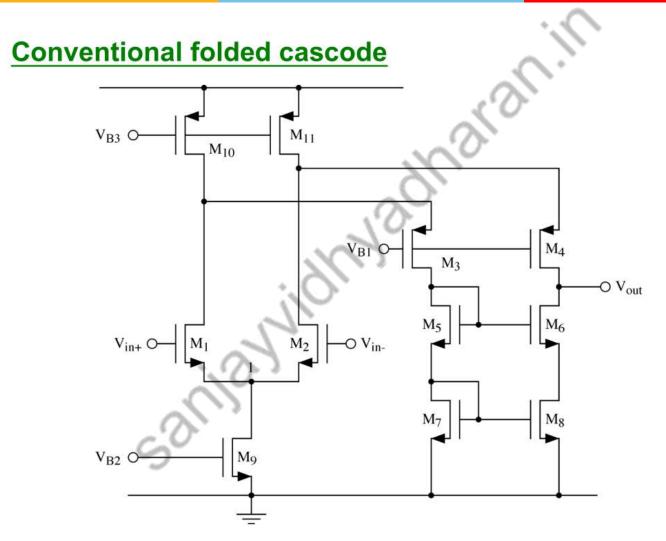

### **Single Stage Cascoded Amplifier**

### Telescopic cascode

- DC gain  $A_0 \approx (g_m r_{ds})^2$

- low power consumption

- only one high impedance node: compensated with a capacitance load (if necessary)

- Iow output swing

- reference of the input close to the negative supply

- two bias lines (V<sub>B1</sub>, V<sub>B2</sub>)

- 5 transistors in series

10/22/2022

COMMUNICATION

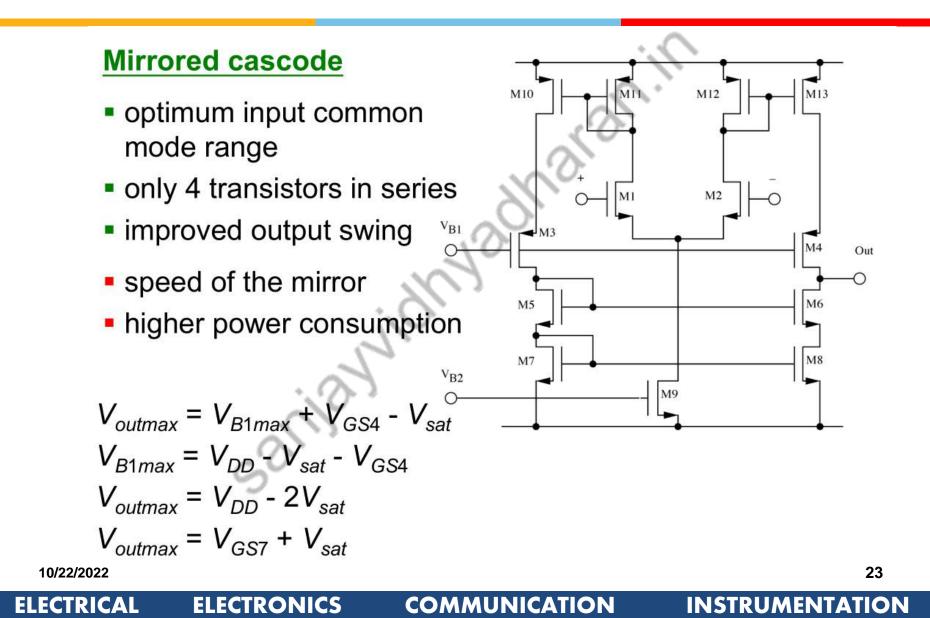

### **Single Stage Cascoded Amplifier**

### **Single Stage Cascoded Amplifier**

10/22/2022

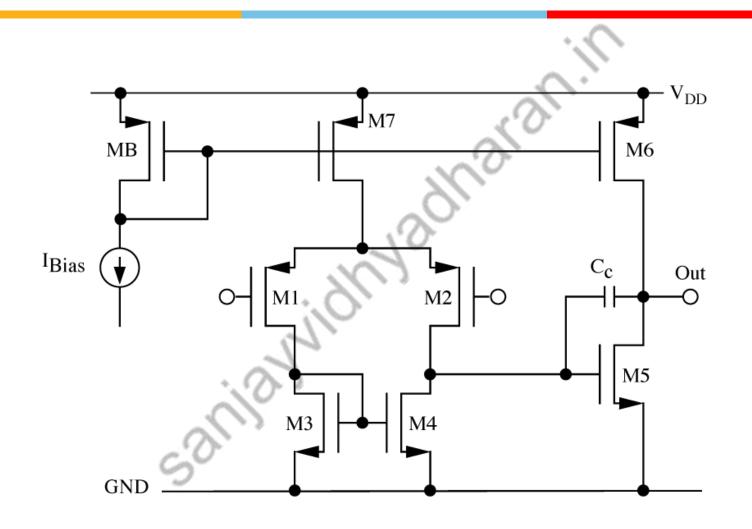

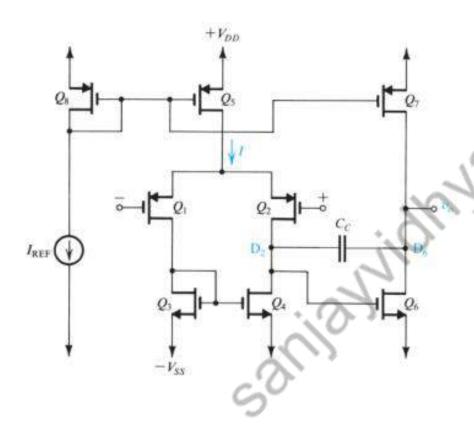

### Two-stage op-amp

10/22/2022

**ELECTRICAL**

25

**ELECTRONICS**

### **Two-stage op-amp**

COMMUNICATION

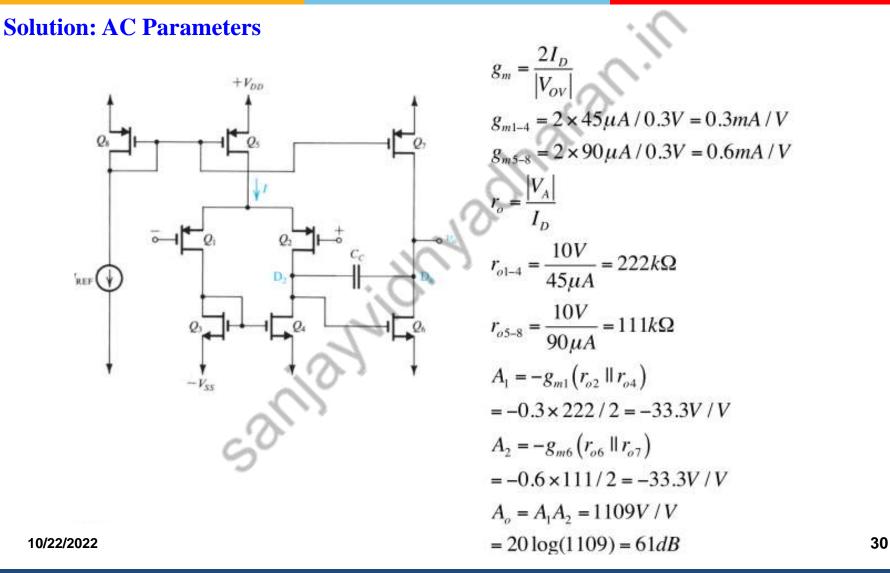

#### **Open-loop differential gain:**

The gain is obtained by multiplying the gains of the two stages.

$$A_{v} = A_{1}A_{2} = \frac{g_{m1}}{(g_{ds2} + g_{ds4})} \frac{g_{m5}}{(g_{ds5} + g_{ds6})} =$$

$$= \frac{2\sqrt{2\mu_{n}\mu_{p}}C_{ox}}{(\lambda_{n} + \lambda_{p})^{2}} \frac{\sqrt{\left(\frac{W}{L}\right)_{1}}\sqrt{\left(\frac{W}{L}\right)_{5}}\left(\frac{W}{L}\right)_{B}}}{\sqrt{\left(\frac{W}{L}\right)_{6}}\sqrt{\left(\frac{W}{L}\right)_{7}}} \frac{1}{I_{Bias}}$$

$\frac{1}{r_{eq}} = \frac{1}{r_1} + \frac{1}{r_2}$  $\frac{1}{r_{eq}} = g_{ds1} + g_{ds2}$  $r_{eq} = \frac{1}{g_{ds1} + g_{ds2}}$

$$g_m = \sqrt{2\mu_n C_{ox} \left(\frac{W}{L}\right) I_D}$$

$r_o \approx \frac{1}{\lambda I_D}$

INSTRUMENTATION

At low frequency the gain is inversely proportional to the bias current.

**ELECTRONICS**

#### 10/22/2022

### **Two-stage op-amp**

10/22/2022

COMMUNICATION

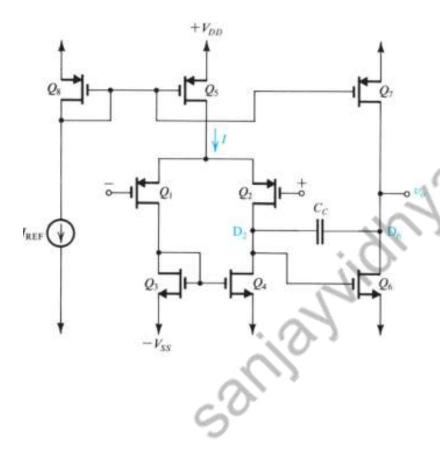

| 1200         |        |        |       |       |  |

|--------------|--------|--------|-------|-------|--|

|              | Q1     | Q2     | Q3    | Q4    |  |

| W/L<br>in um | 20/0.8 | 20/0.8 | 5/0.8 | 5/0.8 |  |

| X            | Q5     | Q6     | Q7    | Q8    |  |

| W/L<br>in um | 40/0.8 | 10/0.8 | 4/0.8 | 4/0.8 |  |

$$\begin{split} I_{\text{REF}} &= 90 \; \mu\text{A}, \; V_{\text{tn}} = 0.7 \text{V}, \; \; V_{\text{tp}} = -0.8 \text{V} \\ \mu_{\text{n}} C_{\text{ox}} &= 160 \; \mu\text{A}/\text{V}^2, \; \mu_{\text{p}} C_{\text{ox}} = 40 \; \mu\text{A}/\text{V}^2 \\ |V_{\text{A}}| &= 10 \text{V} \; \text{for all devices} \\ V_{\text{DD}} &= V_{\text{SS}} = 2.5 \text{V} \end{split}$$

Find I<sub>D</sub>, |V<sub>OV</sub>|, |V<sub>GS</sub>|, g<sub>m</sub>, r<sub>o</sub> for all Q's, voltage gain, input common mode range, output voltage range.

10/22/2022

COMMUNICATION

Δ

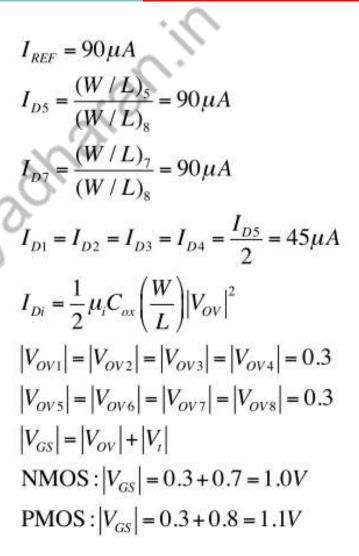

**Solution: DC Parameters**

10/22/2022

COMMUNICATION

ELECTRICAL

ELECTRONICS

#### **Solution: Input Common-Mode Ranges**

Input common-mode voltage range: Maximum: Q<sub>5</sub> near edge of saturation  $|V_{DS5}| = |V_{OV5}| = 0.3V$   $v_{icmmax} = 2.5 - |V_{OV5}| - |V_{GS5}|$ = 2.5 - 0.3 - 1.1 = 1.1V

Minimum: Q1 near edge of saturation

$$\begin{aligned} v_{D1} &= -V_{SS} + V_{GS3} = -2.5 + 1 = -1.5V \\ \left| v_{DS1} \right| &= \left| v_{GS1} \right| - \left| v_{tp} \right| \\ -v_{DS1} &= -v_{GS1} - 0.8 \\ -v_{D1} &= -v_{G1} - 0.8 \\ v_{icmmin} &= v_{G1} = v_{D1} - 0.8 = -2.3V \end{aligned}$$

10/22/2022

**Solution: Output Ranges**

Output voltage range: Maximum: Q<sub>7</sub> near edge of saturation  $|V_{OV7}| = 0.3V$   $v_{omax} = 2.5 - |V_{OV7}| = 2.2V$ Minimum: Q<sub>6</sub> near edge of saturation  $v_{omin} = -V_{SS} + |V_{OV6}| = -2.5 + 0.3 = -2.2V$

10/22/2022

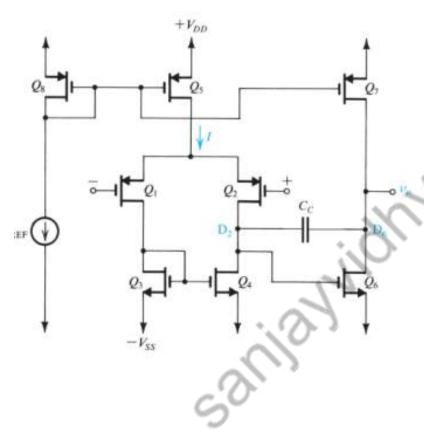

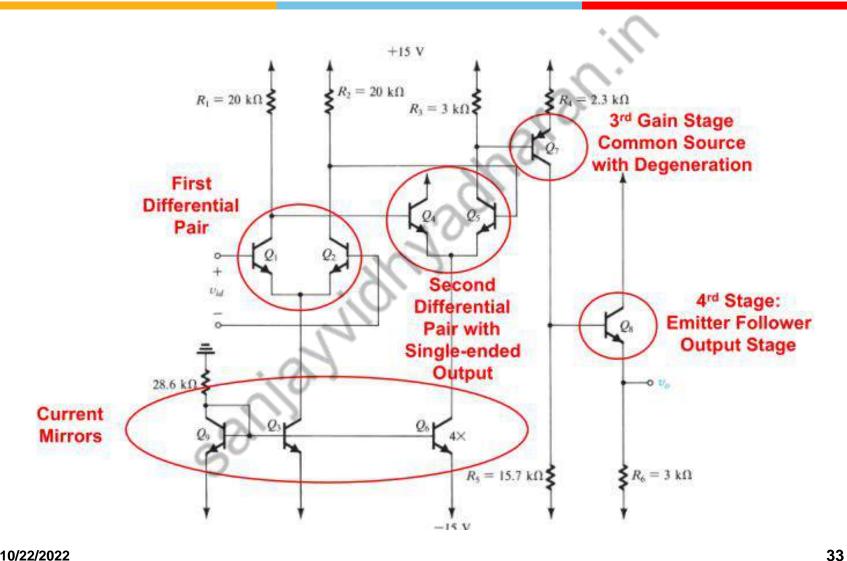

### **A Four-Stage Bipolar Op-Amp**

COMMUNICATION

10/22/2022

**ELECTRICAL**

**ELECTRONICS**

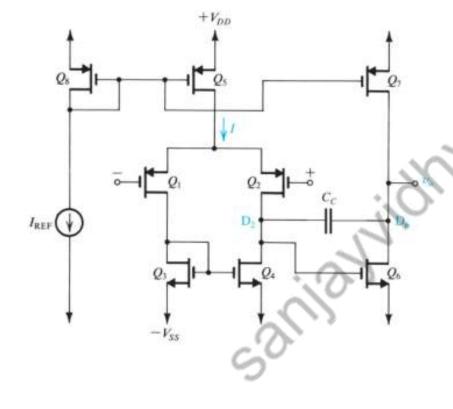

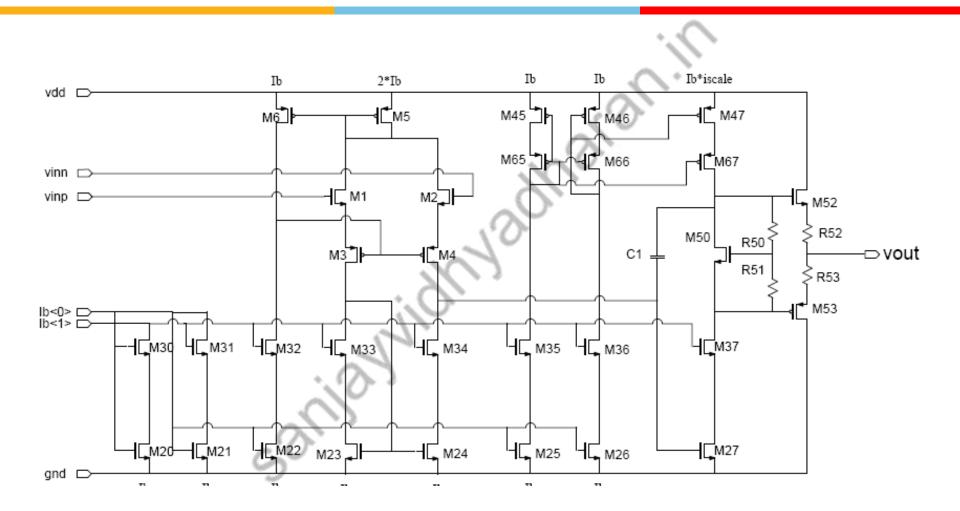

## **CMOS Implementation of 741 Op-Amp**

10/22/2022

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

INSTRUMENTATION

10/22/2022

COMMUNICATION