INSTRUMENTATION

# Advanced VLSI Design: 2021-22 Lecture 4A Pipelined Registers

# By Dr. Sanjay Vidhyadharan

ELECTRICAL ELECTRONICS

COMMUNICATION

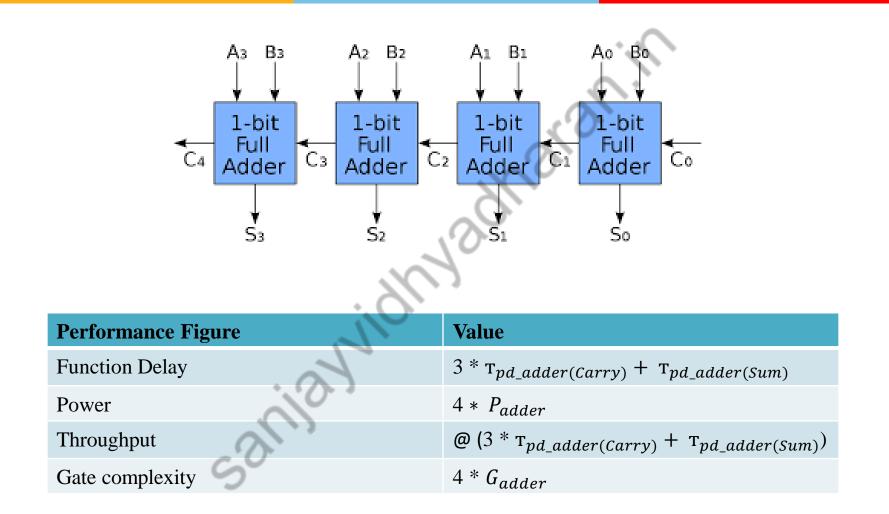

#### **4-Bit Adder**

#### 8/14/2022

#### COMMUNICATION

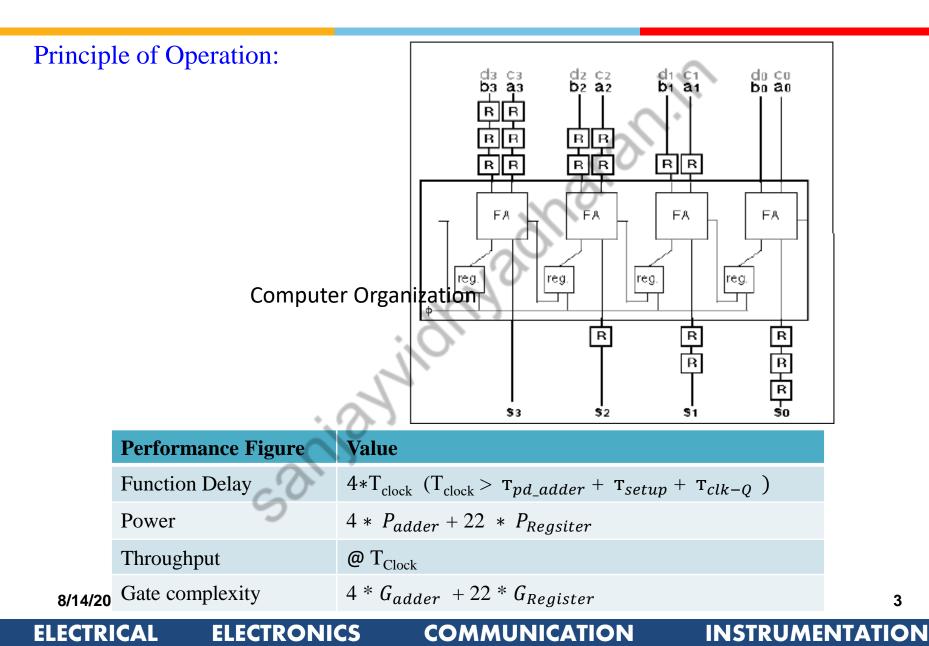

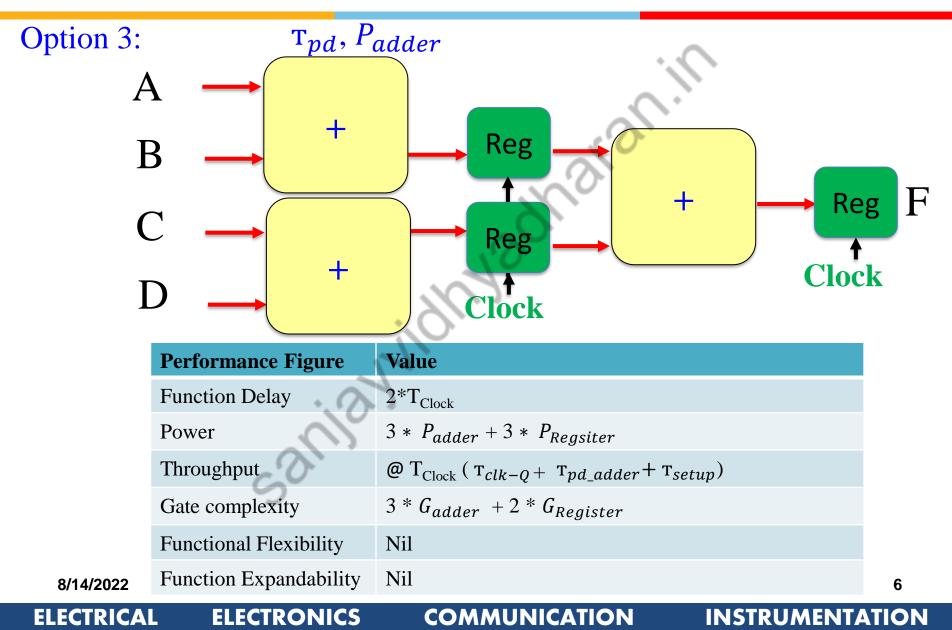

#### **Pipelined 4-Bit Adder**

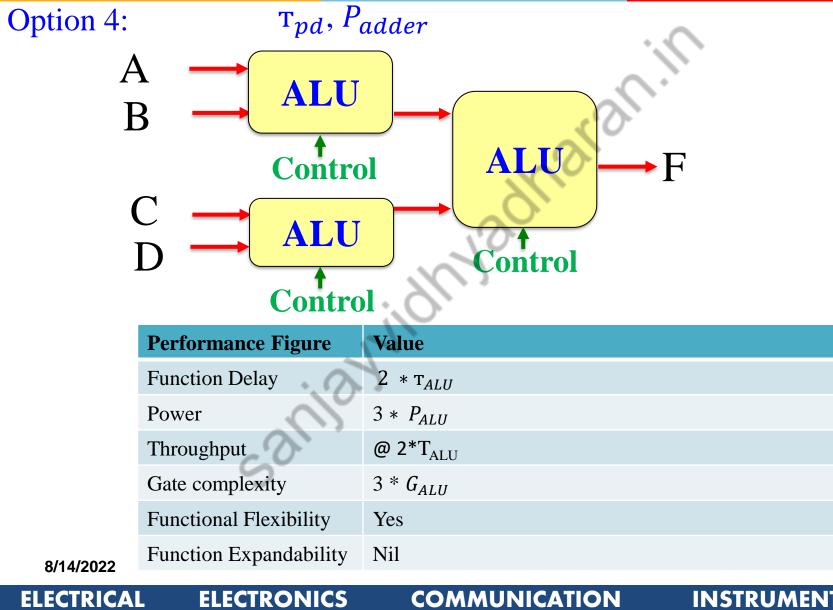

# **Example 2**

# Example 2

# Example 2

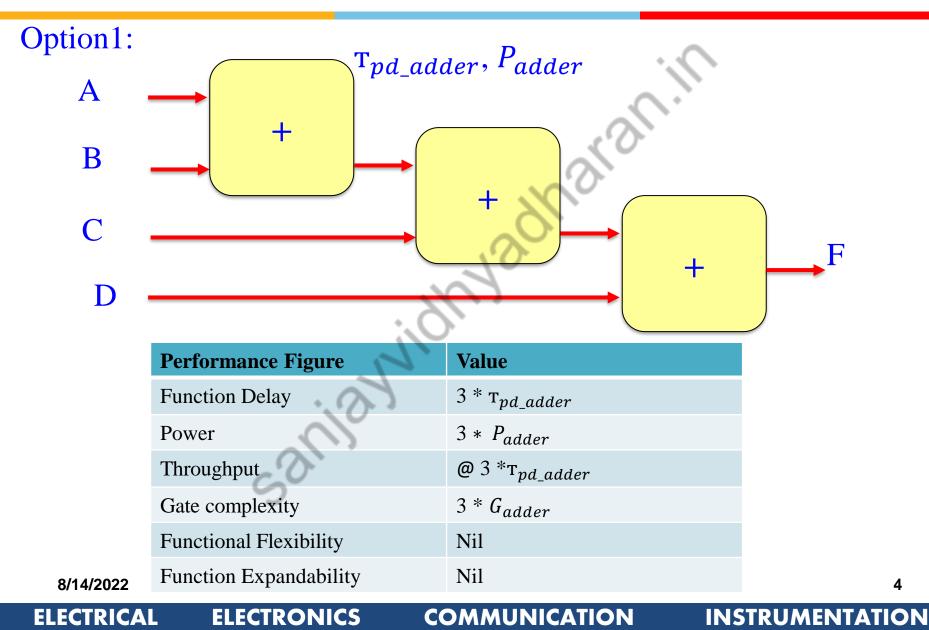

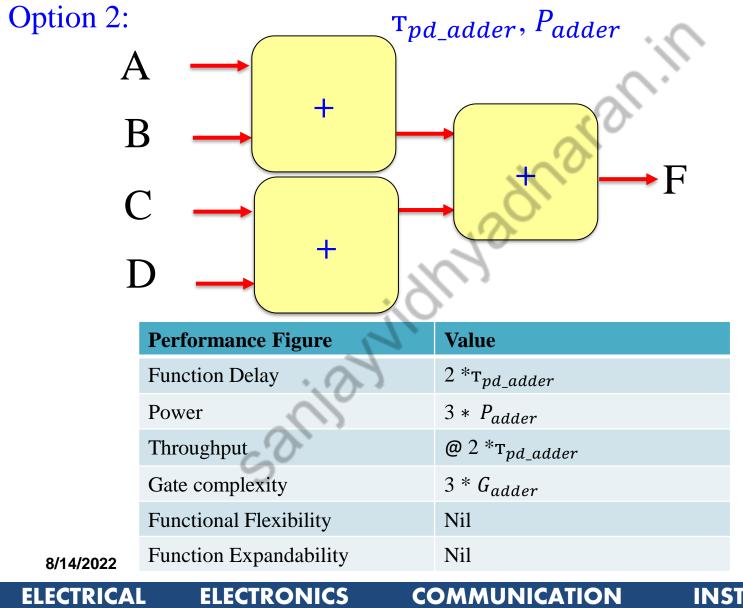

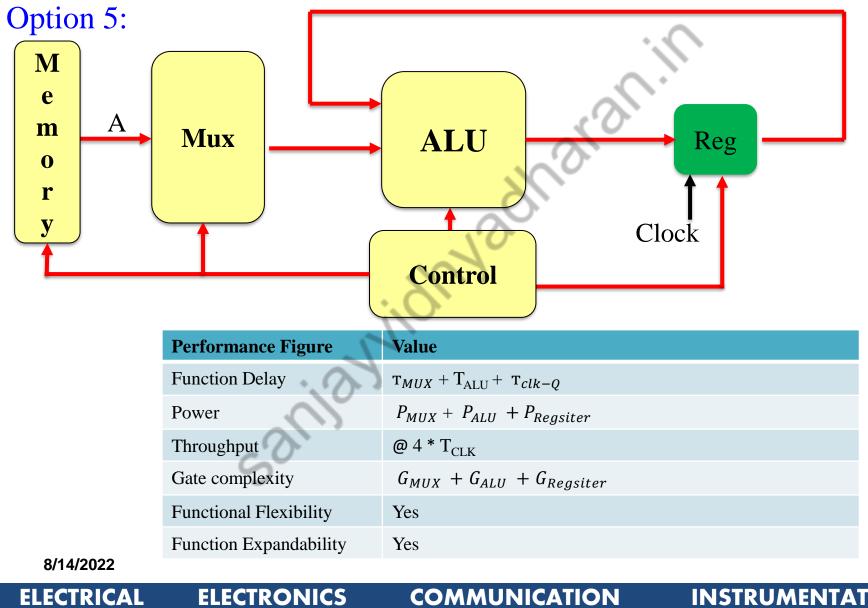

# VLSI Architecture Example 1

# VLSI Architecture Example 1

**INSTRUMENTATION**

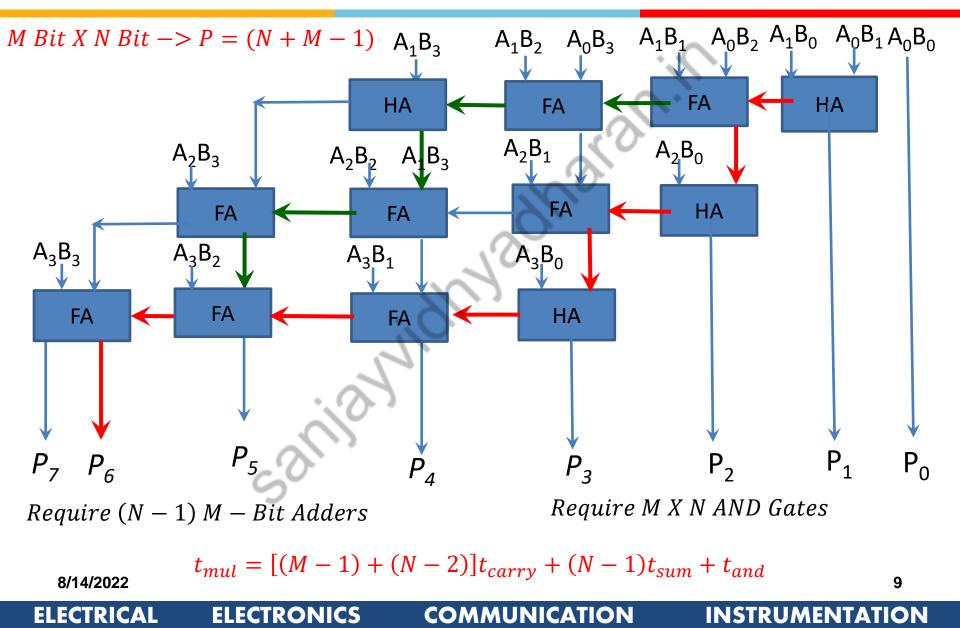

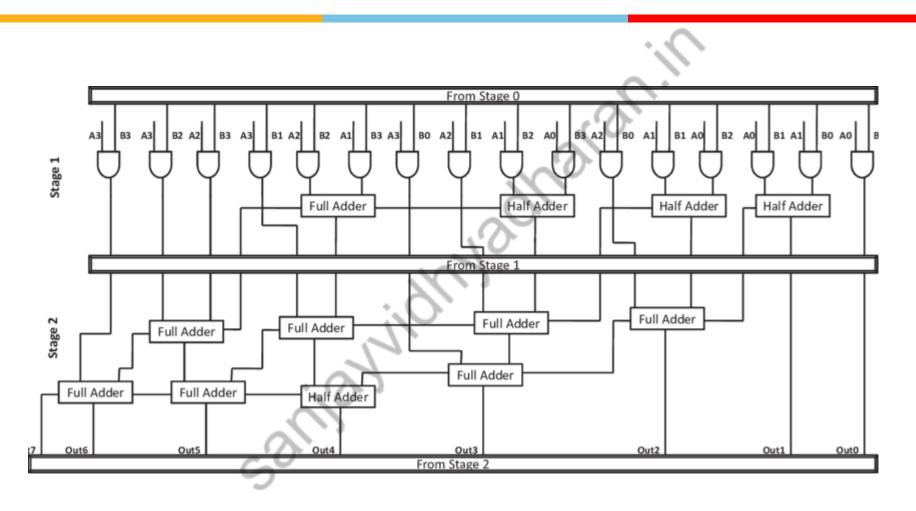

# **The Array Multiplier**

# **4-Bit Pipelined Multiplier**

ELECTRONICS COMMUNICATION

**ELECTRICAL**

#### **INSTRUMENTATION**

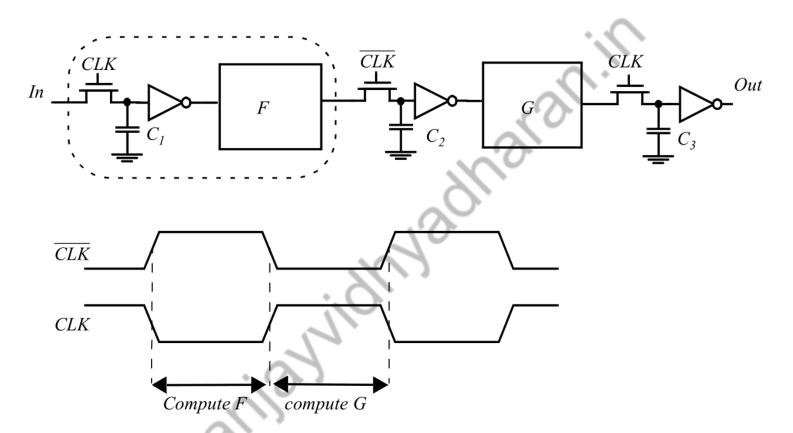

#### **Pipelining with Latches**

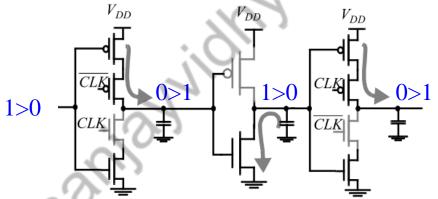

A non-overlapping clock essential for correct operation. Else there will be race around

COMMUNICATION

**ELECTRONICS**

#### 8/14/2022

**ELECTRICAL**

INSTRUMENTATION

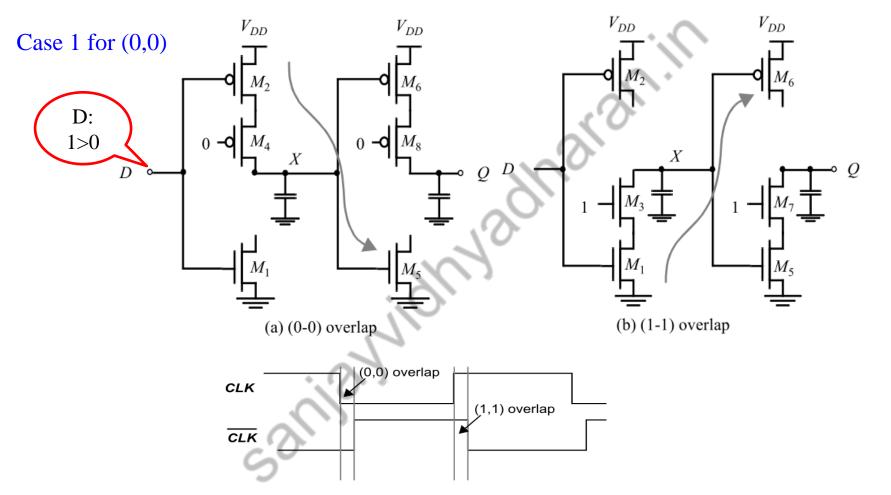

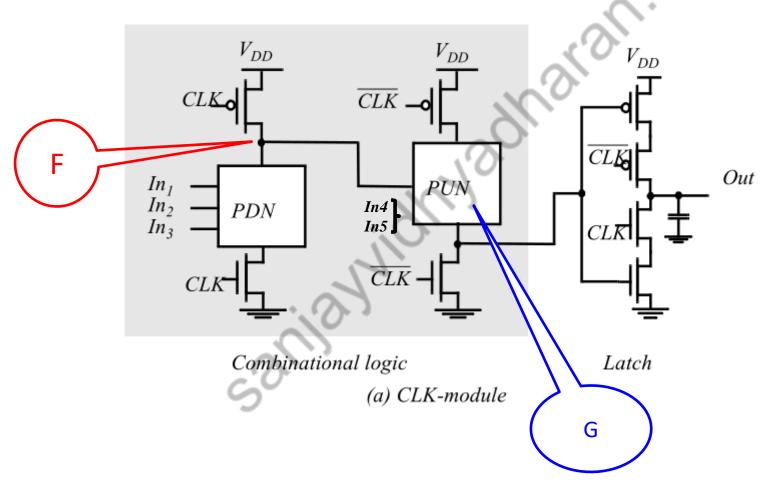

## **Clock-Skew Insensitive C<sup>2</sup>MOS Register**

If the D input changes during the overlap period, node X can make a transition, but cannot propagate to the output. 8/14/2022 12

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

INSTRUMENTATION

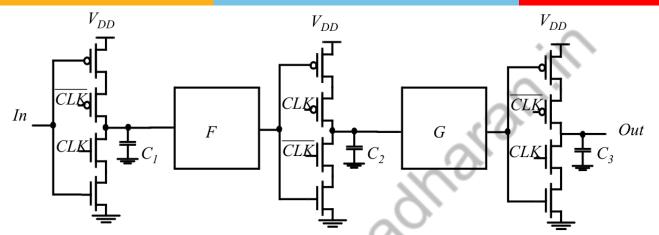

## **Pipelined Logic using C<sup>2</sup>MOS**

Potential race condition during (0-0) overlap in C<sup>2</sup>MOS-based design

Similar considerations are valid for the (1-1) overlap.

A C<sup>2</sup>MOS-based pipelined circuit is race-free as long as all the logic functions F (implemented using static logic) between the latches are non-inverting

COMMUNICATION

INSTRUMENTATION

**ELECTRONICS**

8/14/2022

**ELECTRICAL**

COMMUNICATION

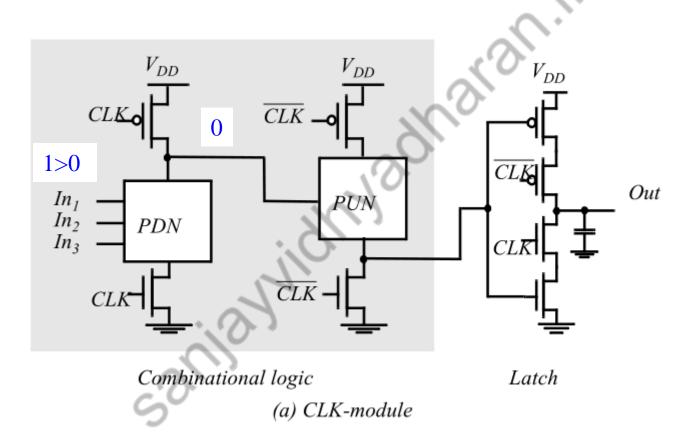

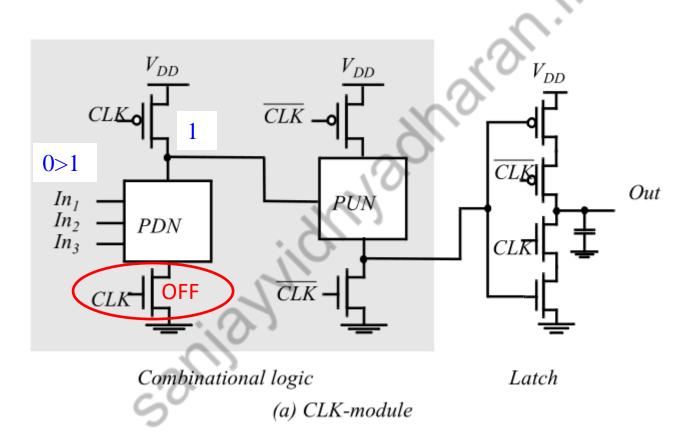

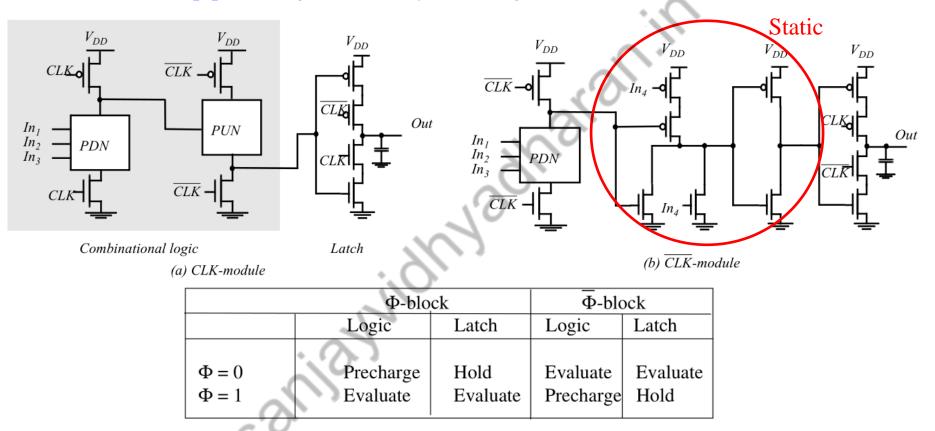

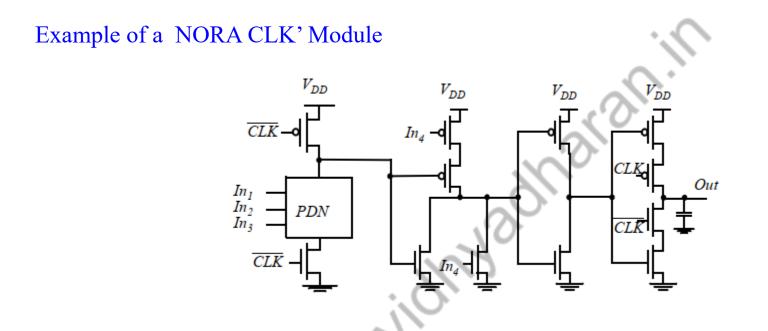

It combines C<sup>2</sup>MOS pipeline registers and dynamic logic functional blocks.

**ELECTRONICS**

8/14/2022

**ELECTRICAL**

INSTRUMENTATION

It combines C<sup>2</sup>MOS pipeline registers and dynamic logic functional blocks.

**ELECTRICAL**

**ELECTRONICS**

It combines C<sup>2</sup>MOS pipeline registers and dynamic logic functional blocks.

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

It combines C<sup>2</sup>MOS pipeline registers and dynamic logic functional blocks.

NORA offers designers a wide range of design choices. Dynamic and static logic can be mixed freely. A NORA datapath consists of a chain of alternating CLK and CLK modules. While one class of modules is precharging with its output latch in hold mode, preserving the pre-vious output value, the other class is evaluating. Data is passed in a pipelined fashion from module to module.

8/14/2022

ELECTRICAL ELECTRONICS

COMMUNICATION

ELECTRONICS

In order to ensure correct operation, two important rules should always be followed: • **The dynamic-logic rule:** Inputs to a dynamic  $CLK_n(CLK_p)$  block are only allowed to make a single  $0 \rightarrow 1$  ( $1 \rightarrow 0$ ) transition during the evaluation period.

• The C<sub>2</sub>MOS rule: In order to avoid races, the number of static inversions between C<sub>2</sub>MOS latches should be even.

COMMUNICATION

8/14/2022

**ELECTRICAL**

8/14/2022