# VLSI SYSTEMS AND ARCHITECTURE 2021-22 Lecture 8

**Hardware Flowcharts Part-3**

By Dr. Sanjay Vidhyadharan

ELECTRICAL

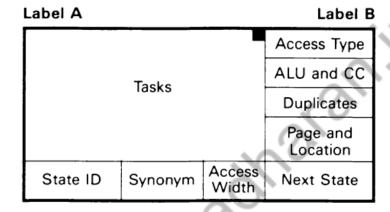

### **State Identifiers**

Sequence Label A

Operation format or instruction

type

Example: rx op ry → ry

rx op mem → mem

Sequence Label B

Operation sequence or address

mode sequence

Example: ADD, AND, SUB

Register Indirect

Indexed

Access Type

DR Data Read DW Data Write

IR Instruction Read

NA No Access

ALU and CC (ALU function and Condition Code setting)

Example: ADD, AND, or OP condition codes

condition code S Set

N Not set X Don't care

**Duplicates**

(Not used in MIN)

Page and Location

(Not used in MIN)

**Next State**

BC Branch Conditionally

IB Instruction Branch

SB Sequence Branch

State ID Direct transfer

Access Width

(Not used in MIN)

Synonym

(Not used in MIN)

State ID

State Identification

indicates external bus activity

Example 1: ADD

RX AR

RY

| $R \rightarrow R$         | ADD   |

|---------------------------|-------|

| rx→a→alu                  | na    |

| ry→b→alu                  | op-s  |

|                           |       |

|                           |       |

| oprr1                     | oprr2 |

| edb→irf                   | ir    |

| pc→a→alu, ao<br>t1 →b →ry | add-n |

| +1→alu                    |       |

| •                         | 7     |

| oprr2                     | oprr3 |

| irf→ire                   | na    |

| t1→b→pc                   | x-n   |

|                           |       |

|                           |       |

| oprr3                     | ib    |

|   | Label A  |         |                 | Label B              |

|---|----------|---------|-----------------|----------------------|

|   | 9        |         |                 | Access Type          |

|   | 7100     | Tasks   |                 | ALU and CC           |

|   | O.       | IdSKS   |                 | Duplicates           |

| 1 | 30       |         |                 | Page and<br>Location |

| , | State ID | Synonym | Access<br>Width | Next State           |

| RY→RX                       |   |       | LOAD  |

|-----------------------------|---|-------|-------|

| edb→irf                     |   |       | ir    |

| pc→a→alu, ao<br>ry→b→rx, t2 |   | add-x |       |

| +1 → alu                    | - |       |       |

|                             |   |       |       |

| ldrr1                       |   |       | ldrr2 |

| irf→ire                     |   |       | na    |

| t1→b→<br>t2→a→              | • |       | add-s |

| 0→alu                       |   |       |       |

|                             |   | -     | 9,,,  |

| ldrr2                       |   | S     | ib    |

| RX→RY                      |                       |       | STORE |

|----------------------------|-----------------------|-------|-------|

| edb→irf                    |                       | ir    |       |

| pc→a→alu, ao<br>rx→b→ry +2 |                       | add-x |       |

|                            | rx→b→ry, t2<br>+1→alu |       |       |

|                            |                       |       |       |

| strr1                      |                       |       | strr2 |

| irf→ire                    |                       |       | na    |

| t1→b→<br>t2→a→             | •                     |       | add-s |

| 0→alu                      |                       |       |       |

|                            |                       |       |       |

| strr2                      |                       |       | ib    |

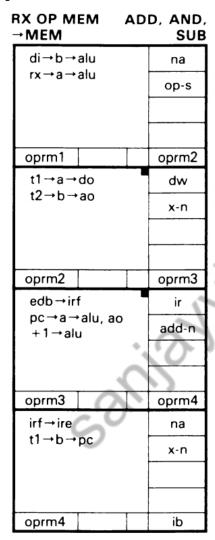

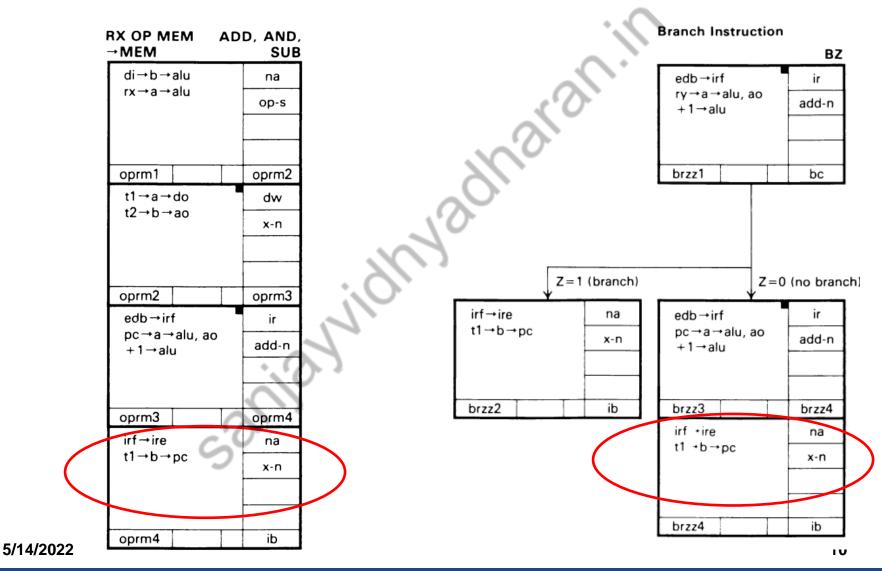

## **Execution Sequences with a Memory Operand Reference**

| MEM→RX                  | LOAD  |

|-------------------------|-------|

| di→b→rx, t2             | ir    |

| edb→irf<br>pc→a→alu, ao | add-x |

| +1→alu                  |       |

|                         |       |

| ldrm1                   | ldrm2 |

| irf→ire                 | na    |

| t1→b→pc<br>t2→a→alu     | add-s |

| 0 → alu                 |       |

| S                       | )     |

| ldrm2                   | ib    |

|    | Label A  |         |                 | Label B              |

|----|----------|---------|-----------------|----------------------|

|    | 0,       |         |                 | Access Type          |

| ľ  | 0.       | Tasks   |                 | ALU and CC           |

| N. |          |         |                 | Duplicates           |

|    |          |         |                 | Page and<br>Location |

|    | State ID | Synonym | Access<br>Width | Next State           |

## **Execution Sequences with a Memory Operand Reference**

| RX→MEM                      | STORE |

|-----------------------------|-------|

| rx→a→alu, do                | dw    |

| t2→b→ao<br>0→alu            | add-s |

| }                           |       |

|                             |       |

| strm1                       | strm2 |

| edb→irf                     | ir    |

| pc → a → alu,ao<br>+1 → alu | add-n |

|                             |       |

| strm2                       | strm3 |

| irf→ire                     | na 🧹  |

| t1→b→pc                     | x-n   |

|                             | 9     |

|                             |       |

| strm3                       | ib    |

| Label A  | <i>)</i> - |                 | Label B              |

|----------|------------|-----------------|----------------------|

| 20/      |            |                 | Access Type          |

| 10       | Tasks      |                 | ALU and CC           |

| 3        | lasks      |                 | Duplicates           |

|          |            |                 | Page and<br>Location |

| State ID | Synonym    | Access<br>Width | Next State           |

6

## **Execution Sequences with a Memory Operand Reference**

|   | Label A  | <i>y</i> - |                 | Label B              |  |

|---|----------|------------|-----------------|----------------------|--|

|   | 0/       |            |                 | Access Type          |  |

|   | 0.       | Tasks      |                 | ALU and CC           |  |

| / | 3        | idsks      |                 | Duplicates           |  |

|   |          |            |                 | Page and<br>Location |  |

|   | State ID | Synonym    | Access<br>Width | Next State           |  |

(RY + d)@

|                                         | (N1 + u/@                  |

|-----------------------------------------|----------------------------|

| edb→di                                  | ir                         |

| pc →a →alu, ao<br>+1 →alu               | add-n                      |

|                                         |                            |

|                                         |                            |

| abdm1                                   | abdm2                      |

| t1→a→pc                                 | na                         |

|                                         | x-n                        |

|                                         |                            |

|                                         |                            |

| abdm2                                   | abdm3                      |

|                                         |                            |

| di→b→alu                                | na                         |

|                                         | _                          |

| di→b→alu                                | na                         |

| di→b→alu                                | na                         |

| di→b→alu                                | na                         |

| di→b→alu<br>ry→a→alu<br>abdm3<br>edb→di | na<br>add-n                |

| di→b→alu<br>ry→a→alu<br>abdm3           | na<br>add-n<br>abdm4       |

| di→b→alu<br>ry→a→alu<br>abdm3<br>edb→di | na<br>add-n<br>abdm4<br>dr |

| di→b→alu<br>ry→a→alu<br>abdm3<br>edb→di | na<br>add-n<br>abdm4<br>dr |

| L | abel A   |         |                 | Label B              |

|---|----------|---------|-----------------|----------------------|

| I |          | 0.      | ,               | Access Type          |

| ı | al al    | Tasks   |                 | ALU and CC           |

| ١ | 0        | Idaka   |                 | Duplicates           |

|   | Mo       |         |                 | Page and<br>Location |

| I | State ID | Synonym | Access<br>Width | Next State           |

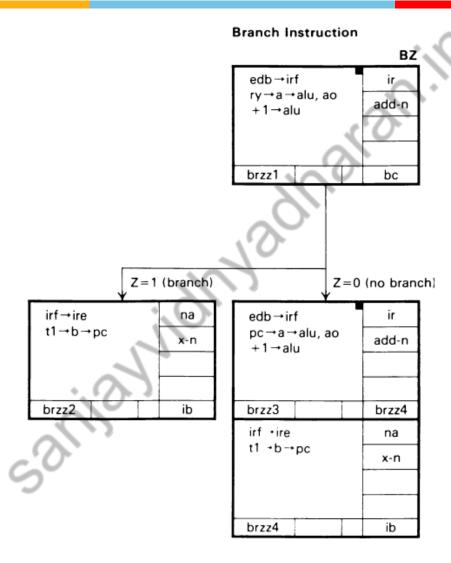

#### **Next State**

BC Branch Conditionally

IB Instruction Branch

SB Sequence Branch

State ID Direct transfer

Z: Zero Flag

JZ (RY)

**MAG RX:** This instruction examines the number stored in register RX and stores back the magnitude value of the number in register RX

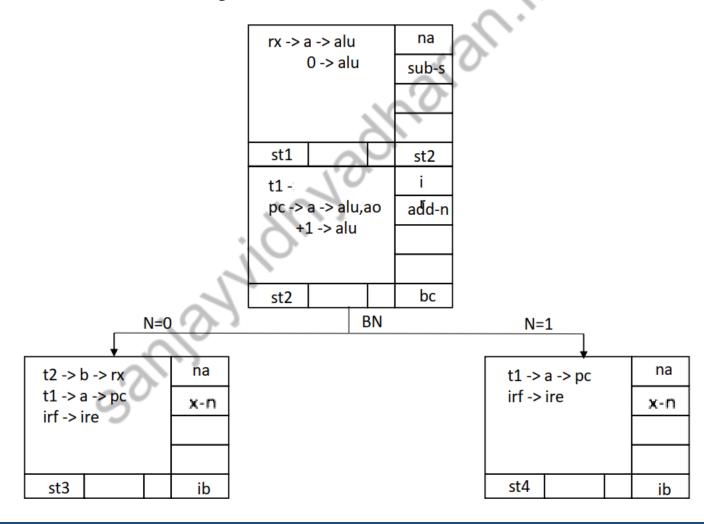

#### SORT @RX @RY:

This instruction compares the two numbers stored in memory at addresses provided by registers RX and RY. It swaps the numbers in the two memory locations if the number at the memory address provided by RY is smaller than the other number.

#### SORT @RX @RY:

|                | _     |

|----------------|-------|

| edb -> di      | dr    |

| rx -> a -> ao  | x-n   |

|                | n     |

|                |       |

| st1            | st2   |

| di -> b -> t2  | d     |

| edb -> di      | x-n   |

| ry -> a ->ao   |       |

|                |       |

| st2            | st3   |

| t2 -> a -> alu | na    |

| di -> b -> alu | sub-s |

|                | 50    |

| st3            | st4   |

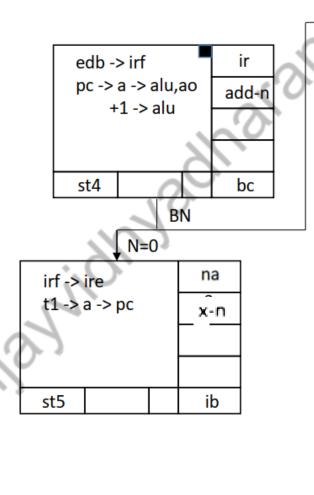

| , ,           | ↓ N=    | 1 |     |

|---------------|---------|---|-----|

| ry -> b -> ao |         |   | dw  |

| t2 -> a -> do |         |   | x-n |

|               |         |   | -   |

|               |         |   |     |

| st6           |         |   | st7 |

| di -> l       | o -> t2 |   | na  |

|               |         |   | x-n |

|               |         |   |     |

|               |         |   |     |

| st7           |         |   | st8 |

| rx -> b -> ao |         |   | dw  |

| t2 -> a -> do |         |   | x-n |

|               |         |   |     |

|               |         |   |     |

| st8           |         |   | st5 |

Thank you