# Advanced VLSI Design: 2021-22 Lecture 14-A Deep-Submicron MOSFET operation

By Dr. Sanjay Vidhyadharan

ELECTRICAL

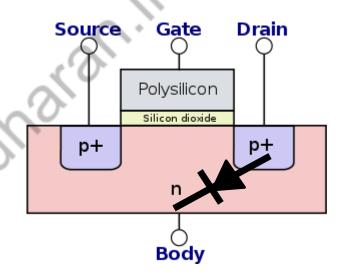

## **MOSFET Operation**

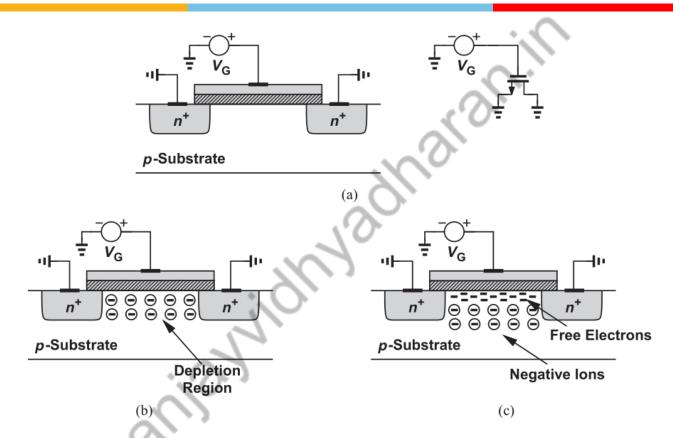

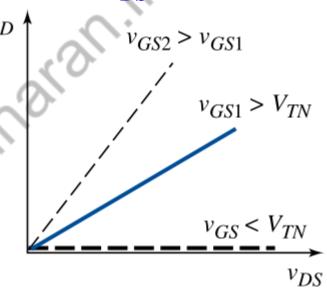

#### **Cut-off Region**

For

$$V_{GS} < V_T$$

$I_D = 0$

As a practical definition, The threshold Voltage  $V_T$  is that gate voltage when the surface is said to be inverted, i.e. the density of mobile electrons on the surface becomes equal to the density of holes in the bulk (p-type) substrate.

$$V_{T0} = \Phi_{GC} - 2\phi_F - \frac{Q_{B0}}{C_{ox}} - \frac{Q_{ox}}{C_{ox}}$$

1. The work function difference TGC between the gate and the channel reflects the built-in potential of the MOS system, which consists of the p-type substrate, the thin silicon dioxide layer, and the gate electrode. Depending on the gate material, the work function difference is

$$\emptyset_{GC} = \emptyset_{F\_Substrate}$$

-  $\emptyset_{F_{metal}}$  For Metal Gate

$$\emptyset_{GC} = \emptyset_{F\_Substrate} - \emptyset_{F_{Polysilicon}}$$

For Polysilicon Gate

2. The externally applied gate voltage must be changed to achieve surface inversion, i.e., to change the surface potential by - 2  $\emptyset$ <sub>F</sub>. This will be the second component of the threshold voltage.

$$\phi_{Fp} = \frac{kT}{q} \ln \frac{n_i}{N_A}$$

$$V_{T0} = \Phi_{GC} - 2\phi_F - \frac{Q_{B0}}{C_{ox}} - \frac{Q_{ox}}{C_{ox}}$$

3. Another component of the applied gate voltage is necessary to offset the depletion region charge, which is due to the fixed acceptor ions located in the depletion region near the surface.

$$Q_{B0} = -\sqrt{2q \cdot N_A \cdot \varepsilon_{Si} \cdot \left| -2\phi_F \right|}$$

4. There always exists a fixed positive charge density  $Q_{ox}$  at the interface between the gate oxide and the silicon substrate, due to impurities and/or lattice imperfections at the interface. The gate voltage component that is necessary to offset this positive charge at the interface is -  $Q_{OX}/C_{ox}$ .

$$V_{TH} = V_{TH \, 0} + \gamma \left( \sqrt{|2\phi_F| + V_{SB}} - \sqrt{|2\phi_F|} \right)$$

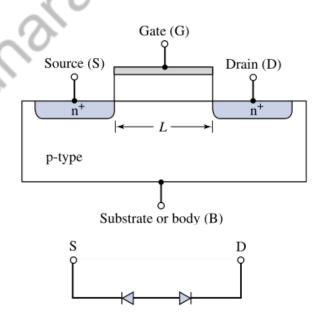

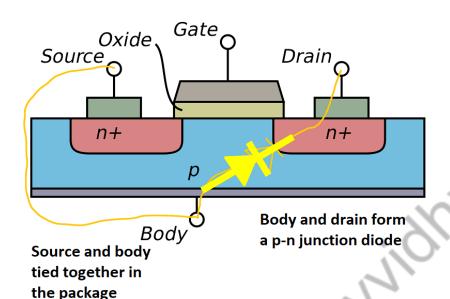

The body effect occurs in a MOSFET when the source is not tied to the substrate (which is always connected to the most negative power supply in the integrated circuit for n-channel devices and to the most positive for p-channel devices). The substrate then acts as a "second gate" or a back-gate for the MOSFET

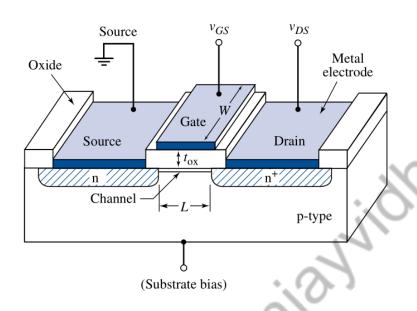

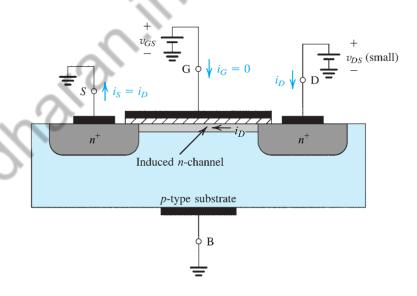

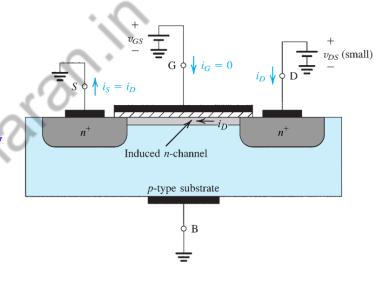

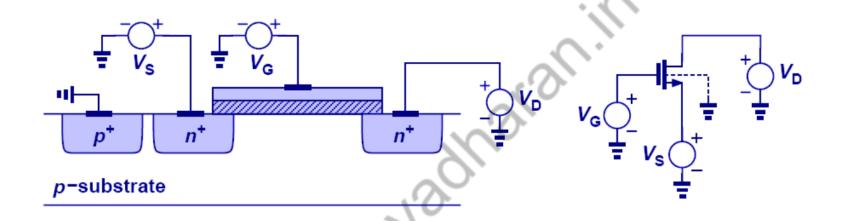

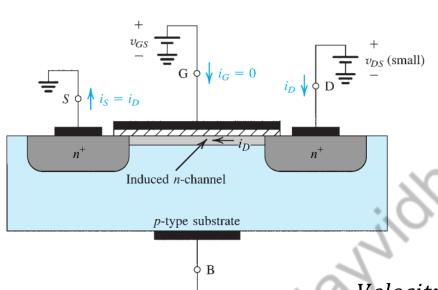

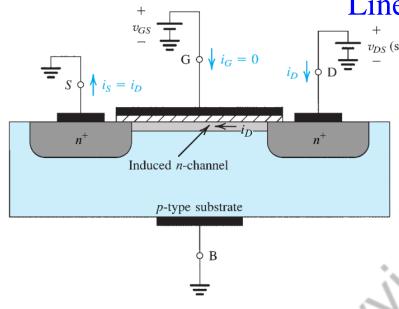

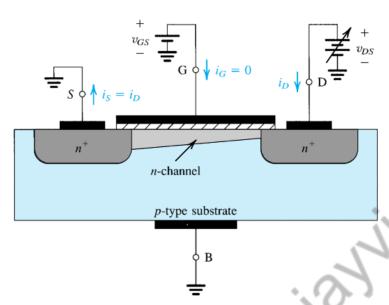

#### Linear Region- Small V<sub>DS</sub>

$$V_{ov} = V_{GS} - V_T$$

$$C_{ox}WL = \frac{Q}{V_{ox}}$$

$C_{ox}WL = rac{Q}{V_{ov}}$  Charge per unit Length  $=rac{Q}{L}=\ C_{ox}WV_{ov}$

$$Electric\ Field\ in\ Channel = \frac{V_{DS}}{L}$$

Velocity of Charge in Channel(v) =  $\mu_n E = \frac{V_{DS}\mu_n}{r}$

Current in Channel

$$(I_D) = v * \frac{Q}{L} = \frac{V_{DS}\mu_{n*}}{L} * C_{ox}WV_{ov}$$

$$I_D = \frac{\mu_{nC_{ox}}W(V_{GS} - V_T)V_{DS}}{L}$$

## Linear Region- Small V<sub>DS</sub>

$V_{a}$

$$I_D = \frac{\mu_{nC_{ox}}W(V_{GS} - V_T)V_{DS}}{L}$$

Transconductance of Channel  $g_{DS} = \frac{\mu_{nC_{ox}}WV_{ov}}{L}$

Process transconductance parameter  $k'_n = \mu_{nC_{ox}}$

$$I_D = \frac{k_n'WV_{ov}V_{DS}}{L}$$

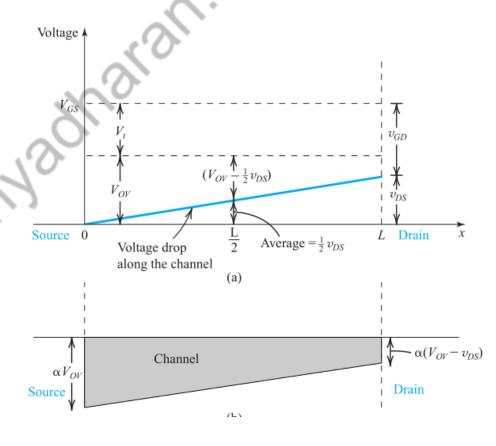

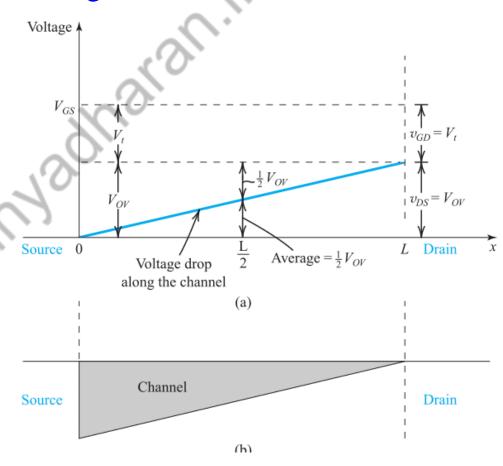

#### Linear Region as V<sub>DS</sub> is Increased

Charge in the tapered channel is proportional to the channel cross-sectional area

$$I_D = \frac{k_n'W(V_{ov} - \frac{V_{DS}}{2})V_{DS}}{L}$$

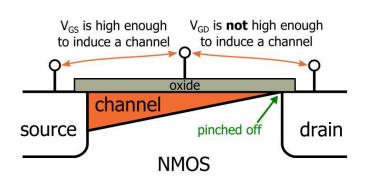

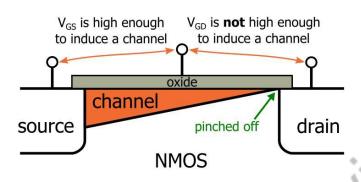

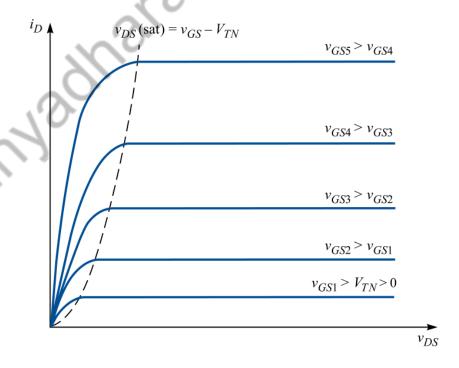

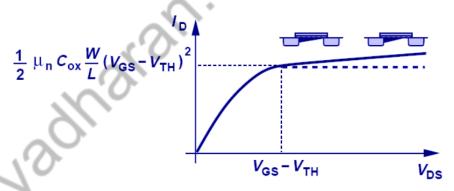

#### **Saturation Region**

$$V_{DS} = V_{ov} = V_{GS} - V_T$$

$$I_D = \frac{k_n'W(V_{ov} - \frac{V_{DS}}{2})V_{DS}}{L}$$

$$I_D = \frac{k_n' W (V_{GS} - V_T)^2}{2L}$$

$$I_D = \frac{k_n'W(V_{GS} - V_T)^2}{2L}$$

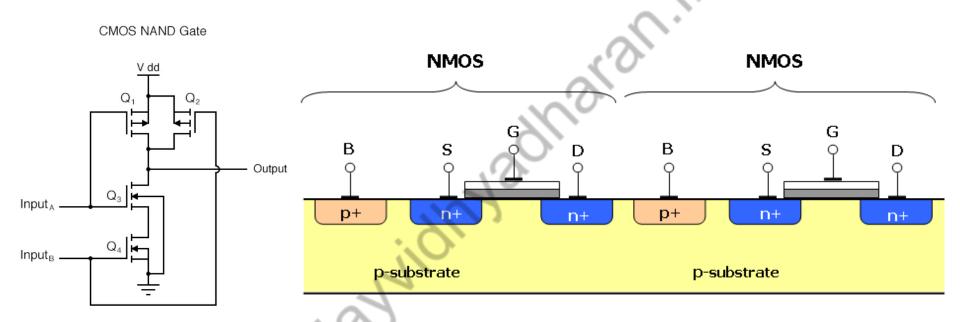

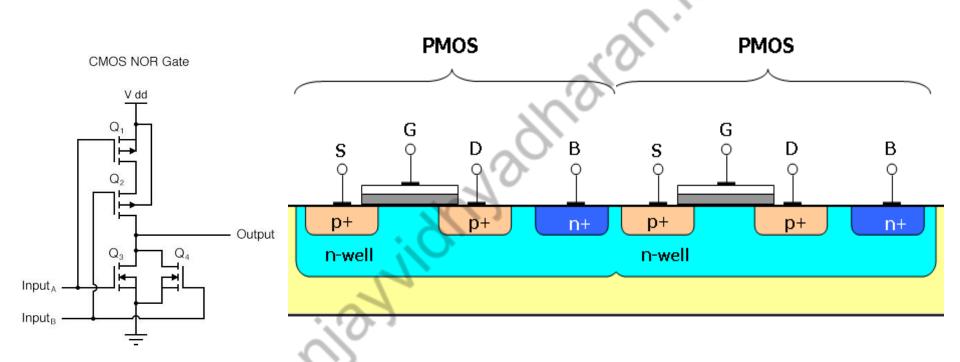

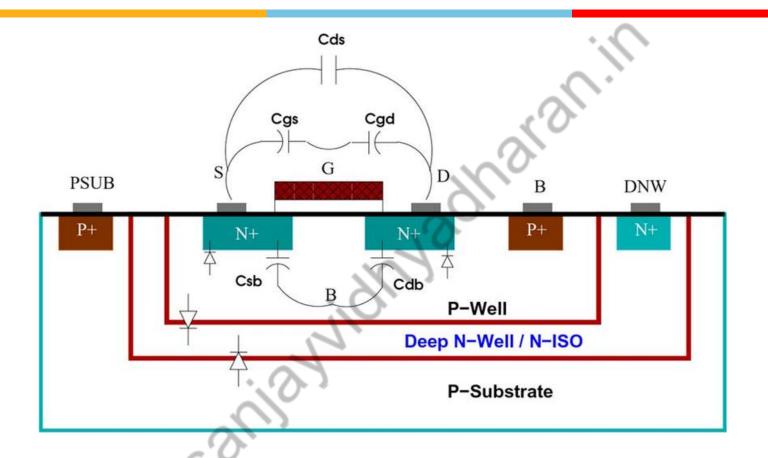

- > NMOS Body to Lowest Possible Potential (Gnd)

- ► PMOS Body to Highest Possible Potential (V<sub>DD</sub>)

> NMOS Double well : Body not same as Substrate

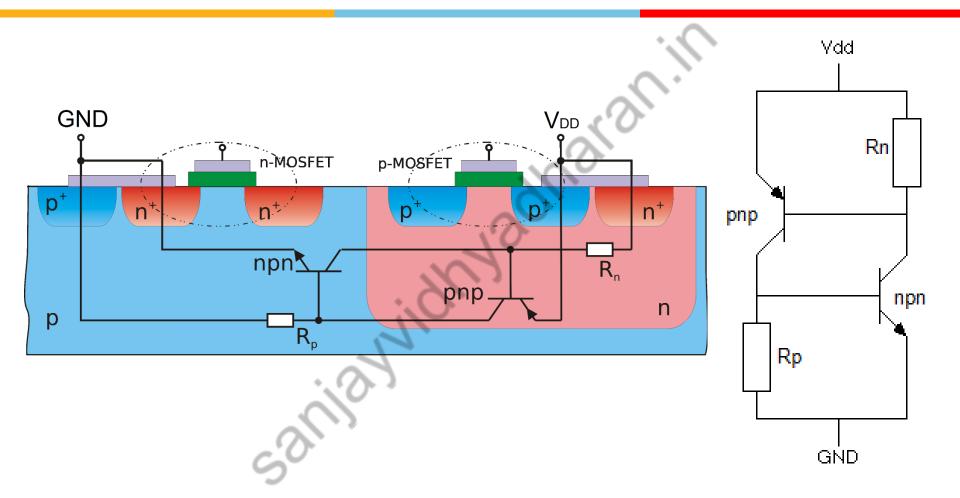

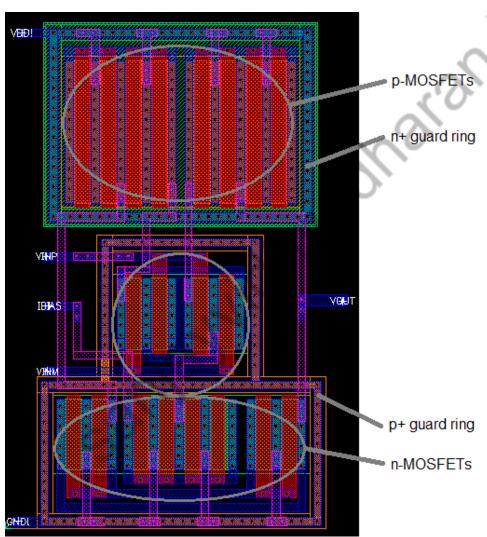

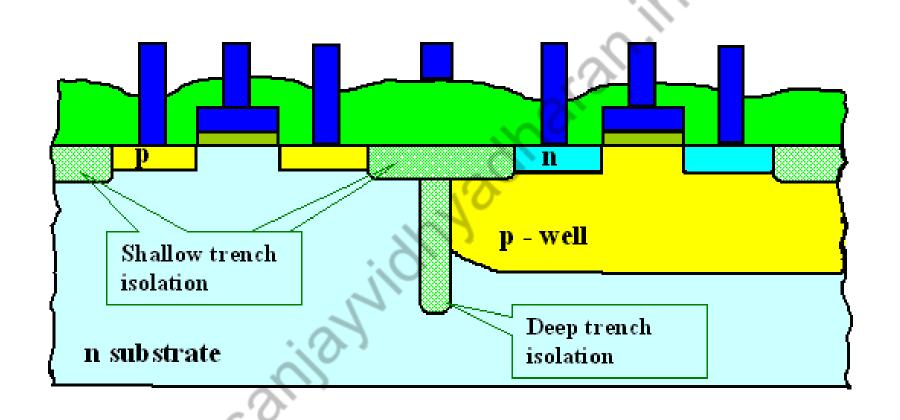

## **MOSFET LATCH**

## **MOSFET LATCH**

# **MOSFET LATCH**

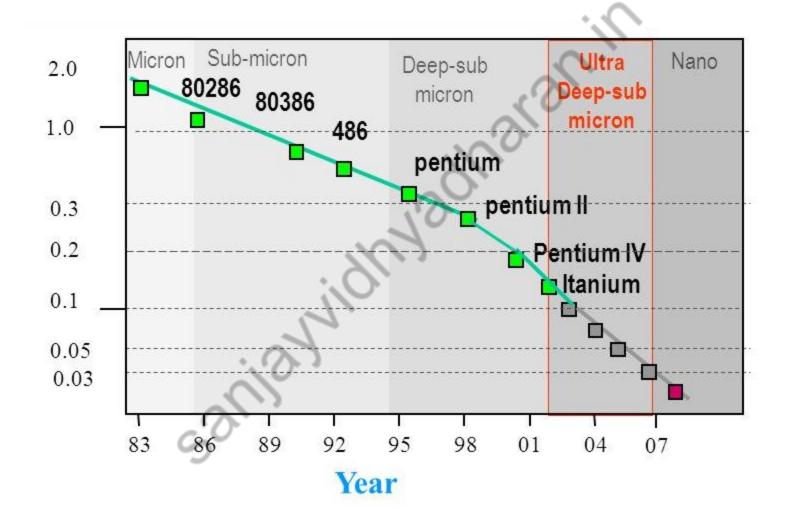

# **Deep-submicron MOSFET operation**

# **Deep-submicron MOSFET operation**

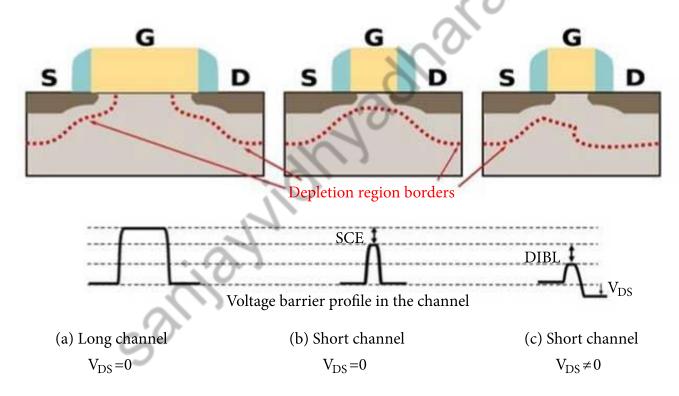

- ➤ Threshold voltage reduction

- > VT Roll Off

- ➤ Drain-induced barrier lowering (DIBL)

- ➤ Mobility degradation due to a vertical field

- ➤ Velocity saturation effects

- > Channel length modulation

- > Subthreshold (weak inversion) conduction

- ➤ Hot-electron effects on output resistance

#### **VT Variation**

- > VT Roll Off

- Drain-induced barrier lowering (DIBL)

# **Mobility Degradation**

There also exists a normal (vertical) field originating from the gate voltage that further inhibits channel carrier mobility. This effect, which is called mobility degradation, reduces the surface mobility with respect to the bulk mobility.

$$\mu_{n, eff} = \frac{\mu_{n0}}{1 + \eta(V_{GS} - V_T)}$$

$\mu_{n,\, eff} = \frac{\mu_{n0}}{1+\eta(V_{GS}-V_T)}$  with  $\mu_{n0}$  the bulk mobility and  $\eta$  an empirical parameter.

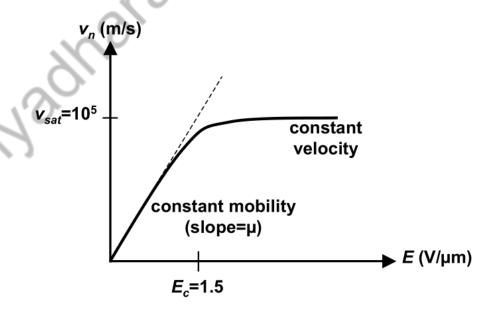

# **Velocity Saturation Effect**

When the electric field reaches a critical value EC the velocity of the carriers tends to saturate.

$$v = \frac{\mu_n E}{1 + E/E_C}$$

for  $E \le E_C$

$$v = v_{sat}$$

for  $E \ge E_C$

$$v_{sat} = \begin{cases} 8 \times 10^6 \text{ cm/s for electrons in Si} \\ 6 \times 10^6 \text{ cm/s for holes in Si} \end{cases}$$

$$\mathcal{E}_{sat} = \frac{2v_{sat}}{u}$$

5/8/2022

23

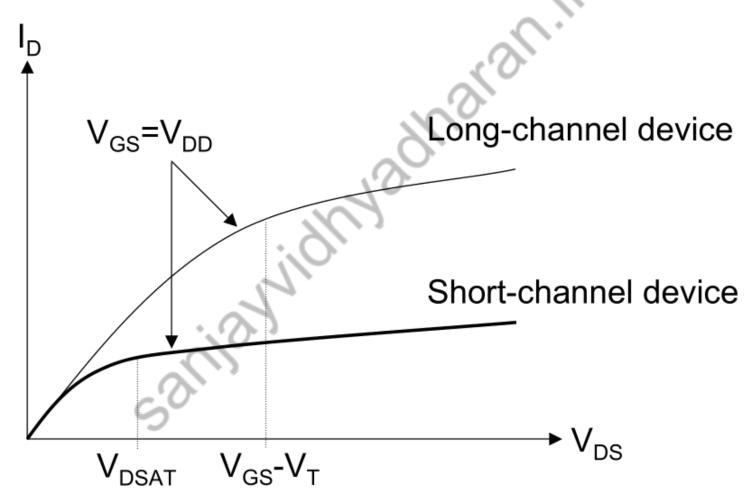

# **Velocity Saturation Effect**

#### Linear region:

$$I_{DS} = \frac{\frac{W}{L}C_{oxe}\mu_{eff,n}\left(V_{GS} - V_{Tn} - \frac{m}{2}V_{DS}\right)V_{DS}}{1 + \frac{V_{DS}}{\boldsymbol{\mathcal{E}}_{sat}L}}$$

#### Saturation region:

$$I_{DS} = I_{DSsat} = \frac{\frac{W}{2mL}C_{oxe}\mu_{eff,n}(V_{GS} - V_T)^2}{1 + \frac{V_{GS} - V_T}{\mathcal{E}_{sat}L}} \quad \mathcal{E}_{sat} = \frac{2v_{sat}}{\mu}$$

$$v_{sat} = 8 \times 10^6 \text{ cm/s}$$

for electrons in Si

# **Velocity Saturation Effect**

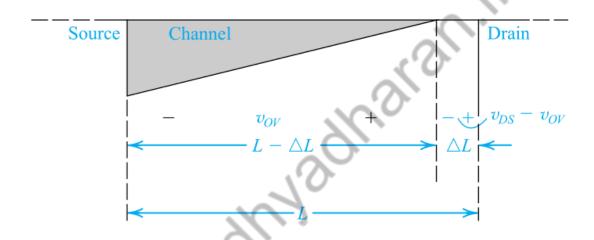

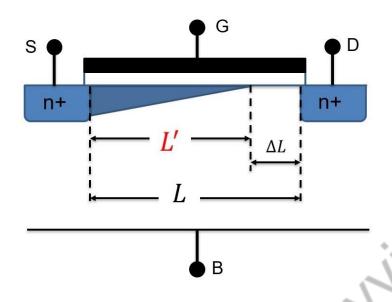

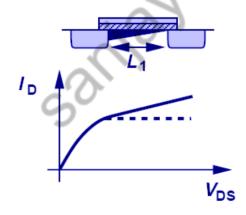

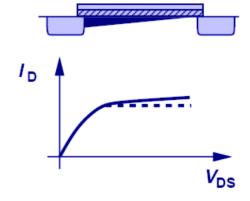

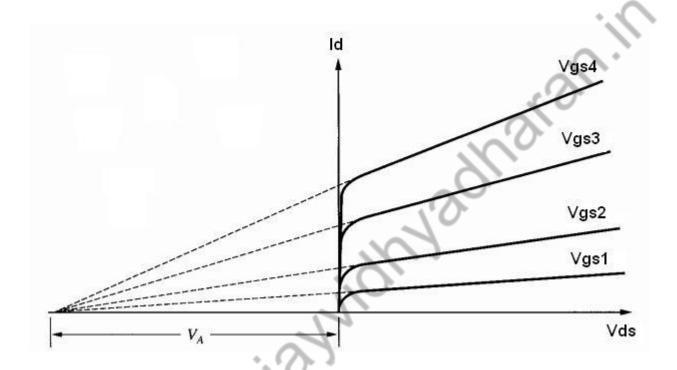

# **Channel Length Modulation**

When the  $V_{DS}$  is increased beyond  $V_{OV}$ , the pinch-off point is moved slightly away from the drain, toward the source. The additional voltage applied to the drain appears as a voltage drop across the narrow depletion region between the end of the channel and the drain region. This voltage accelerates the electrons that reach the drain end of the channel and sweeps them across the depletion region into the drain.

# **Channel Length Modulation**

$$I_{D} = \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^{2} (1 + \lambda V_{DS})$$

27

# **Channel Length Modulation**

$V_A$  Early Voltage  $\lambda = \frac{1}{V_A}$

$$\lambda = \frac{1}{V_A}$$

$$r_o \approx \frac{1}{\lambda I_D}$$

$\lambda \propto 1/L$

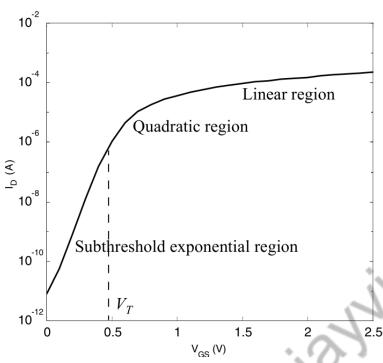

## **Subthreshold Conduction**

$$I_D = I_S e^{\frac{V_{GS}}{nkT/q}} \left(1 - e^{-\frac{V_{DS}}{kT/q}}\right)$$

where  $I_S$  and n are empirical parameters, with  $n \ge 1$  and typically ranging around 1.5.

Subthreshold current has some important repercussions. In general, we want the current through the transistor to be as close as possible to zero at  $V_{GS} = 0$ . This is especially important in the so-called dynamic circuits, which rely on the storage of charge on a capacitor and whose operation can be severely degraded by subthreshold leakage.

#### **Hot Carrier Effects**

Increase in the electric field strength causes an increasing energy of the electrons.

- > Some electrons are able to leave the silicon and tunnel into the gate oxide.

- > Such electrons are called "Hot carriers".

- $\triangleright$  Electrons trapped in the oxide change the  $V_T$  of the transistors.

- This leads to a long term reliability problem.

- ➤ For an electron to become hot an electric field of 10<sup>4</sup> V/cm is necessary.

- > This condition is easily met with channel lengths below 1μm.

Thank you