# VLSI SYSTEMS AND ARCHITECTURE 2021-22 Lecture 10 Timing Signals

By Dr. Sanjay Vidhyadharan

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

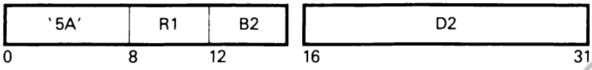

#### **Instruction Set Example**

ADD

#### A R1,D2 (B2)

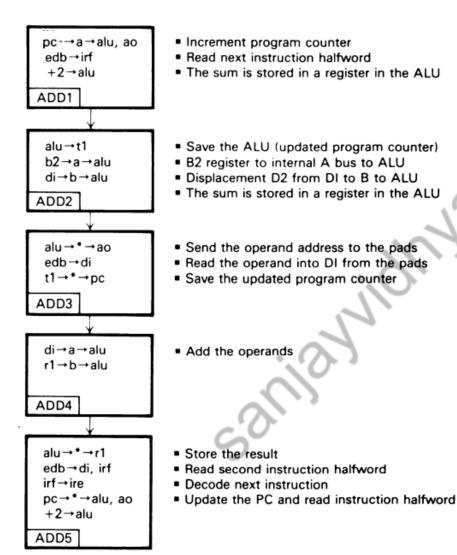

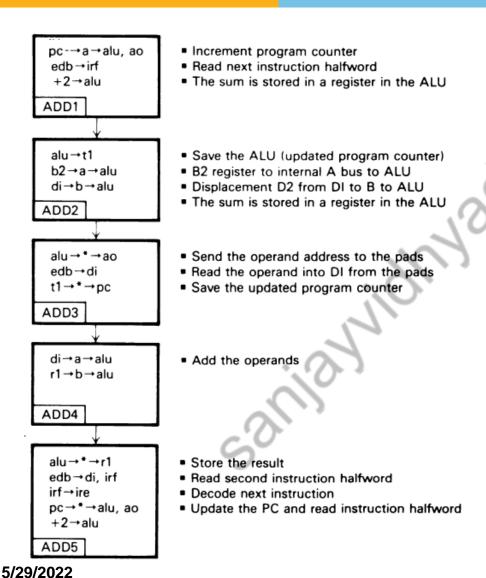

Here are the steps for the ADD instruction:

- 1. Fetch the first instruction halfword.

- 2. Find the ADD control word sequence.

- 3. Fetch the remaining instruction halfword.

- 4. Calculate the operand address.

- 5. Fetch the operand.

- Add.

- 7. Store the answer.

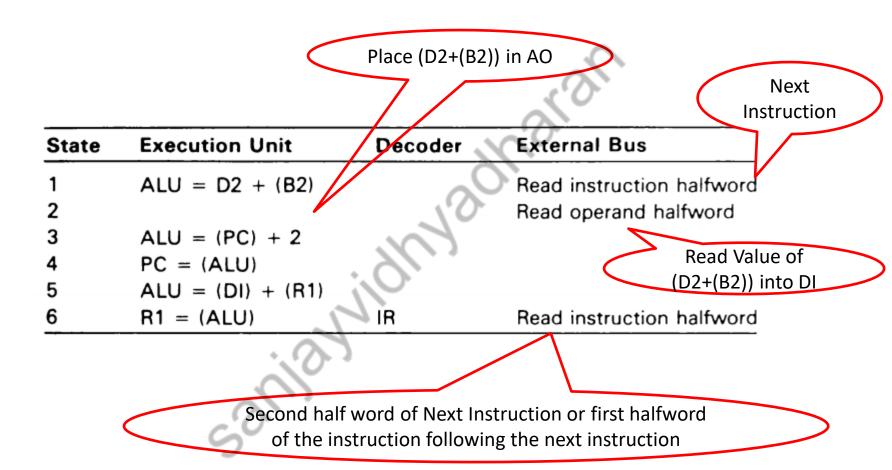

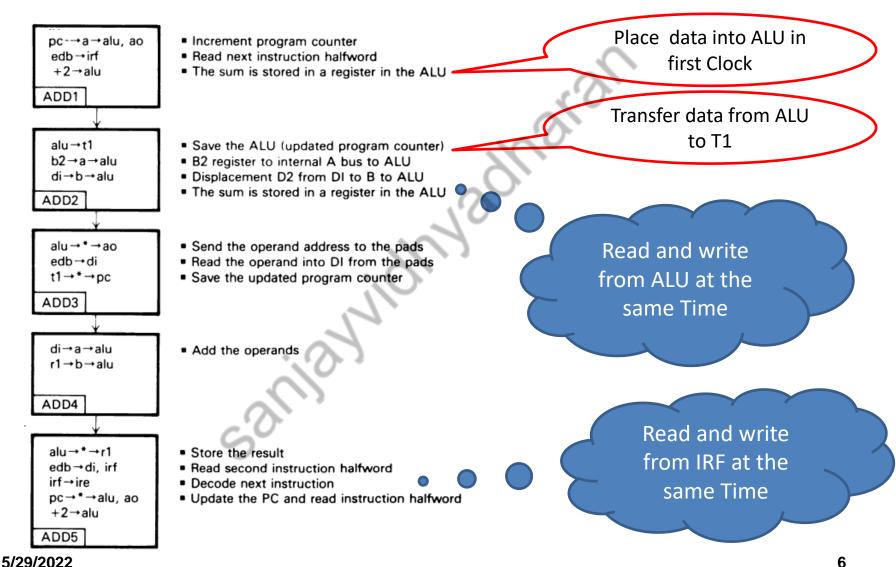

# **ADD Instruction Timing State**

# **ADD Instruction Execution with No Overlap**

#### **ADD R1, D2 (B2)**

| From | IRI |  |

|------|-----|--|

|------|-----|--|

| State | Execution Unit    | Decoder | External Bus                 |

|-------|-------------------|---------|------------------------------|

| 1     |                   |         | Read instruction halfword    |

| 2     | ALU = D2 + (B2)   | 1,0     | )*                           |

| 3     |                   | 103     | Read operand halfword        |

| 4     | ALU = (DI) + (R1) | :(0)    |                              |

| 5     | R1 = (ALU)        | 17/     | ALU data D2+(B2) placed in A |

| 6     | ALU = (PC) + 2    | P       | Read Value of into DI        |

| 7     | PC = (ALU)        | 0. 4    |                              |

| 8     |                   |         | Read instruction halfword    |

| 9     | 50                | IR      |                              |

#### **ADD Instruction Execution with Overlap**

## **ADD Instruction Timing State**

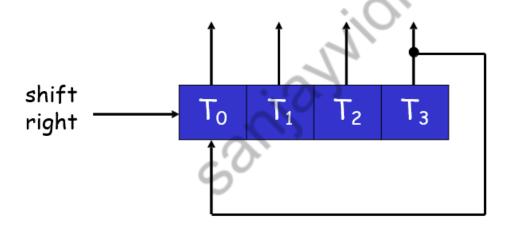

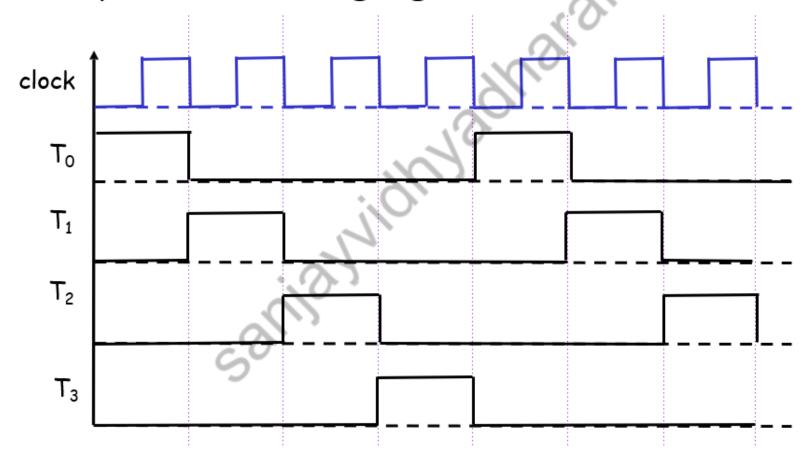

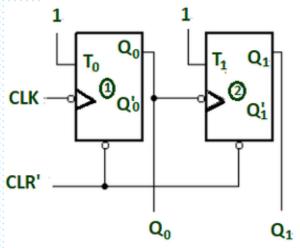

#### Ring Counter

- Timing signals control the sequence of operations in a digital system

- A ring counter is a circular shift register with only one flip-flop being set at any particular time, all others are cleared.

initial value 1000

Sequence of timing signals

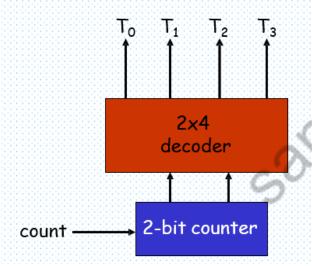

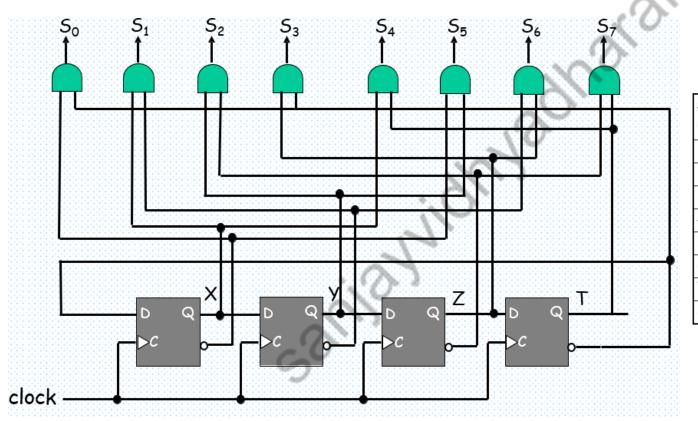

#### Counter with Decoder

- To generate 2<sup>n</sup> timing signals,

- we need a shift register with 2<sup>n</sup> flip-flops

- or, we can construct the ring counter with a binary counter and a decoder

#### <u>Cost</u>:

- ·2 flip-flop

- ·2-to-4 line decoder

- Cost in general case:

- · n flip-flops

- · n-to-2<sup>n</sup> line decoder

- 2<sup>n</sup> n-input AND gates

#### Johnson Counter

| sequence | Flip-flop outputs |   |   |   |  |

|----------|-------------------|---|---|---|--|

| number   | X                 | У | Z | T |  |

| 1        | 0                 | 0 | 0 | 0 |  |

| 2        | 1                 | 0 | 0 | 0 |  |

| 3        | 1                 | 1 | 0 | 0 |  |

| 4        | 1                 | 1 | 1 | 0 |  |

| 5        | 1                 | 1 | 1 | 1 |  |

| 6        | 0                 | 1 | 1 | 1 |  |

| 7        | 0                 | 0 | 1 | 1 |  |

| 8        | 0                 | 0 | 0 | 1 |  |

|          |                   |   |   |   |  |

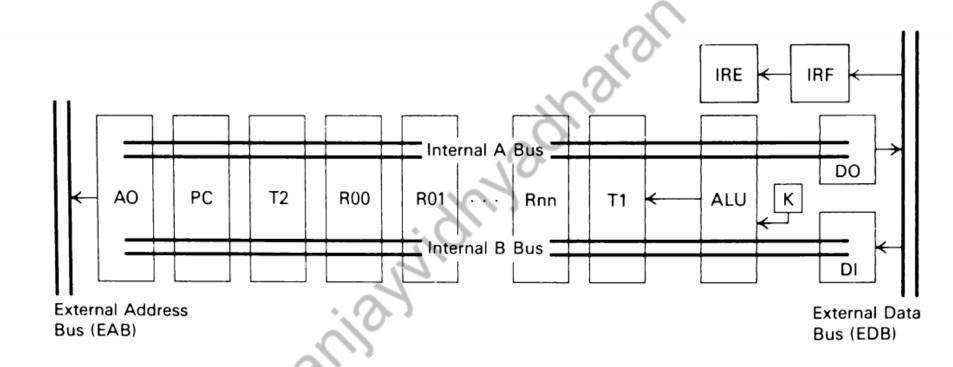

- > During phase 1, the source register is gated to the internal bus.

- ➤ During phase 2, the signal on the internal bus is amplified and broadcast the length of the bus.

- ➤ During phase 3, the signal on the internal bus is gated to the destination.

- ➤ In phase 4, the bus is returned to a neutral state.

5/29/2022

INSTRUMENTATION

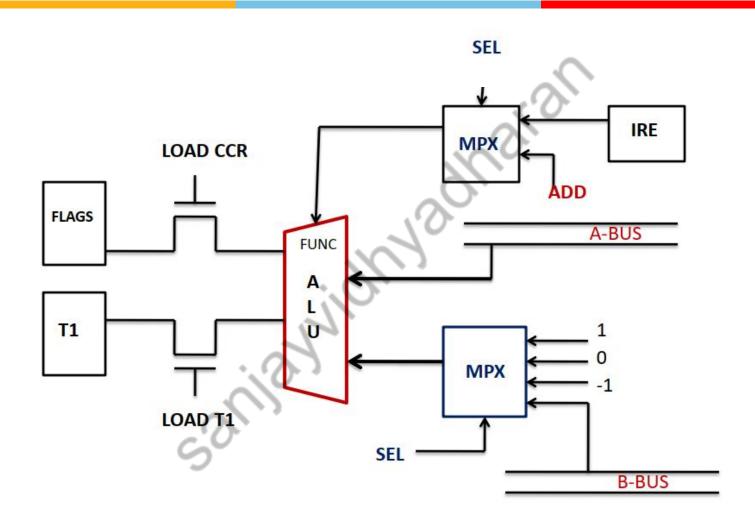

In state ADD1,

The PC will reach AO at phase 3.

AO is the buffer that drives the pads.

The instruction returned by the memory on the EDB will arrive at phase 4 or (some) phase 4 prime.

In ADD2,

The value being saved in T1 is the updated PC. The ALU-to-T1 transfer must be a phase 1 transfer. It will take 3 phases for data from b2 and di to reach ALU

In ADD3,

PC is updated with T1.

T1 not loaded with ALU.

In state ADD4,

The register Dl and the register designated by the R1 field of instruction are gated to buses B and A, respectively, during phase 1.

During phase 2, the contents of the registers are amplified and broadcast down the bus.

During phase 3, the inputs to the ALU are opened, and the ALU begins to operate.

During phase 4, the result of the ALU operation is saved in the ALU output register, and the resulting condition codes are sent to the condition code register.

15

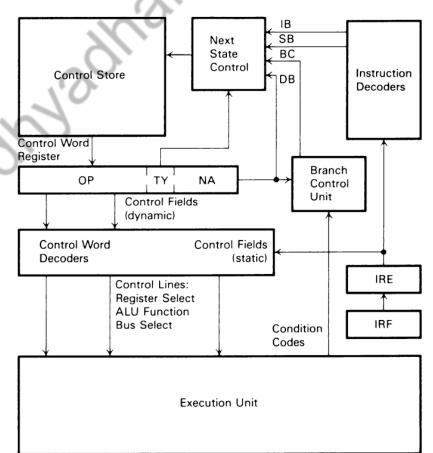

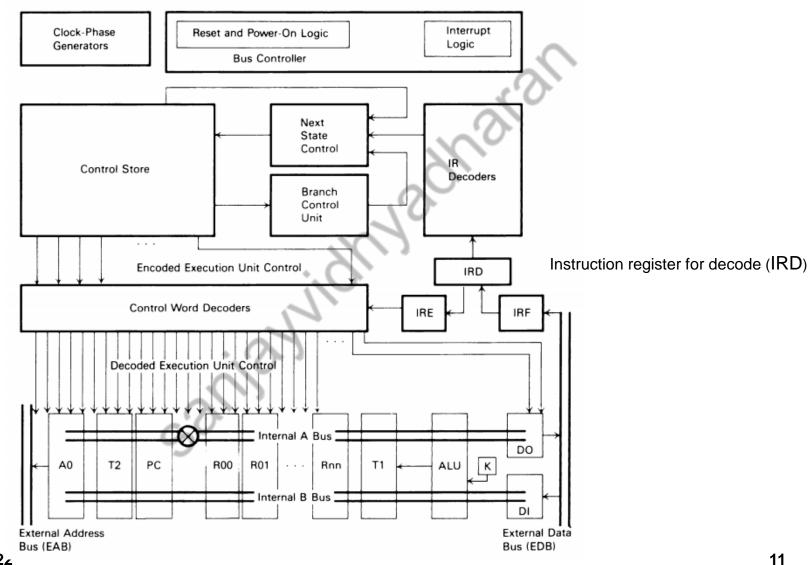

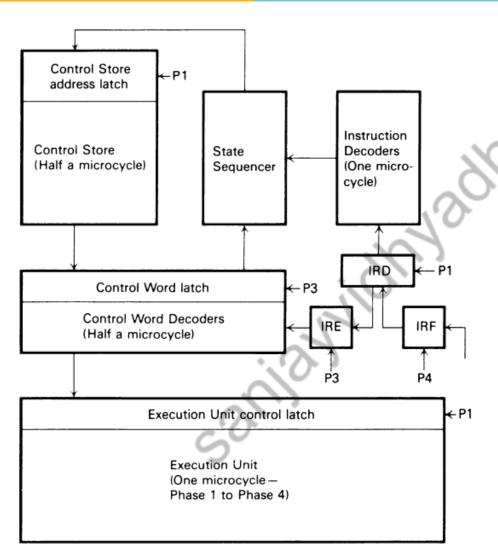

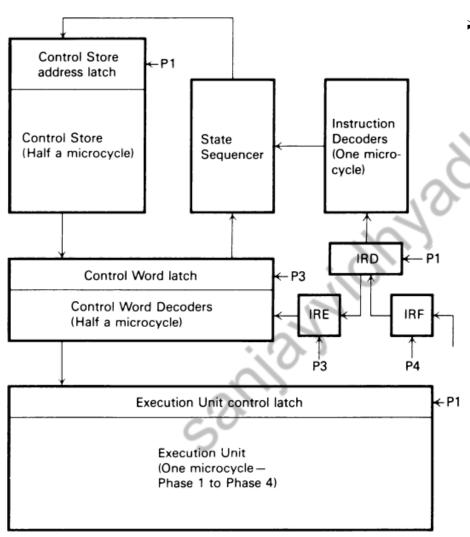

- ➤ The execution unit operates on a four-phase clock.

- ➤ A microcycle is one sequence of the four clock phases.

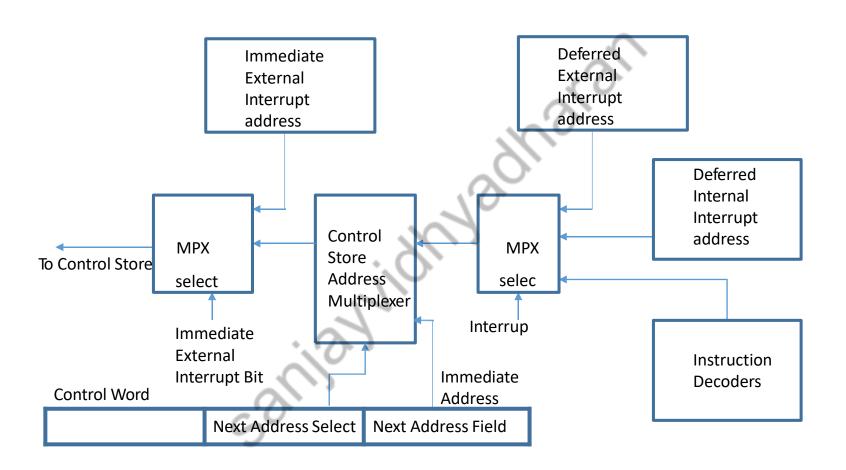

- The instruction decoders take one microcycle, and the control store takes half a microcycle. The control word decoders also take half a microcycle.

- ➤ Output of the control word decoders must be from the beginning of phase 1 through the end of phase 4

- ➤ Control Store and Control word decoder require 1 micro-cyle hence control store address latch should be latched beginning of phase 1.

Since the IR decoders take one microcycle, their input must be available at phase-1 two microcycles before the execution unit is to operate. When we fetch an instruction, it is loaded into the IRF on phase 4. At the next phase-1, we could load the IRE and begin instruction decoding.

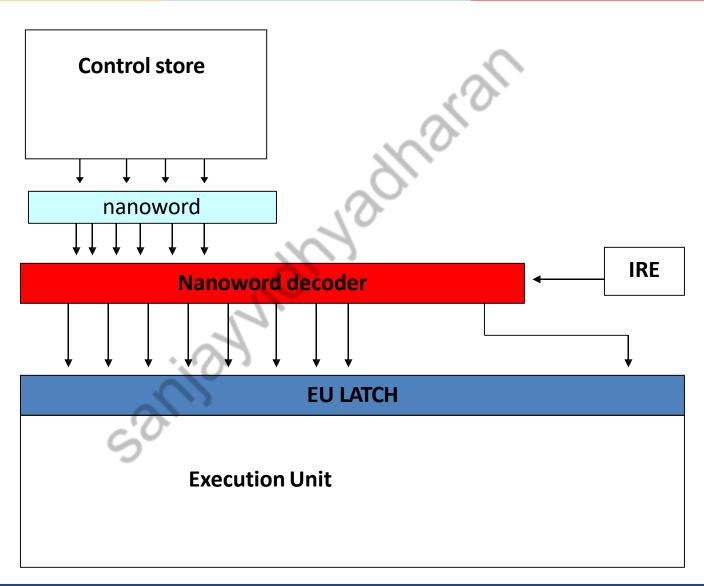

#### **Two-level control store (organization)**

#### Motorola MC68000

Microword output 16:1 MUX M rows of 16 words Microword store 18 bits per word address decoder N rows of 4 words Nanoword store 72 bits per word Nanoword output 4:1 MUX

#### **Two-level control store (organization)**

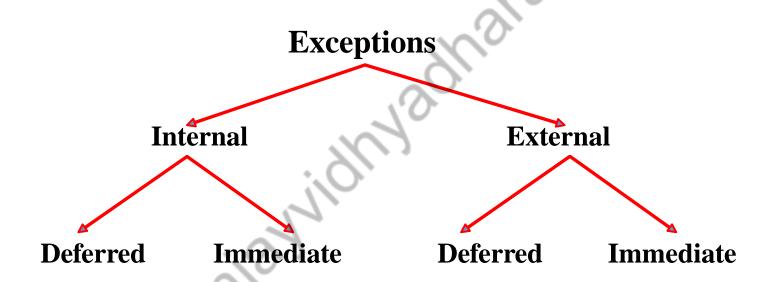

#### **Exceptions**

Anything that isn't a valid instruction is an Exception.

#### **Exceptions**

#### **Interrupts**

An interrupt is a request for a change in the normal instruction sequence. From the microprocessor's view, there are two kinds of interrupts.

One kind comes from inside the chip (internal interrupts), and the other kind comes from outside the chip (external interrupts)

The following might cause an internal interrupt fixed-point overflow divide-by-zero trace

These conditions might cause an external interrupt: bus error peripheral (chip) service request reset request power-on test request

#### **Exceptions**

Thank you