VLSI Design: 2021-22

Lecture 16

Arithmetic Circuits: Part-1

By Dr. Sanjay Vidhyadharan

ELECTRICAL

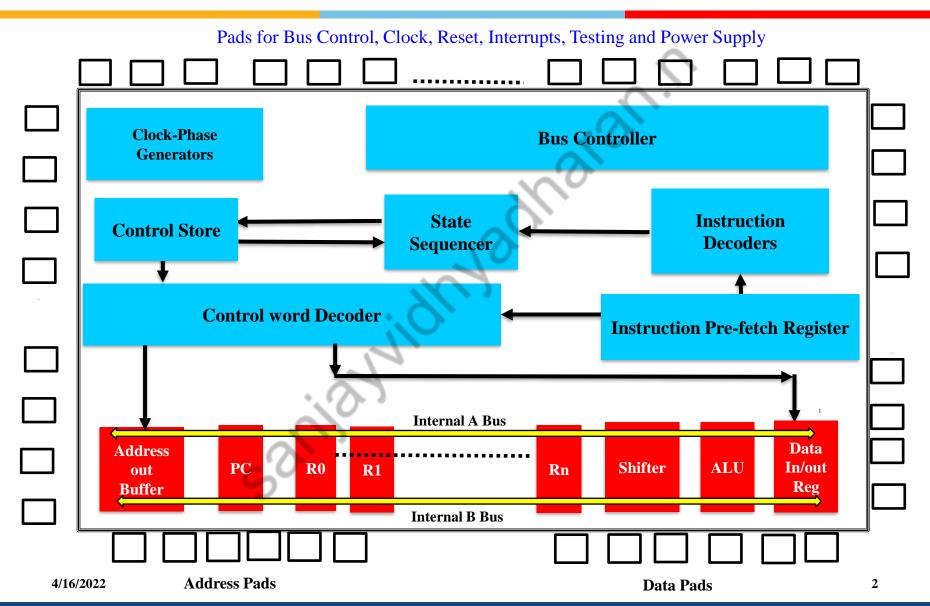

# Microprocessor Design

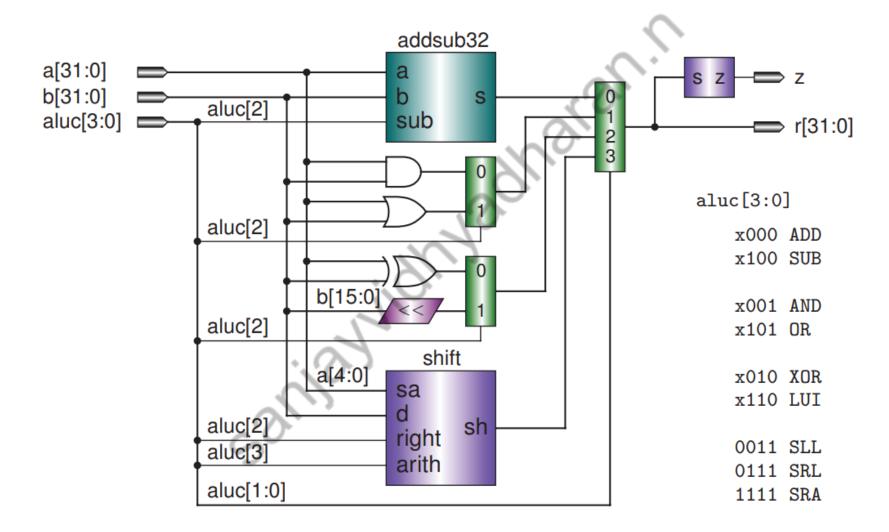

# **ALU Design**

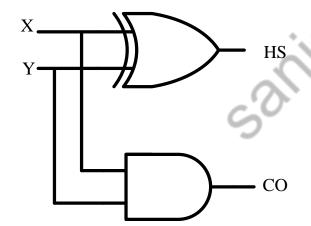

#### Half Adder

| Inp | outs | Out   | put |

|-----|------|-------|-----|

| A   | В    | Carry | Sum |

| o   | 0    | 0     | 0   |

| o   | 1    | 0     | 1   |

| 1   | 0    | 0     | 1   |

| 1   | 1    | 1     | 0   |

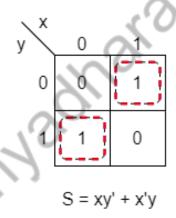

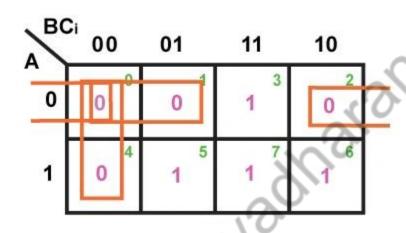

#### K-map for Sum

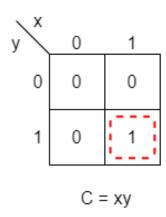

#### K-map for Carry

$$Sum = X \cdot Y' + X' \cdot Y = X \bigoplus Y$$

$$Carry = X \cdot Y$$

Time Delay for the Half Adder?

1 gate delay

A gate delay of an xor for the half sum

A gate delay of an AND gate for the carry out

#### **Full Adder**

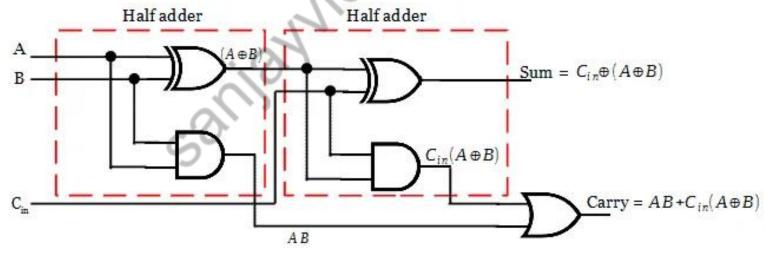

#### Full-adder can also implemented with two half adders and one OR gate.

$$\begin{split} S &= A \oplus B \oplus C_{in} \\ C_{out} &= AB + BC_{in} + AC_{in} \\ &= AB + C_{in} (A+B) \\ &= AB + C_{in} (A \oplus B+AB) \\ &= AB + C_{in} (A \oplus B) + C_{in} AB = AB(1+C_{in}) + C_{in} (A \oplus B) \\ &= AB + C_{in} (A \oplus B) \end{split}$$

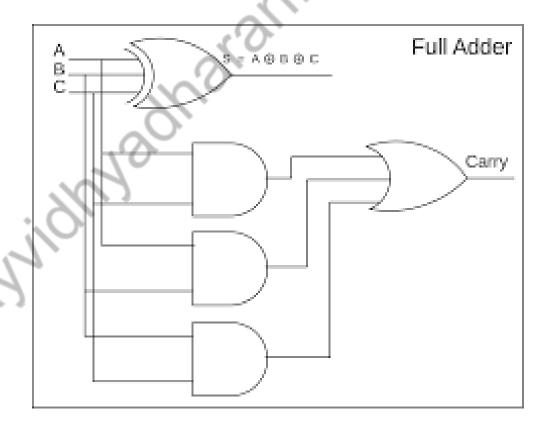

#### **Full Adder**

| A | В | Carry<br>In | Sum | Carry<br>out |

|---|---|-------------|-----|--------------|

| 0 | 0 | 0           | 0   | 0            |

| 0 | 0 | 1           | 1   | 0            |

| 0 | 1 | 0           | 1   | 0            |

| 0 | 1 | 1           | 0   | 1            |

| 1 | 0 | 0           | 1   | 0            |

| 1 | 0 | 1           | 0   | 1            |

| 1 | 1 | 0           | 0   | 1            |

| 1 | 1 | 1           | 1   | 1 (          |

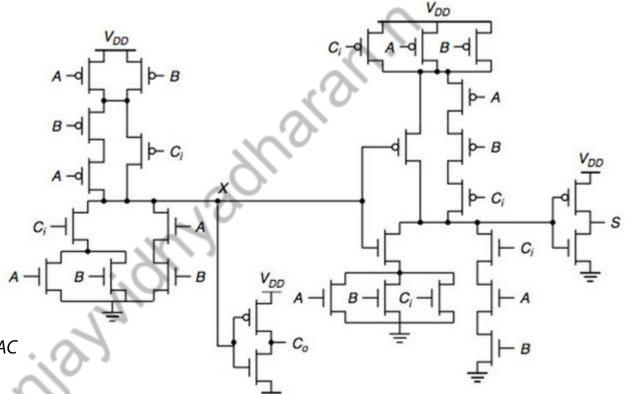

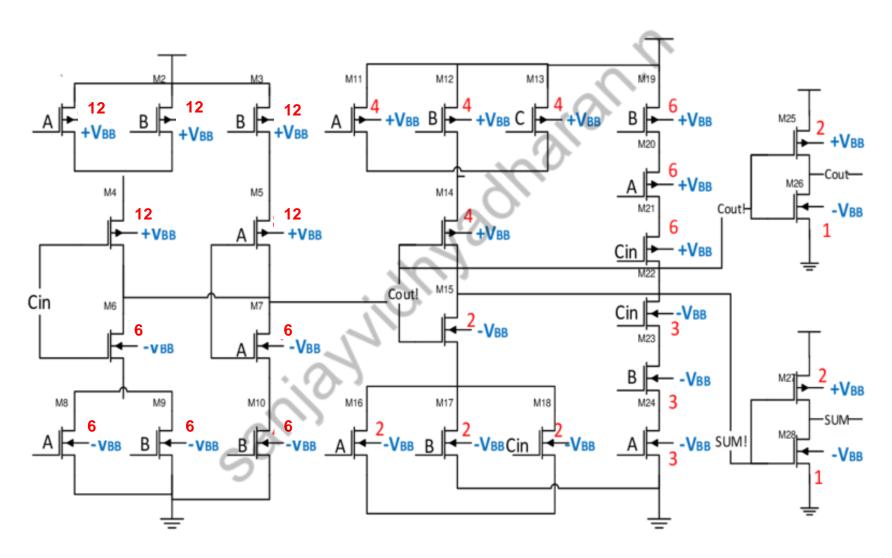

#### **CMOS 28T Adder**

| A | В | Carry<br>In | Sum | Carry<br>out |

|---|---|-------------|-----|--------------|

| 0 | 0 | 0           | 0   | 0            |

| 0 | 0 | 1           | 1   | 0            |

| 0 | 1 | 0           | 1   | 0            |

| 0 | 1 | 1           | 0   | 1            |

| 1 | 0 | 0           | 1   | 0            |

| 1 | 0 | 1           | 0   | 1            |

| 1 | 1 | 0           | 0   | 1            |

| 1 | 1 | 1           | 1   | 1            |

$$\mathit{Carry}(\mathit{CY}) = \mathit{AB} + \mathit{BC} + \mathit{AC}$$

$$Sum(S) = \bar{A}\bar{B}C + A\bar{B}\bar{C} + \bar{A}B\bar{C} + ABC$$

$$CY = AB + C(A + B)$$

Simplified

$S = \overline{CY}(A + B + C) + ABC$  Expressions

#### **CMOS 28T Mirror Adder**

$$Carry = AB + BC + CA = AB + C(A + B)$$

$Pull - Down \ Network \ for \ Carry \ Bar = AB + C(A + B)$

$$Pull-UP$$

Network for Carry  $Bar = A'B' + B'C' + C'A'$

=  $A'B' + C'(A' + B')$

#### **CMOS 28T Mirror Adder**

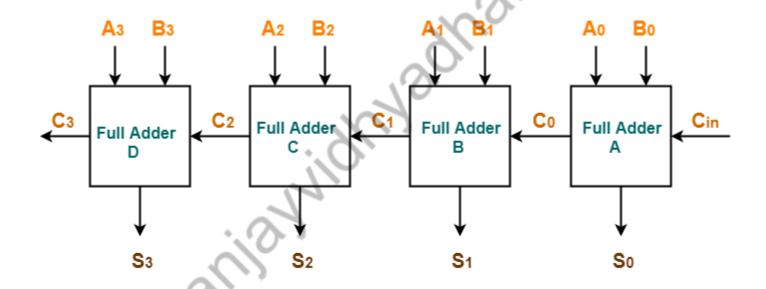

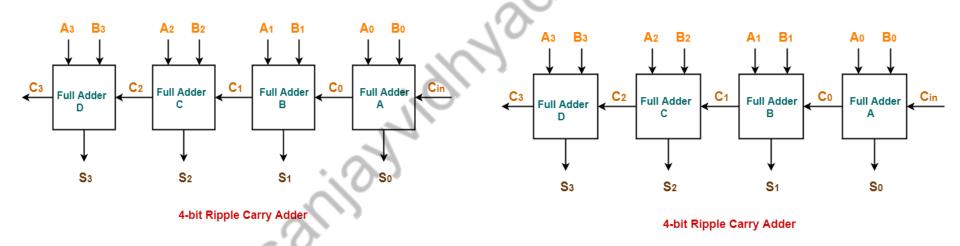

### Ripple Carry Adder

This is called Ripple Carry Adder, because of the construction with full adders are connected in cascade.

4-bit Ripple Carry Adder

Delay= 4 X Full Adder Delay = 8 Gate Delays

Delay=

$$(N-1) t_{carry} + t_{sum}$$

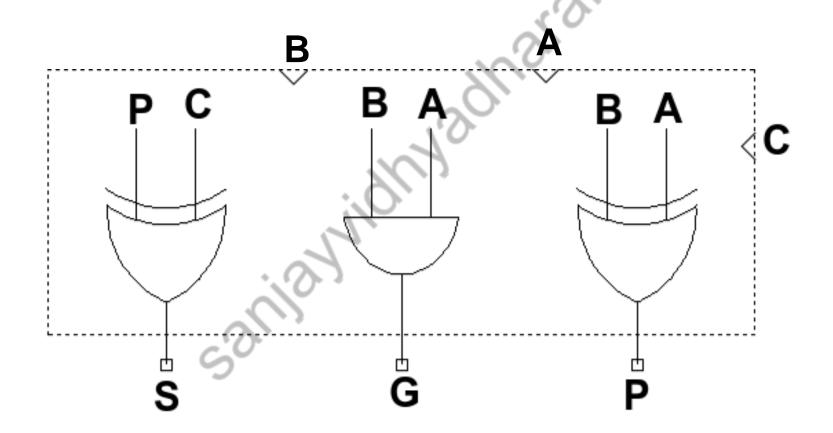

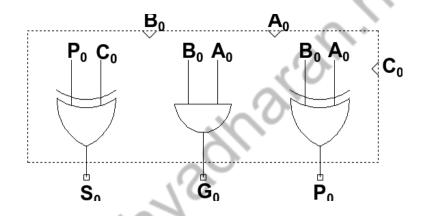

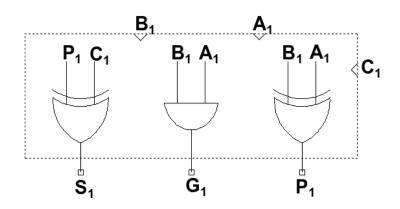

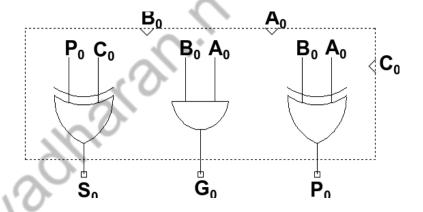

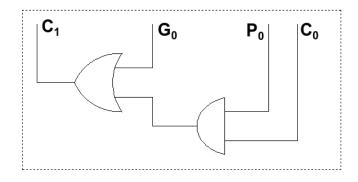

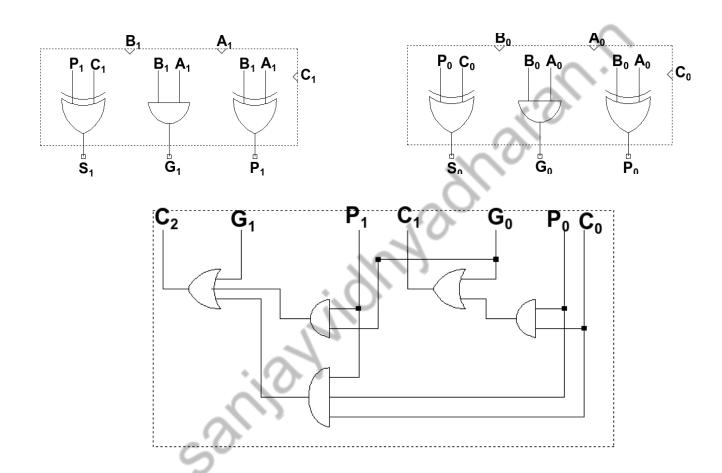

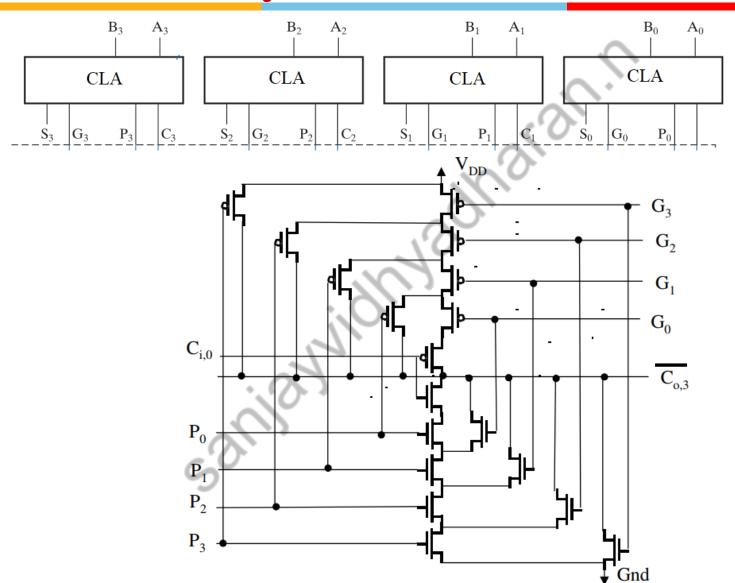

#### 1-bit CLA

**CLLB**

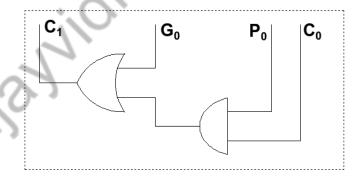

$$C_1 = G_0 + P_0 C_0$$

$$C_2 = G_1 + P_1 C_1$$

$$C_2 = G_1 + P_1 C_1$$

$$C_2 = G_1 + P_1 (G_0 + P_0 C_0)$$

$$= G_1 + P_1 G_0 + P_1 P_0 C_0$$

$$C_2 = G_1 + P_1 G_0 + P_1 P_0 C_0$$

$$C_1 = G_0 + P_0 C_0$$

$$C_1 = G_0 + P_0 C_0$$

$$C_2 = G_1 + P_1 G_0 + P_1 P_0 C_0$$

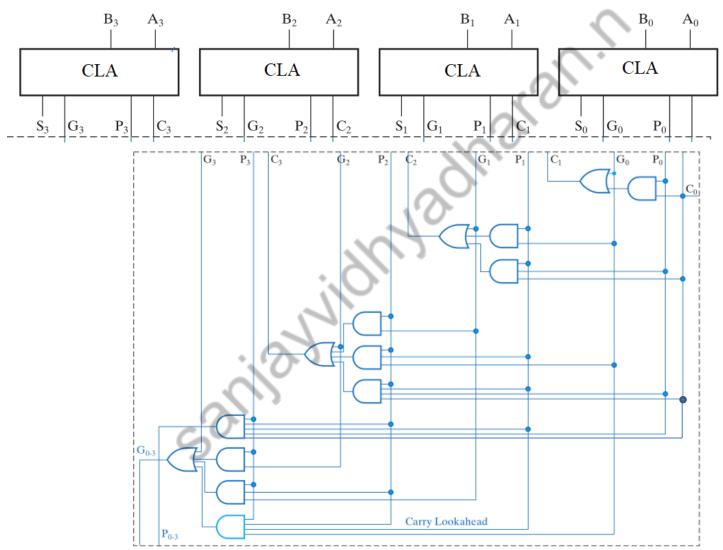

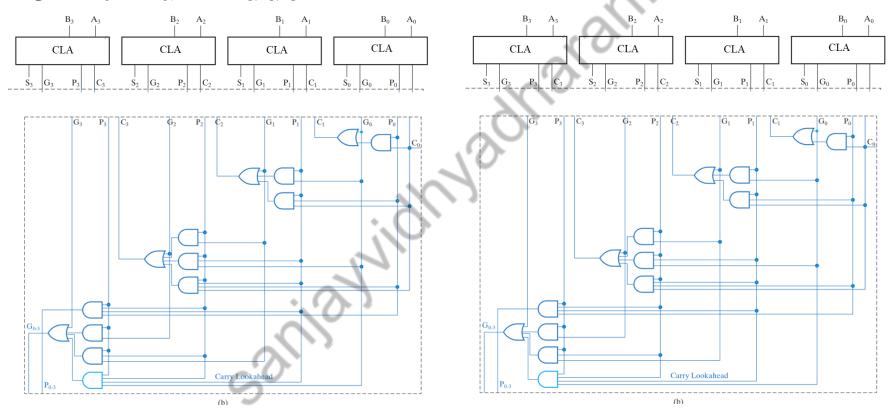

$$C_3 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$$

$$\begin{split} &C_{3} = G_{2} + P_{2}G_{1} + P_{2}P_{1}G_{0} + P_{2}P_{1}P_{0}C_{0} \\ &C_{4} = G_{3} + P_{3}G_{2} + P_{3}P_{2}G_{1} + P_{3}P_{2}P_{1}G_{0} + P_{3}P_{2}P_{1}P_{0}C_{0} \end{split}$$

#### 8 Bit Full Adder

Delay = 2 X 3 = 6 Gate Delay

#### Ripple Carry Adder

#### 8 Bit Full Adder

Delay = 8 X 2 Gate Delay

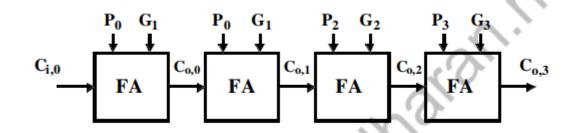

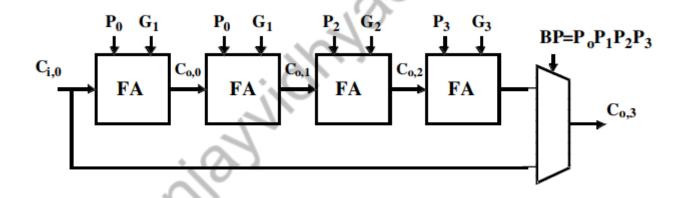

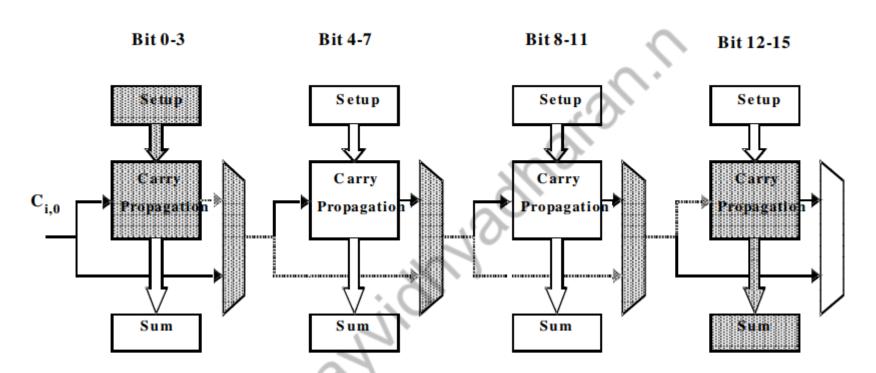

# Carry Bypass or Carry Skip Adder

# Carry Bypass or Carry Skip Adder

Design N-bit adder using N/M equal length stages e.g. N = 16, M = 4

What is the critical path?

$$t_p = t_{\text{setup}} + Mt_{\text{carry}} + (N/M-1)t_{\text{bypass}} + Mt_{\text{carry}} + t_{\text{sum}}$$

, i.e. O(N)

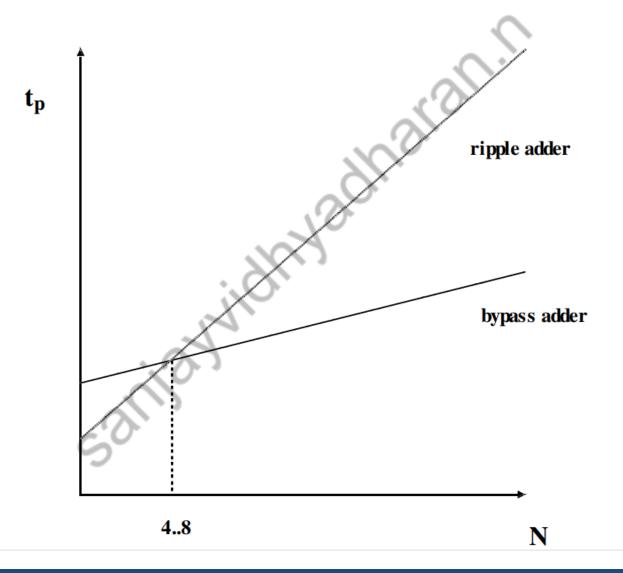

# Carry Ripple versus Carry Bypass

22

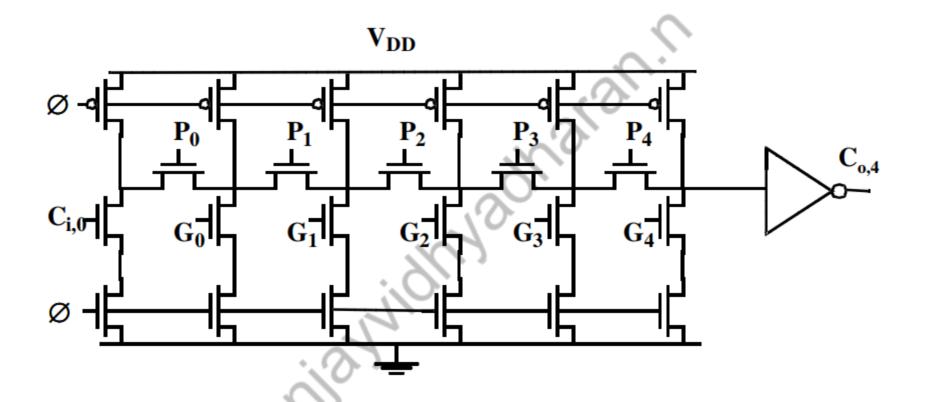

### **Manchester Carry Chain**

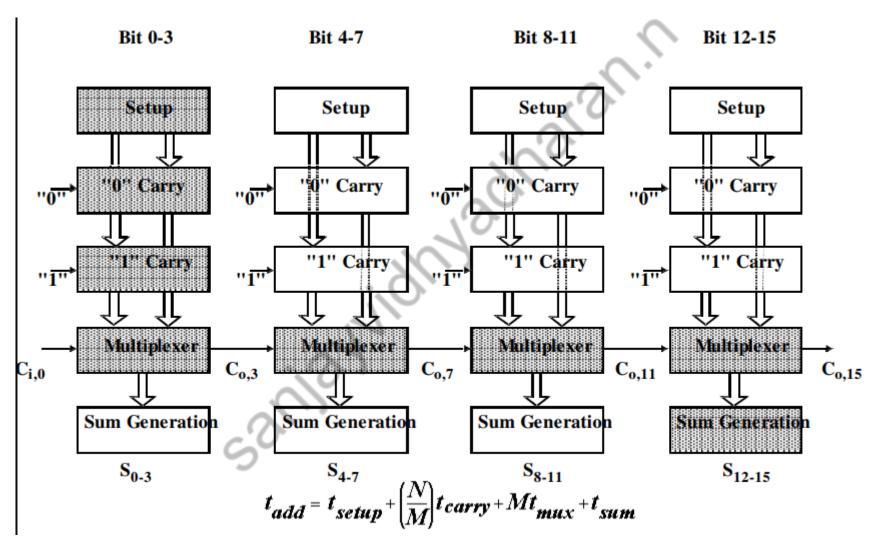

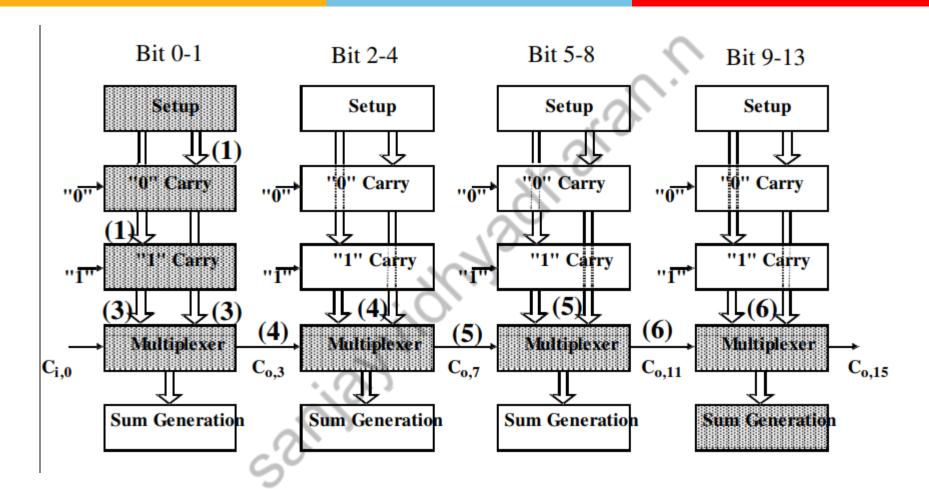

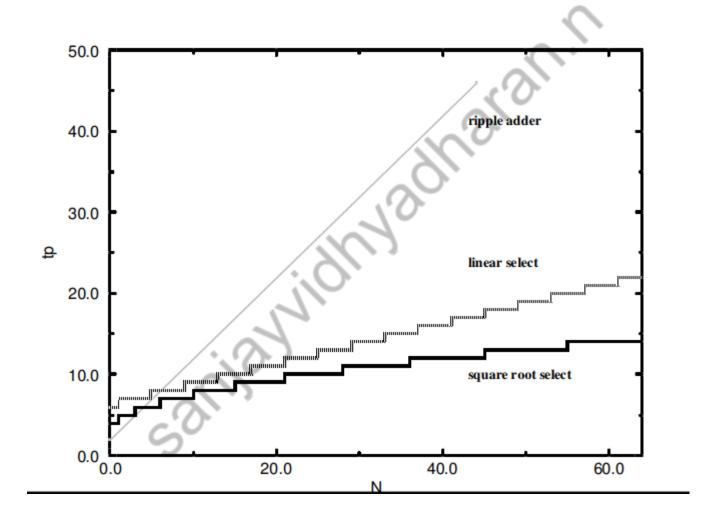

# Linear Carry-Select Adder

### Square Root Carry-Select Adder

$$t_{add} = t_{setup} + Mt_{carry} + (\sqrt{2N})t_{mux} + t_{sum}$$

# **Square Root Carry-Select Adder**

N Bit adder, M – Bits in First Stage, P – Number of Stages

$$N = M + (M+1) + (M+2) + (M+3) + \dots + (M+P-1)$$

$$N = MP + \frac{P(P-1)}{2}$$

$$N = \frac{P^2}{2} + P(M - \frac{1}{2})$$

$$M \ll N \ (e. M = 2 \ and \ N = 64)$$

$$N = \frac{P^2}{2} + P(M - \frac{1}{2})$$

$$M \ll N \ (e. M = 2 \ and \ N = 64)$$

$$N \approx \frac{P^2}{2}$$

# **Adder Delays - Comparison**

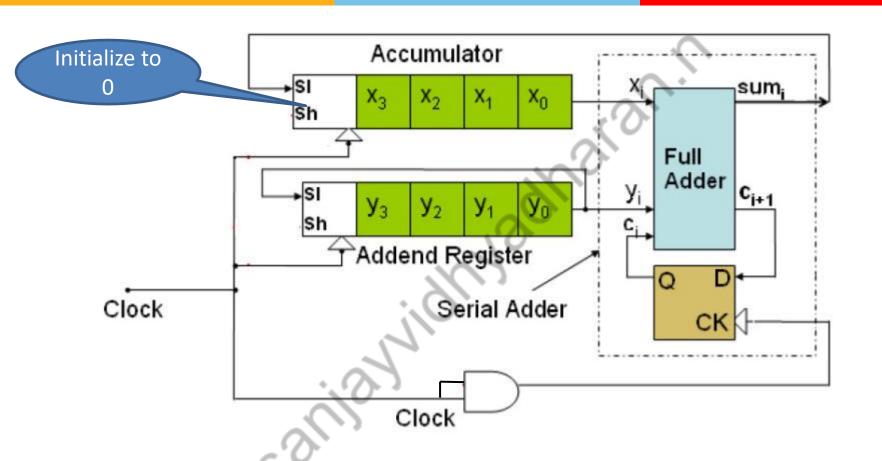

#### Serial Adder

Block Diagram of a 4-bit Serial Adder with Accumulator

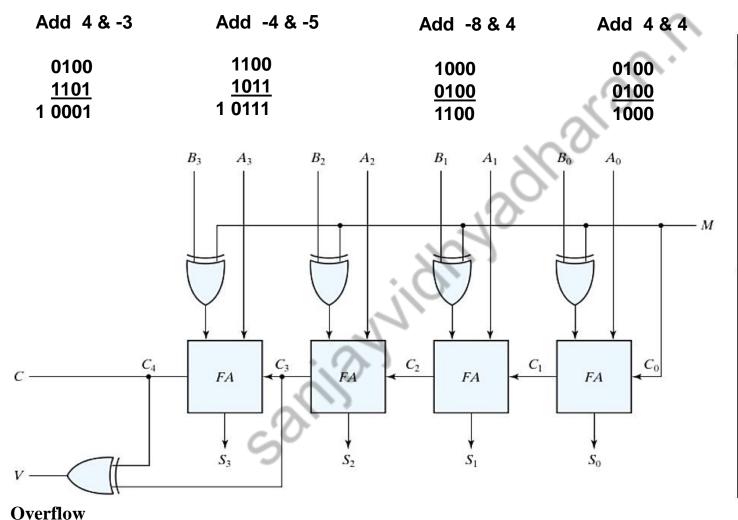

#### 4 Bit-Adder Subtractor

| Decimal | 2's comp. |

|---------|-----------|

| 7       | 0111      |

| 6       | 0110      |

| 5       | 0101      |

| 4       | 0100      |

| 3       | 0011      |

| 2       | 0010      |

| 1       | 0001      |

| 0       | 0000      |

| -0      | -         |

| -1      | 1111      |

| -2      | 1110      |

| -3      | 1101      |

| -4      | 1100      |

| -5      | 1011      |

| -6      | 1010      |

| -7      | 1001      |

| -8      | 1000      |

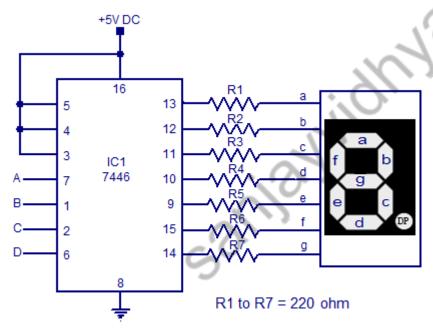

#### General digital systems

User enters decimal  $\rightarrow$  BCD i/p $\rightarrow$  Binary i/p $\rightarrow$  compute in binary  $\rightarrow$  Binary o/p $\rightarrow$  BCD o/p $\rightarrow$  Decimal output shown to user

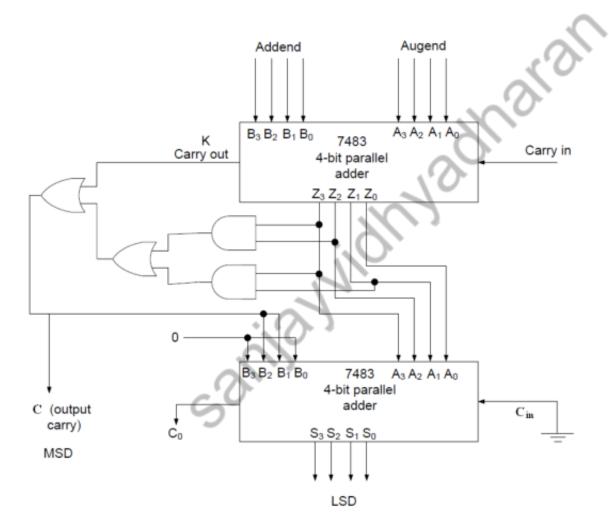

#### **BCD** addition

$$4 + 5$$

**Expected Result**

$$4 + 8$$

1 1 0 0 Is this expected Result?

Expected answer

0001 0010

is BCD of 12

#### **BCD** addition

$$4 + 8$$

Greater than 9

$$\boxed{100}$$

0110

Add correction of +6

$$0\ 0\ 0\ 1\ 0\ 0\ 1\ 0$$

#### **BCD** addition

After addition if carry out is generated or if sum is greater than 9 there is need for correction

#### **BCD** addition

1000

1001

Thank you