VLSI Design: 2021-22 Lecture 13 Domino Logic

By Dr. Sanjay Vidhyadharan

## **Dynamic Logic**

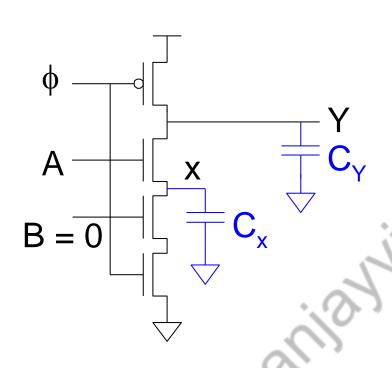

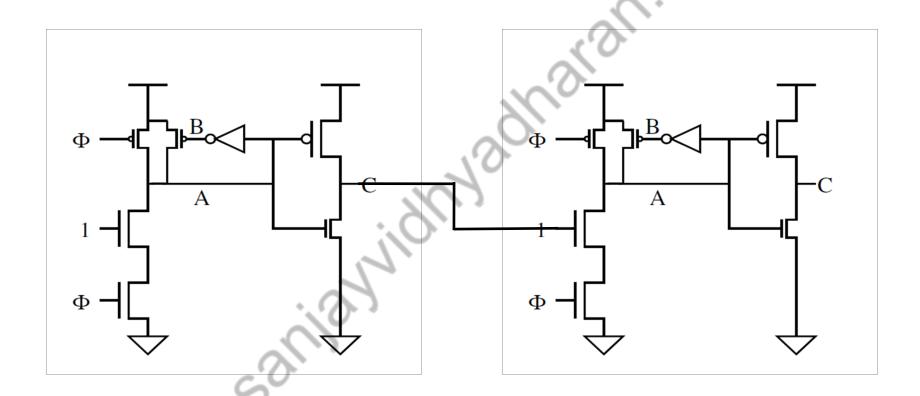

#### > Dynamic Logic Suffers from Charge Sharing Phenomenon

Case1.

$$\Delta V_{out} < V_{Tn} - V_{out}$$

$$V_{DD} \cdot C_Y = V_Y C_Y + (V_{DD} - V_{Tn}) C_X$$

$$\Delta V_{out} = -\frac{(V_{DD} - VT_n) C_X}{C_Y}$$

$$C_Y << C_Y$$

## **Dynamic Logic**

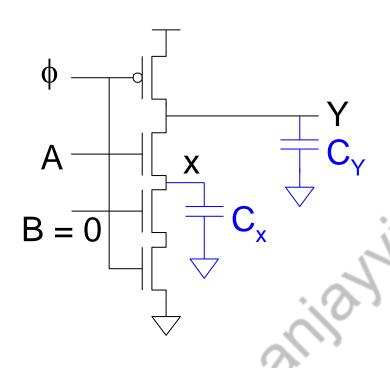

#### > Dynamic Logic Suffers from Charge Sharing Phenomenon

Case2.

$$\Delta V_{out} > V_{Tn} - V_{out}$$

$$V_{DD}.C_Y = V_Y C_Y + V_X C_X$$

$$V_{DD}.C_Y = V_Y C_Y + V_Y C_X$$

$$V_{DD}.C_Y = (V_{DD} + \Delta V_{out}) (C_Y + C_X)$$

$$\Delta V_{out} = -\frac{V_{DD}C_X}{C_{Y^+}C_X}$$

# **Dynamic Logic**

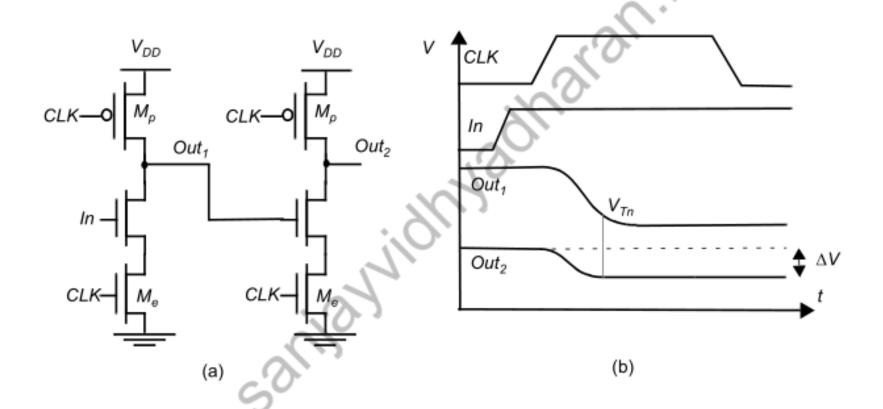

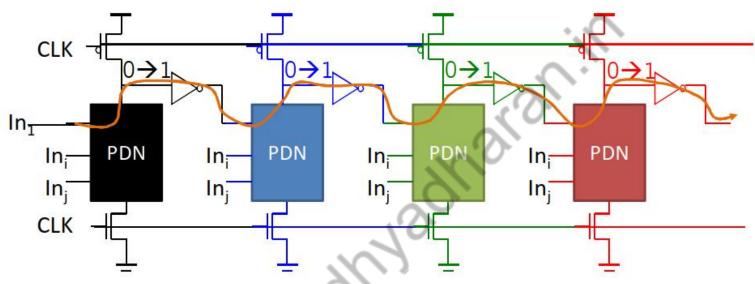

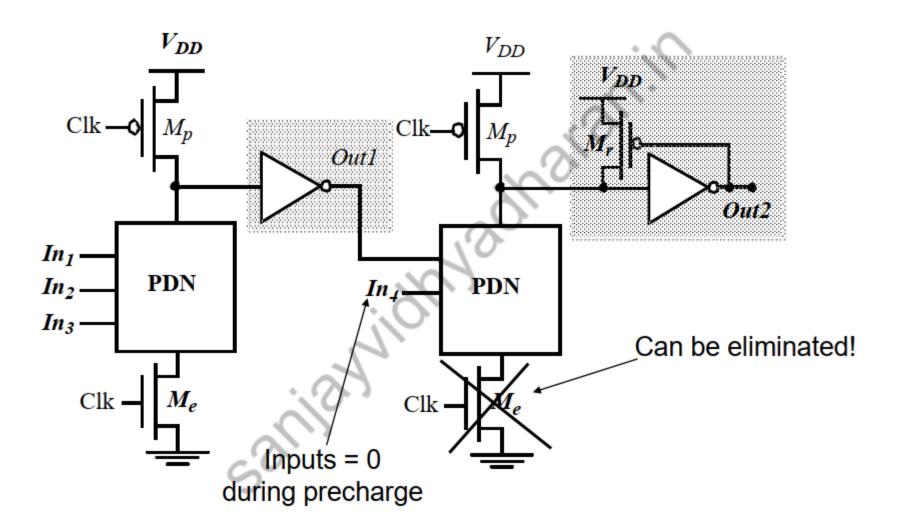

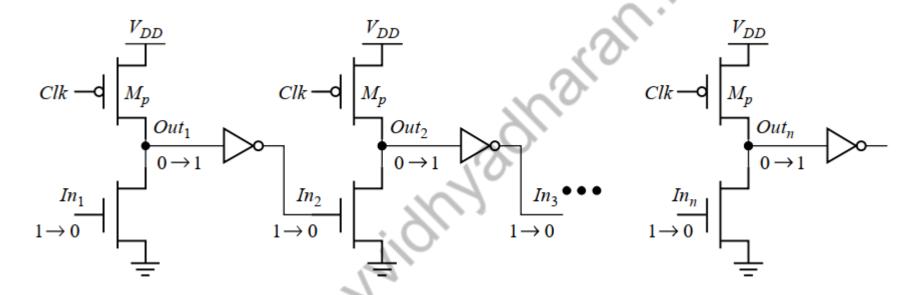

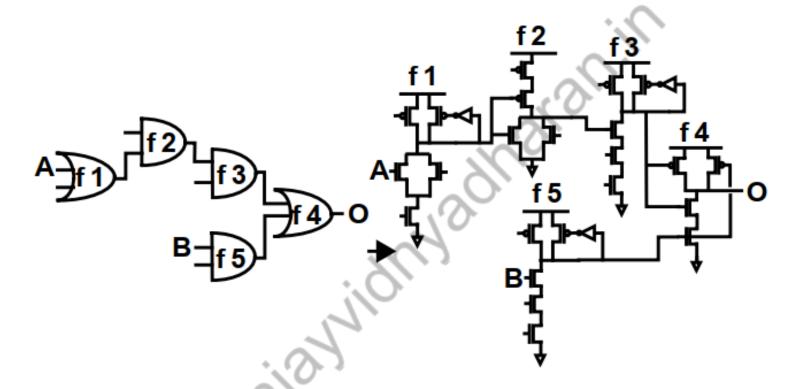

#### > Cascading Dynamic Gates

#### **Cascading Domino Logic**

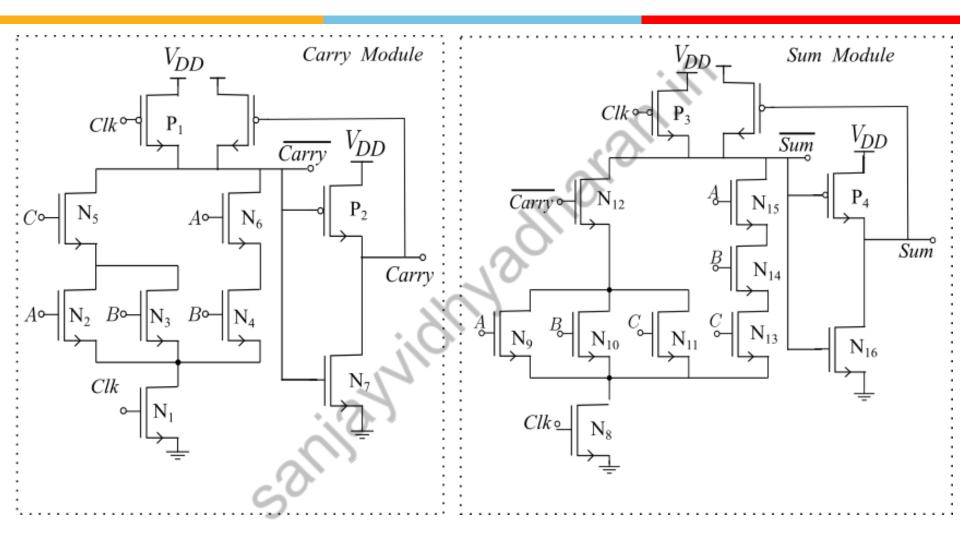

#### 22T Domino Full Adder

• Behave like falling dominos...

#### **Footless Domino**

Pre-charge is rippling – short-circuit current

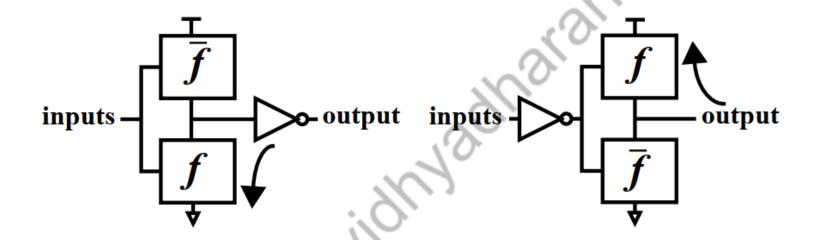

Domino cannot implement inverting switching functions, such as a NOT gate and an XOR gate

Forms for implementing a non-inverting function f

Domino cannot implement inverting switching functions, such as a NOT gate and an XOR gate

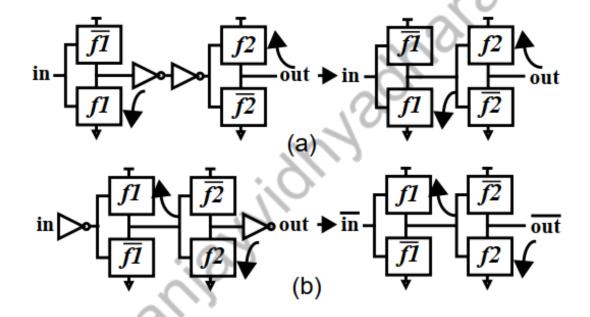

Merging of two non-inverting functions f1 and f2

However, generating a unate network from a random logic network may require logic duplication since both positive and negative signal phases may be needed.

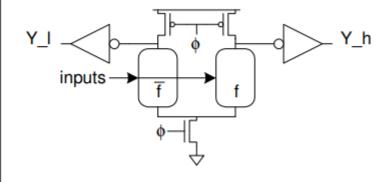

## **Dual-Rail Domino Logic**

- Domino only performs noninverting functions:

- AND, OR but not NAND, NOR, or XOR

- Dual-rail domino solves this problem

- Takes true and complementary inputs

- Produces true and complementary outputs

| sig_h | sig_l | Meaning     |

|-------|-------|-------------|

| 0     | 0     | Precharged  |

| 0     | 1     | <b>'</b> 0' |

| 1     | 0     | <b>'1'</b>  |

| 1     | P     | invalid     |

## Differential (Dual Rail) Domino

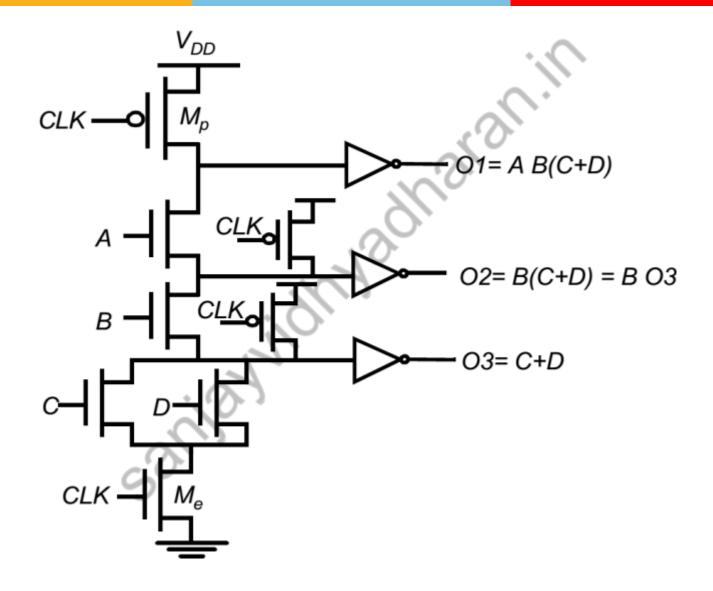

# **Multiple-Output Domino**

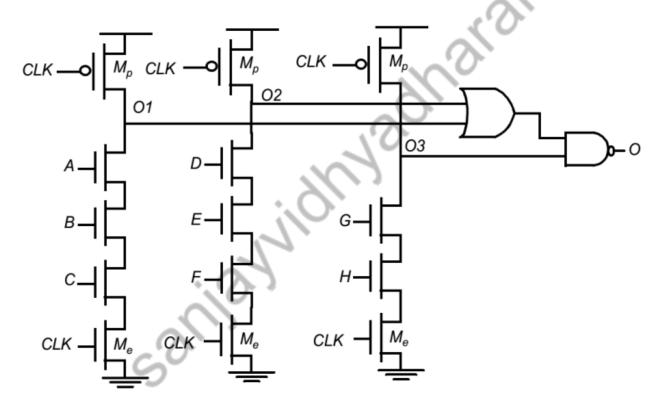

# **Compound Domino logic**

```

O = A B C D E F + GH.

O = ABC \cdot DEF + GH

O = \{ [(ABC)' + (DEF)']' \cdot (GH)' \}'

```

Large dynamic stacks are replaced by parallel structures with small fan-in and complex CMOS gates

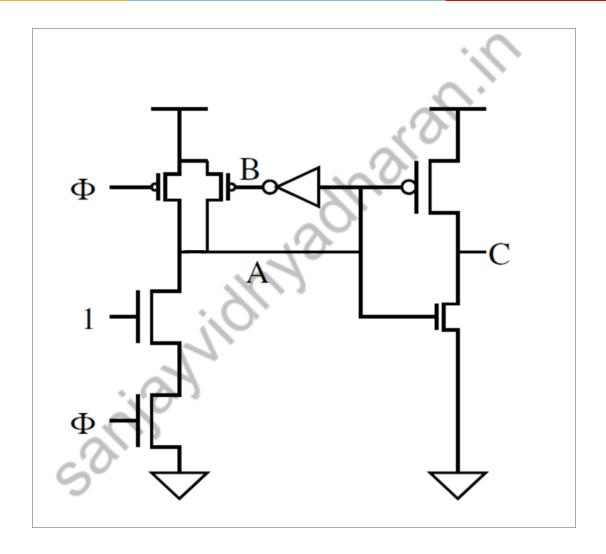

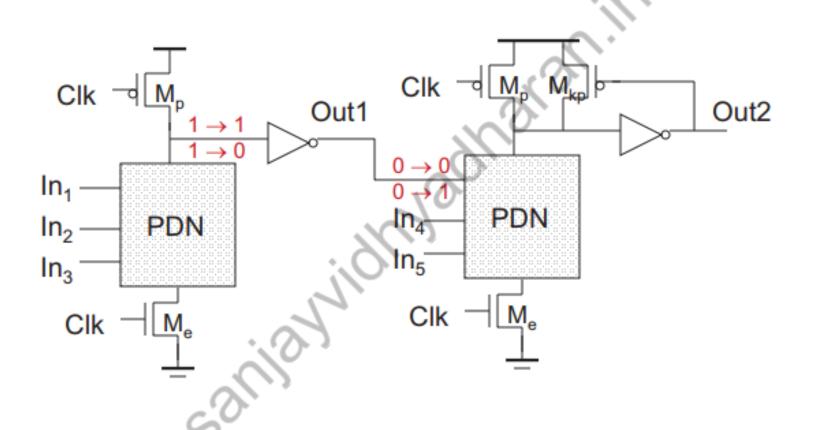

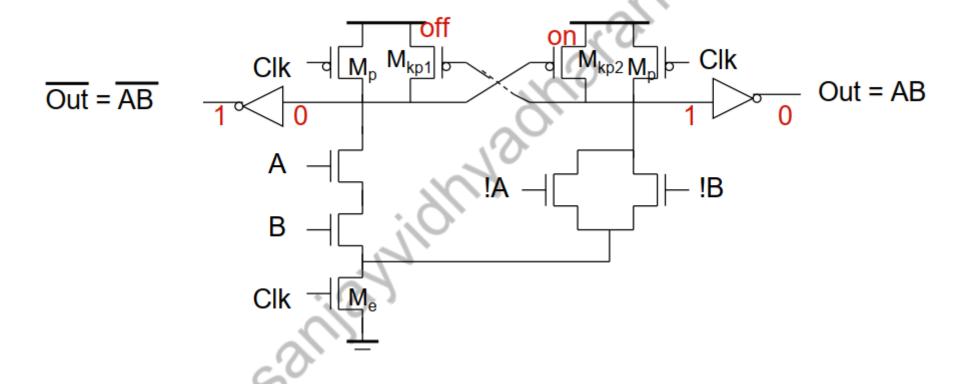

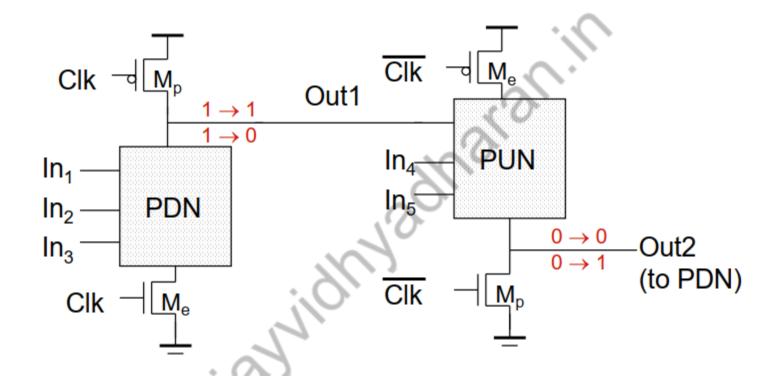

## np-CMOS

Only  $0 \rightarrow 1$  transitions allowed at inputs of PDN Only  $1 \rightarrow 0$  transitions allowed at inputs of PUN

A disadvantage of the *np*-CMOS logic style is that the *p*-tree blocks are slower than the *n*-tree modules, due to the lower current drive of the PMOS transistors in the logic network. Equalizing the propagation delays requires extra area.

# Thank you

4/3/2022