INSTRUMENTATION

# Advanced VLSI Design: 2021-22 Lecture 12-B: Low Power VLSI Design Part-2: Architecture, Algorithmic & RTL Level Optimization

By Dr. Sanjay Vidhyadharan

COMMUNICATION

ELECTRONICS

ELECTRICAL

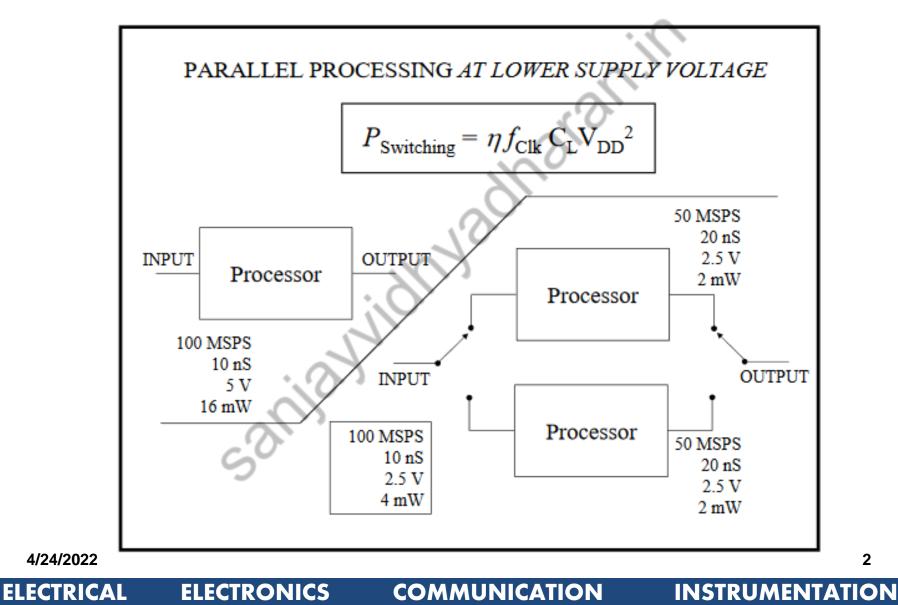

# **Architecture-Level Design – Parallelism**

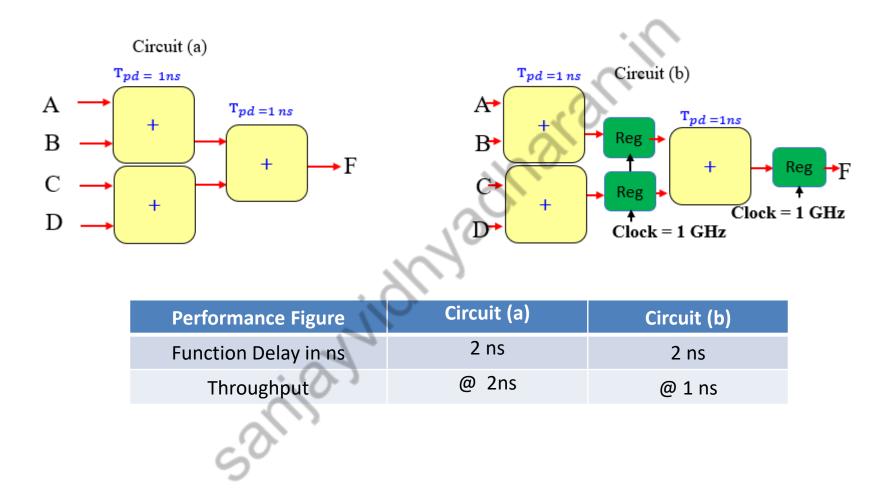

# **Architecture-Level Design – Pipelining**

4/24/2022

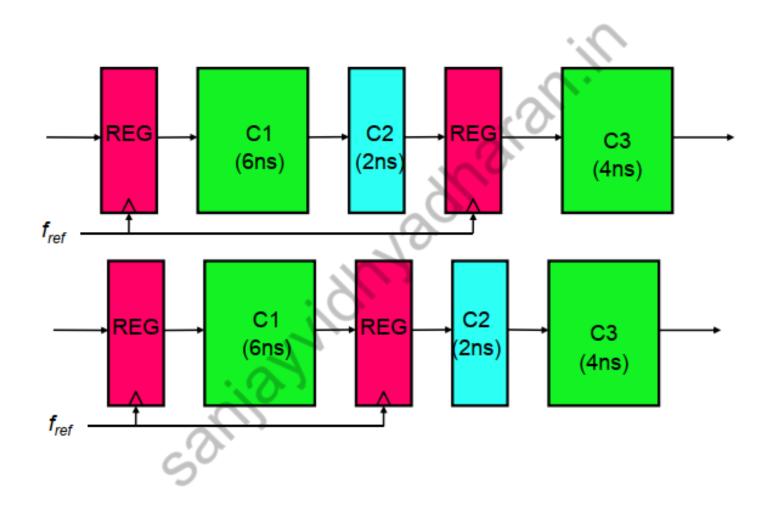

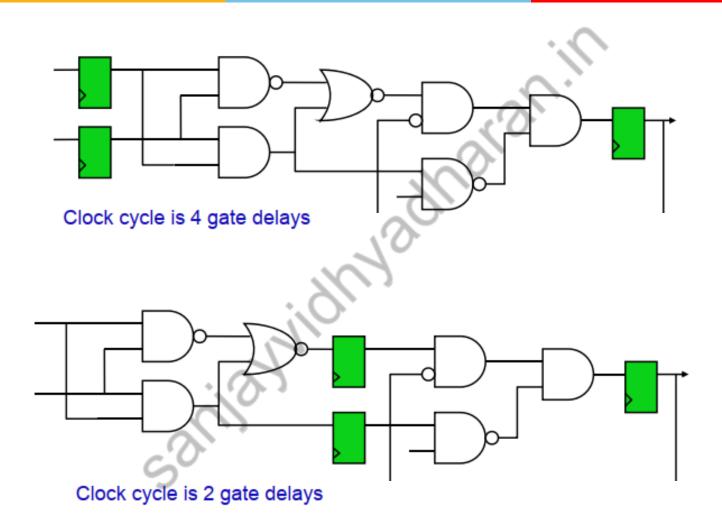

# **Architecture-Level Design – Retiming**

4/24/2022

COMMUNICATION

# **Architecture-Level Design – Retiming**

4/24/2022

ELECTRONICS

COMMUNICATION

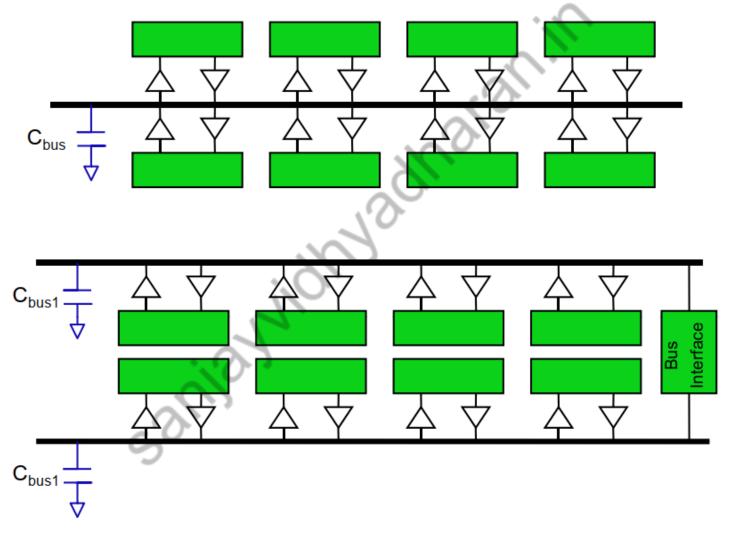

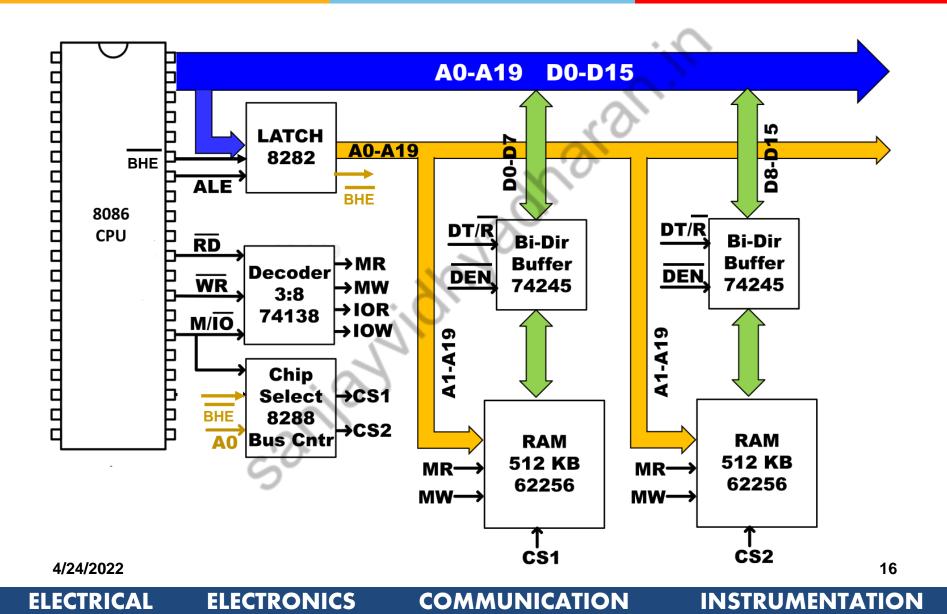

## **Architecture-Level Design – Bus Segmentation**

- Avoid the sharing of resources Reduce the switched capacitance

- For example: a global system bus

A single shared bus is connected to all modules, this structure results in a large bus capacitance due to

The large number of drivers and receivers sharing the same bus The parasitic capacitance of the long bus line

A segmented bus structure

Switched capacitance during each bus access is significantly reduced Overall routing area may be increased

4/24/2022

ELECTRICAL

### **Architecture-Level Design – Bus Segmentation**

4/24/2022

**ELECTRONICS**

COMMUNICATION

| <b>Binary Code</b> | Gray Code | Decimal Equivalent | 2.     |

|--------------------|-----------|--------------------|--------|

| 000                | 000       | 0                  | 1      |

| 001                | 001       | 1                  | $\sim$ |

| 010                | 011       | 2                  |        |

| 011                | 010       | 3                  |        |

| 100                | 110       | 40                 |        |

| 101                | 111       | 5                  |        |

| 110                | 101       | 6                  |        |

| 111                | 100       | 7                  |        |

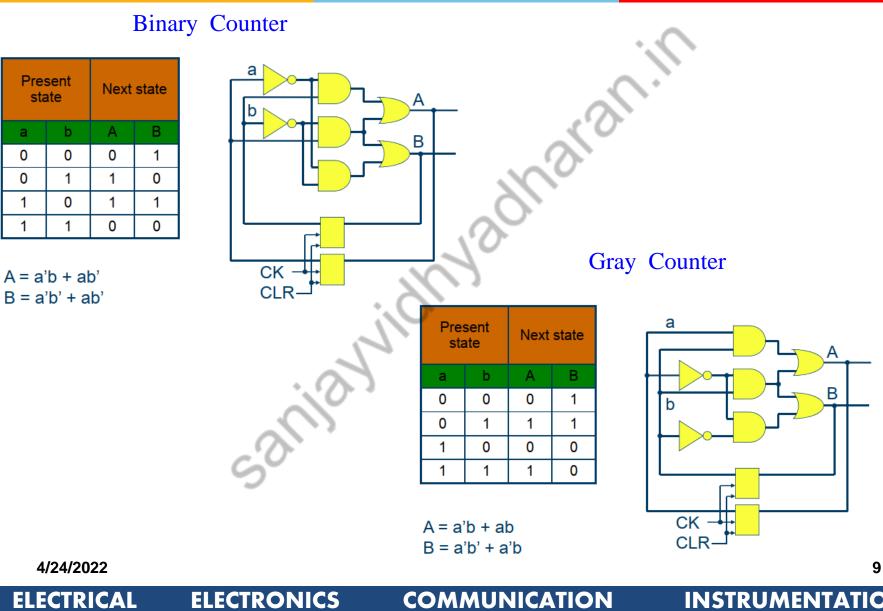

Two-bit binary counter:

State sequence,  $00 \rightarrow 01 \rightarrow 10 \rightarrow 11 \rightarrow 00$ Six bit transitions in four clock cycles 6/4 = 1.5 transitions per clock

• Two-bit Gray-code counter

ELECTRONICS

State sequence,  $00 \rightarrow 01 \rightarrow 11 \rightarrow 10 \rightarrow 00$ Four bit transitions in four clock cycles 4/4 = 1.0 transitions per clock

4/24/2022

COMMUNICATION

| Binary                       |                | Gray-code                 |                |

|------------------------------|----------------|---------------------------|----------------|

| State                        | No. of toggles | State                     | No. of toggles |

| 000                          | -              | 000                       |                |

| 001                          | 1              | 001                       | 1              |

| 010                          | 2              | 011                       | 1              |

| 011                          | 1              | 010                       | 1              |

| 100                          | 3              | 110                       | 1              |

| 101                          | 1 : 0          | 111                       | 1              |

| 110                          | 2              | 101                       | 1              |

| 111                          |                | 100                       | 1              |

| 000                          | 3              | 000                       | 1              |

| Av. Transitions/clock = 1.75 |                | Av. Transitions/clock = 1 |                |

| C                            | 0              |                           |                |

COMMUNICATION

4/24/2022

**ELECTRICAL**

**ELECTRONICS**

#### **N-Bit Counter: Toggles in Counting Cycle**

ELECTRONICS

Binary counter: T(binary) = 2(2<sup>N</sup> − 1)

Gray-code counter: T(gray) = 2<sup>N</sup>

T(gray)/T(binary) = 2<sup>N-1</sup>/(2<sup>N</sup> − 1) → 0.5

| Bits                                    | T(binary) | 🕽 T(gray) | T(gray)/T(binary) |

|-----------------------------------------|-----------|-----------|-------------------|

| 1                                       | 2         | 2         | 1.0               |

| 2                                       | 9         | 4         | 0.6667            |

| 3                                       | 14        | 8         | 0.5714            |

| 4                                       | 30        | 16        | 0.5333            |

| 5                                       | 62        | 32        | 0.5161            |

| 6                                       | 126       | 64        | 0.5079            |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | -         | -         | 0.5000            |

COMMUNICATION

4/24/2022

ELECTRICAL

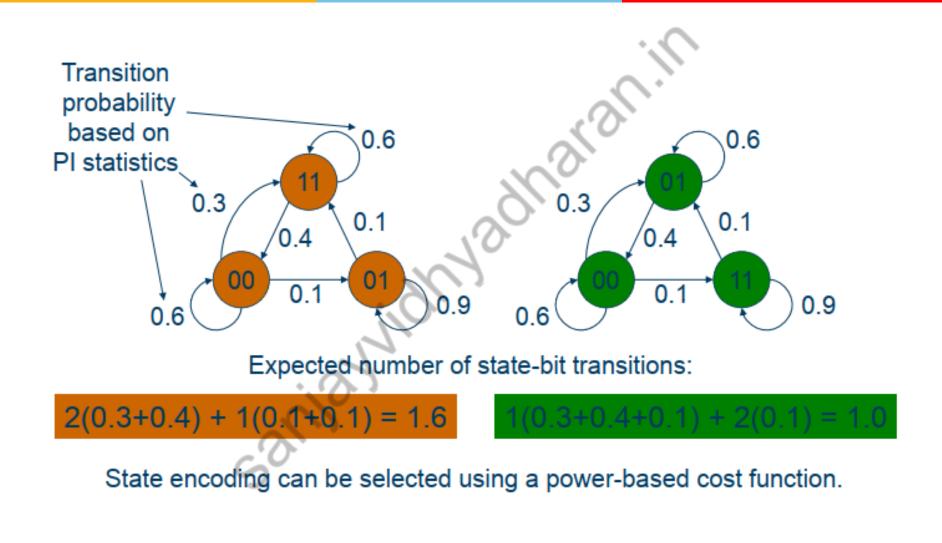

## **FSM State Encoding**

COMMUNICATION

4/24/2022

**ELECTRICAL**

**ELECTRONICS**

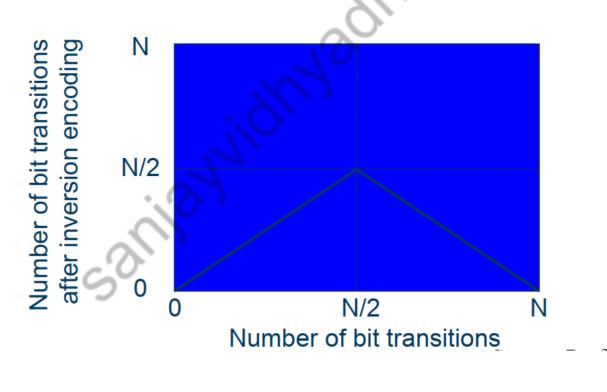

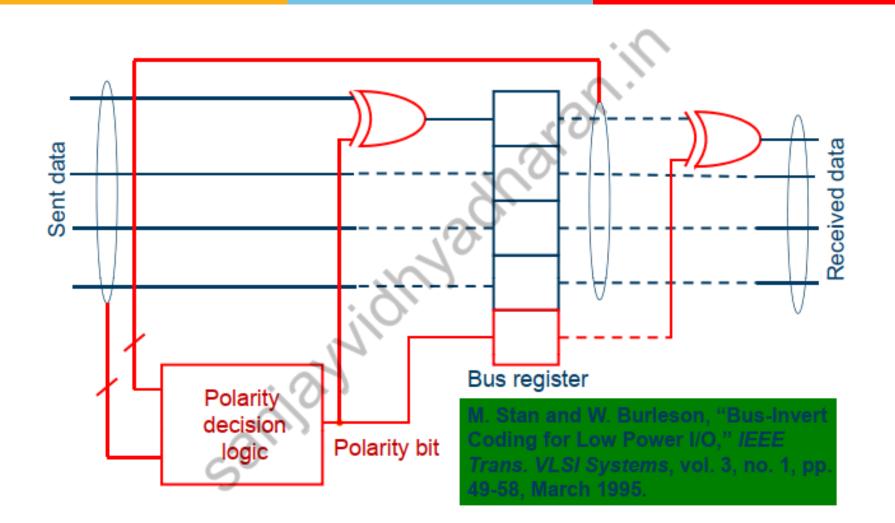

## **Bus Encoding for Reduced Power**

- Example: Four bit bus

- $0000 \rightarrow 1110$  has three transitions. If bits of second pattern are inverted then 0000, then  $0000 \rightarrow 0001$  will have only one transition.

- Bit-inversion encoding for N-bit bus

4/24/2022

### **Bus Encoding for Reduced Power**

COMMUNICATION

4/24/2022

**ELECTRICAL**

**ELECTRONICS**

**INSTRUMENTATION**

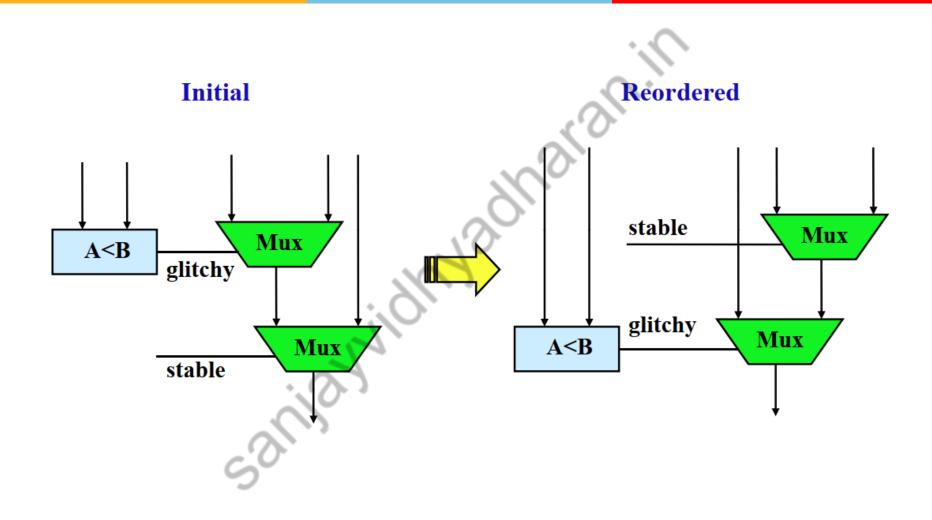

## **RTL-Level Design – Datapath Reordering**

4/24/2022

**ELECTRONICS**

COMMUNICATION

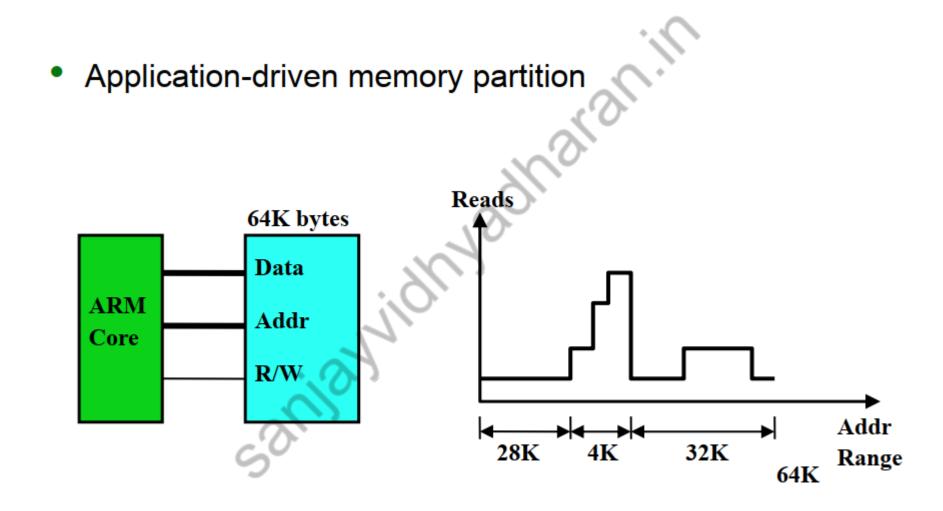

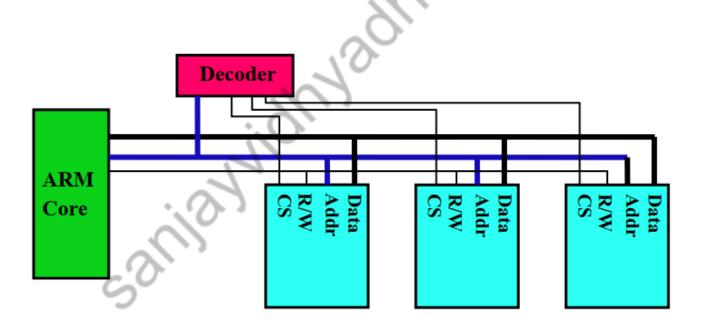

## **RTL-Level Design – Memory Partition**

### **RTL-Level Design – Memory Partition**

COMMUNICATION

4/24/2022

**ELECTRICAL**

**ELECTRONICS**

17

**INSTRUMENTATION**

## **RTL-Level Design – Memory Partition**

A power-optimal partitioned memory organization

COMMUNICATION

4/24/2022

**ELECTRICAL**

**ELECTRONICS**

4/24/2022