Digital Design: 2021-22

Lecture 28: Programable Logic Devices

By Dr. Sanjay Vidhyadharan

ELECTRICAL

# **Types of PLD**

Programable Logic Array (PLA)

Programable Array Logic Array (PAL)

Simple Programmable Logic Device (SPLD)

Complex Programmable Logic Device (CPLD)

Field Programmable Gate Arrays (FPGAs)

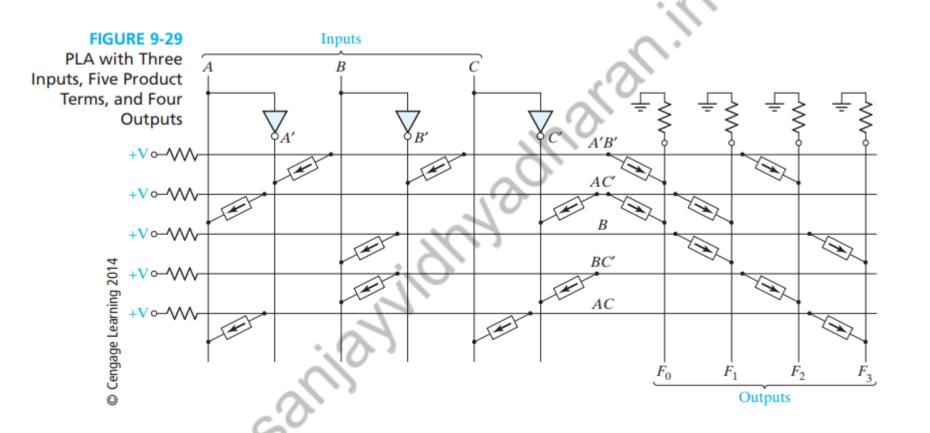

# Programable Logic Array (PLA)

# Programmable device capable of implementing functions expressed in SOP.

- Consists of input buffers and inverters followed by:

- Programmable AND plane, followed by

- Programmable OR plane.

- Can implement m logic functions of n variables. Limit is the number of product terms that can be generated inside of the device.

# Programable Logic Array (PLA)

# Programable Logic Array (PLA)

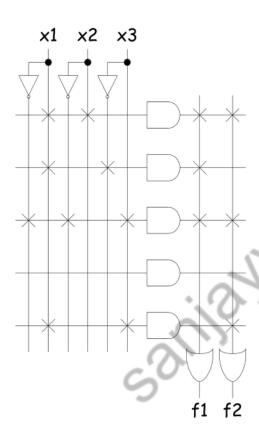

□ Example implementing 2 logic functions of 3 inputs using a 3-5-2 PLA.

$$f_1 = x_1x_2 + x_1\overline{x}_3 + \overline{x}_1\overline{x}_2x_3$$

$$f_2 = x_1x_2 + \overline{x}_1\overline{x}_2x_3 + x_1x_3$$

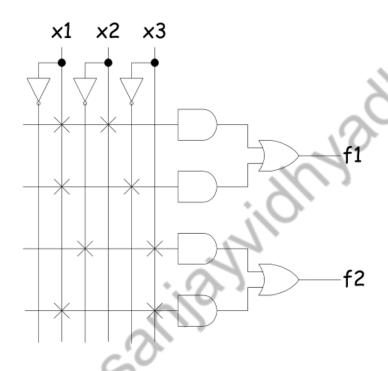

- Similar to a PLA, but only has a programmable AND plane.

- The OR plane is fixed.

- Not as flexible as a PLA since only certain AND gates feed each OR gate, but has fewer things that need programming.

#### □ Example of a PAL:

$$f_1 = x_1 x_2 + x_1 \overline{x}_3$$

$$f_2 = \overline{x}_2 x_3 + x_1 x_3$$

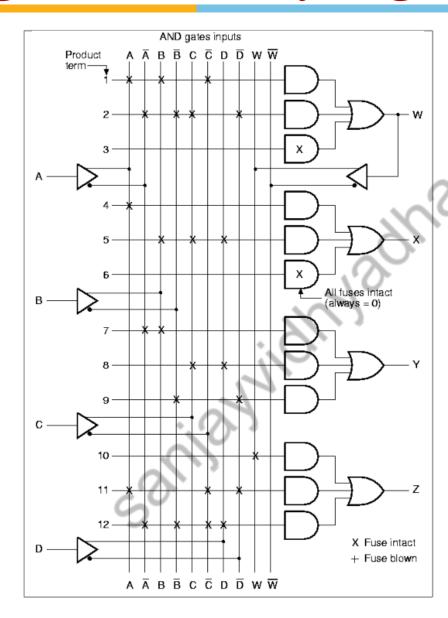

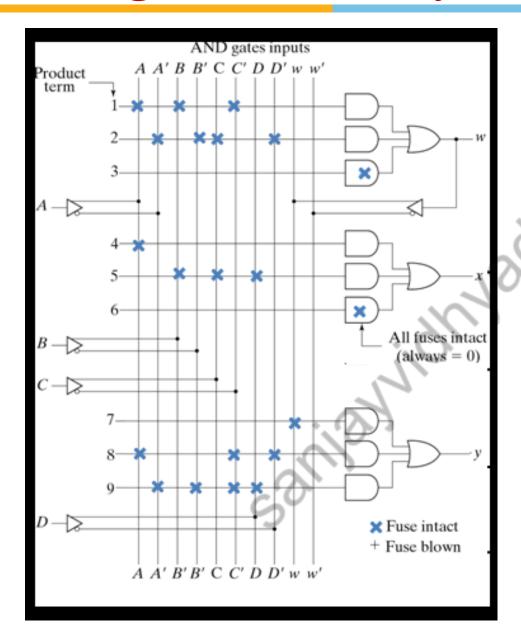

#### Example

$$W(A, B, C, D) = \sum (2, 12, 13)$$

$$X(A, B, C, D) = \sum (7,8,9,10,11,12,13,14,15)$$

$$Y(A, B, C, D) = \sum (1,2,8,12,13)$$

$$W(A, B, C, D) = ABC' + A'B'CD'$$

$$X(A, B, C, D) = A + BCD$$

$$Y(A, B, C, D) = ABC' + A'B'CD' + AC'D' + A'B'C'D$$

$$=$$

W + AC'D' + A'B'C'D

#### Example

$$W(A, B, C, D) = ABC' + A'B'CD'$$

$$X(A, B, C, D) = A + BCD$$

$$Y(A, B, C, D) = W + AC'D' + A'B'C'D$$

| Product | AND Inputs |   |     |   | Outputs |                         |

|---------|------------|---|-----|---|---------|-------------------------|

|         | А          | В | С   | D | W       |                         |

| 1       | 1          | 1 | 0   | - |         | W = ABC' + A'B'CD'      |

| 2       | 0          | 0 | 1   | 0 |         |                         |

| 3       |            |   | 1-1 | J |         |                         |

| 4       | 1          |   | 7.  |   |         | X = A + BCD             |

| 5       | *          | 1 | 1   | 1 |         |                         |

| 6       | <          |   |     |   |         |                         |

| 7       | C-0.       |   |     |   | 1       | Y = W + AC'D' + A'B'C'D |

| 8       | 7          |   | 0   | 0 |         |                         |

| 9       | 0          | 0 | 0   | 1 |         |                         |

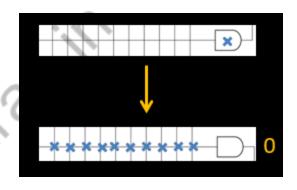

Section 1

Section 2

Section 3

Example

$$W(A, B, C, D) = ABC' + A'B'CD'$$

$$X(A, B, C, D) = A + BCD$$

$$Y(A, B, C, D) = W + AC'D' + A'B'C'D$$

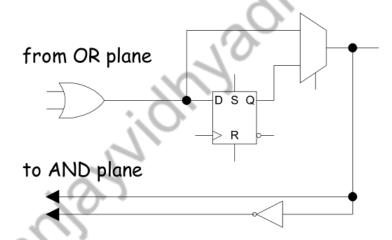

#### **SPLD**

#### Simple Programmable Logic Device (SPLD)

- To implement sequential circuits, take a PAL and add some flip-flops at the output of the OR plane.

- For example...

- □ Above circuit (plus SOP from the AND plane and OR gate) form a MacroCell.

- Several MacroCells together in the same IC is called an SPLD.

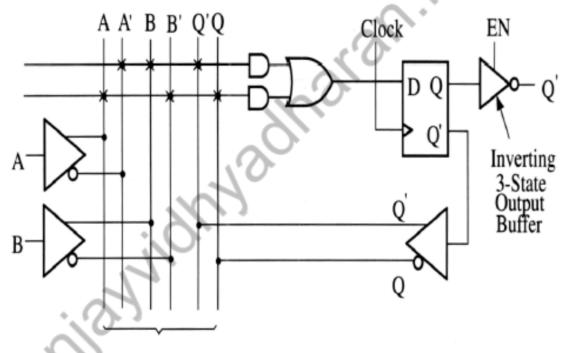

#### **Sequential PAL**

#### Registered (Sequential) PAL:

Programmable AND Array

$$Q^+=D=A'BQ'+AB'Q$$

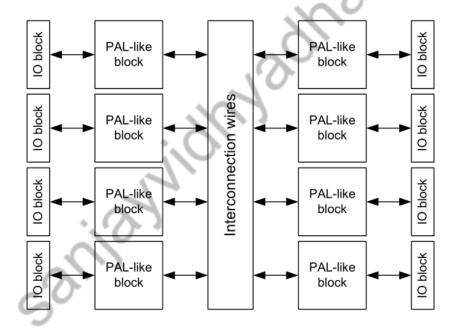

# Complex Programable Logic Device

#### Complex Programmable Logic Device (CPLD)

- □ PLA, PAL and SPLD typically contain small number of outputs (e.g., 16 outputs) with many inputs (e.g., 36 inputs) and a fair number of product terms.

- Therefore only good for simple circuits where each equation has a wide fanin.

- Using a Complex Programmable Logic Device (CPLD) is the "next step" if we have a large complicated circuit...

- CLPD consists of many SPLD connected together by a Programmable Routing Fabric all in the same IC.

#### **Complex Programable Logic Device**

#### Complex Programmable Logic Device (CPLD)

□ Typical architecture (each PAL-like block has many inputs - e.g., 36 - , many product terms - e.g., 80 - and several outputs - e.g., 16).

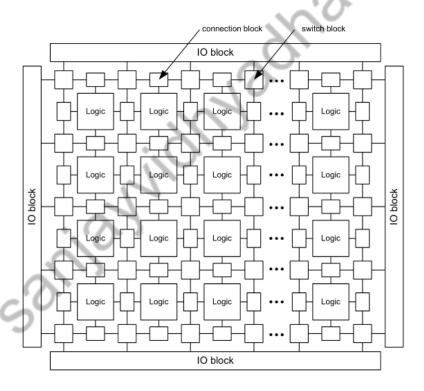

# Field Programable Gate Array

#### Field Programmable Gate Array (FPGA)

□ Typical FPGA consists of many small logic blocks interconnected by programmable routing resources.

# Thank you