# VLSI SYSTEMS AND ARCHITECTURE 2021-22 Lecture 3 Computer A rithmetic Algorithms and

Computer Arithmetic Algorithms and Implementations

By Dr. Sanjay Vidhyadharan

ELECTRICAL

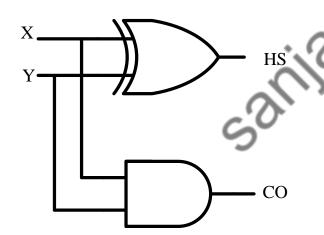

## Half Adder

| Inputs |   | Output |     |  |

|--------|---|--------|-----|--|

| A      | В | Carry  | Sum |  |

| 0      | 0 | 0      | 0   |  |

| 0      | 1 | 0      | 1   |  |

| 1      | 0 | 0      | 1   |  |

| 1      | 1 | 1      | 0   |  |

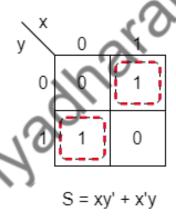

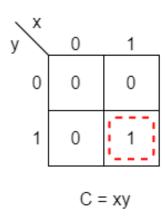

#### K-map for Sum

#### K-map for Carry

Sum =

$$X \cdot Y' + X' \cdot Y = X \oplus Y$$

Carry =  $X \cdot Y$

#### Time Delay for the Half Adder?

1 gate delay

A gate delay of an xor for the half sum

A gate delay of an AND gate for the carry out

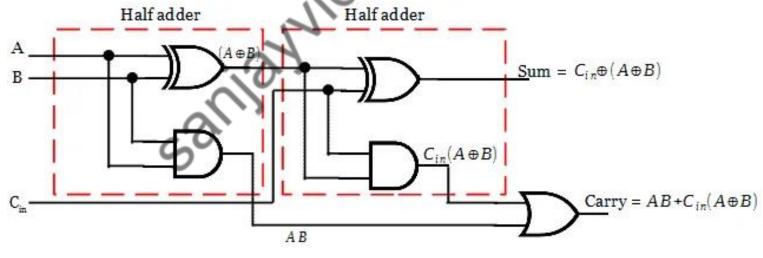

## **Full Adder**

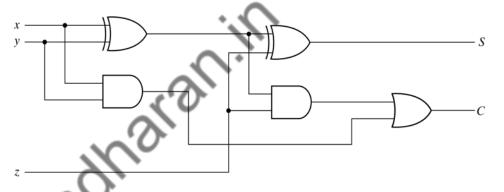

#### Full-adder can also implemented with two half adders and one OR gate.

$$\begin{split} S &= A \oplus B \oplus C_{in} \\ C_{out} &= AB + BC_{in} + AC_{in} \\ &= AB + C_{in} (A+B) \\ &= AB + C_{in} (A \oplus B+AB) \\ &= AB + C_{in} (A \oplus B) + C_{in} AB = AB(1+C_{in}) + C_{in} (A \oplus B) \\ &= AB + C_{in} (A \oplus B) \end{split}$$

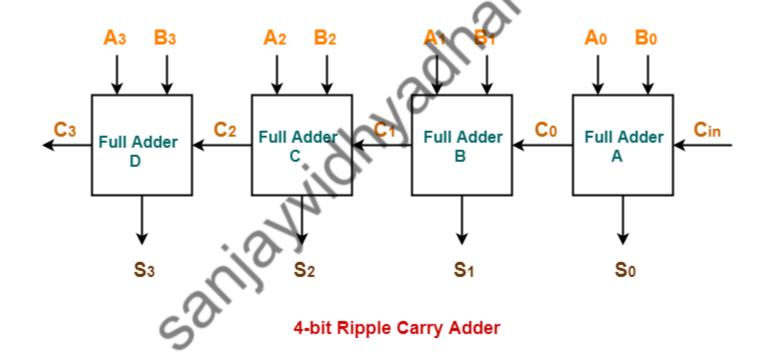

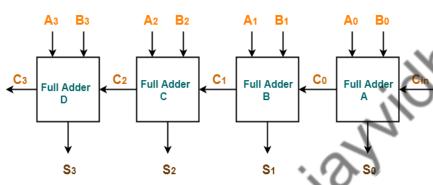

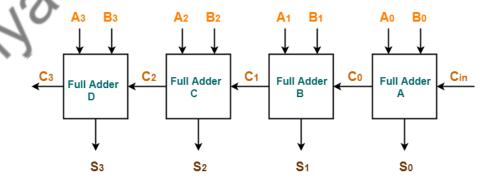

## Ripple Carry Adder

This is called Ripple Carry Adder, because of the construction with full adders are connected in cascade.

Delay= 4 X Full Adder Delay = 12 Gate Delays

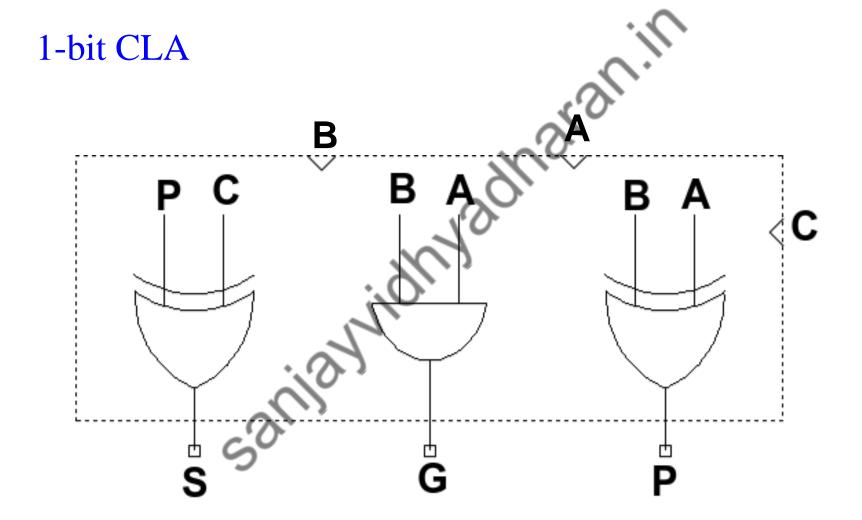

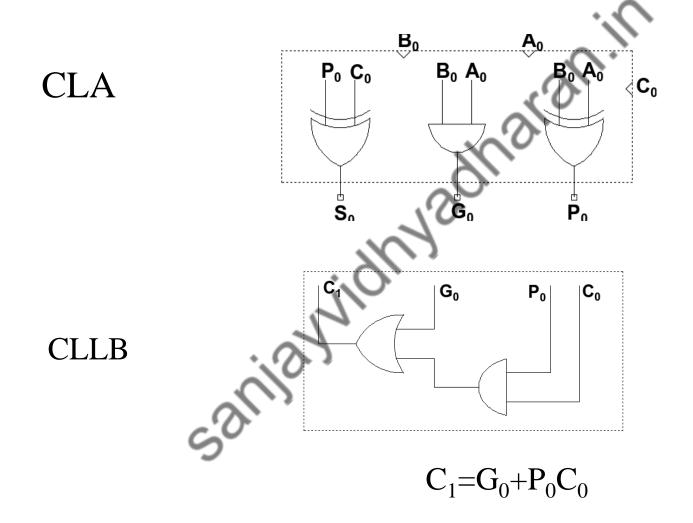

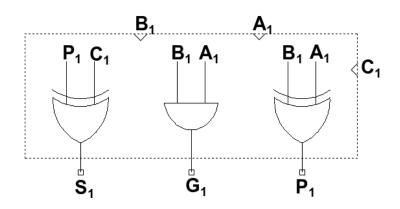

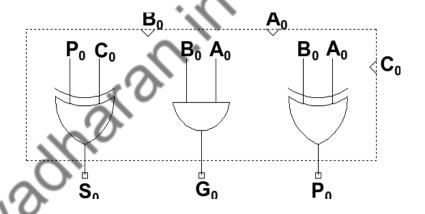

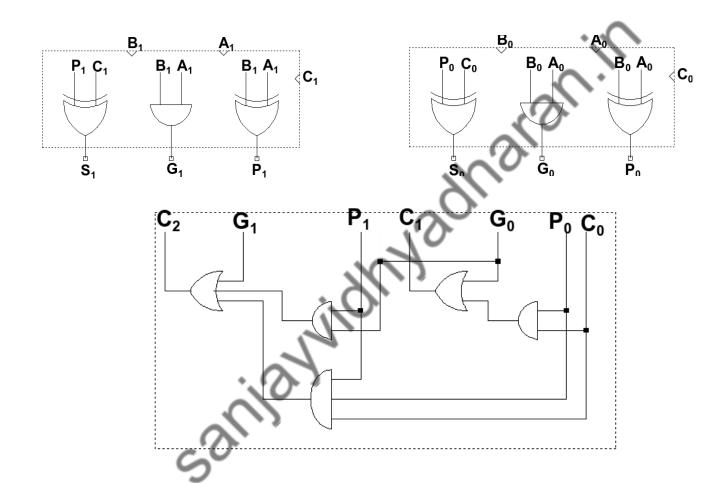

$$C_2 = G_1 + P_1 C_1$$

$$C_{2}=G_{1}+P_{1}C_{1}$$

$$C_{2}=G_{1}+P_{1}(G_{0}+P_{0}C_{0})$$

$$=G_{1}+P_{1}G_{0}+P_{1}P_{0}C_{0}$$

$$C_2 = G_1 + P_1G_0 + P_1P_0C_0$$

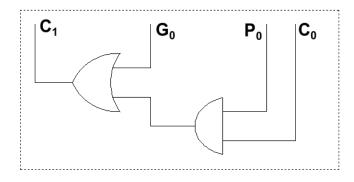

$$C_1 = G_0 + P_0 C_0$$

$$C_1 = G_0 + P_0 C_0$$

$$C_2 = G_1 + P_1 G_0 + P_1 P_0 C_0$$

$$C_3 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$$

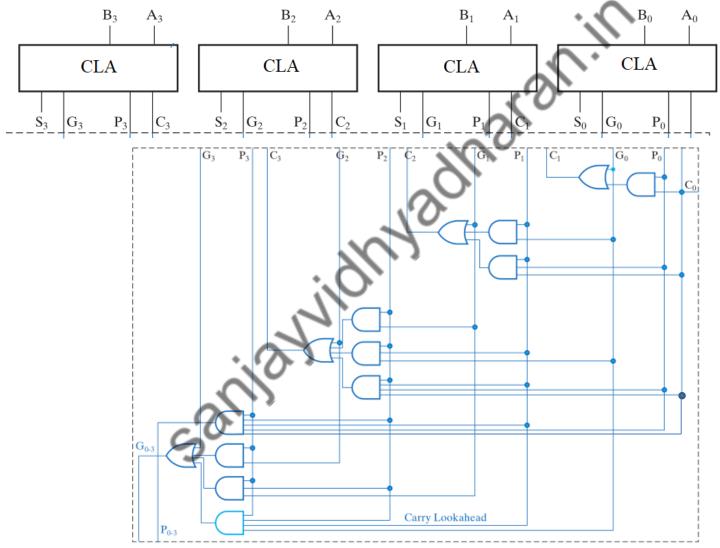

$$\begin{split} &C_1 = G_0 + P_0 C_0 \\ &C_2 = G_1 + P_1 G_0 + P_1 P_0 C_0 \\ &C_3 = G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 C_0 \\ &C_4 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 C_0 \end{split}$$

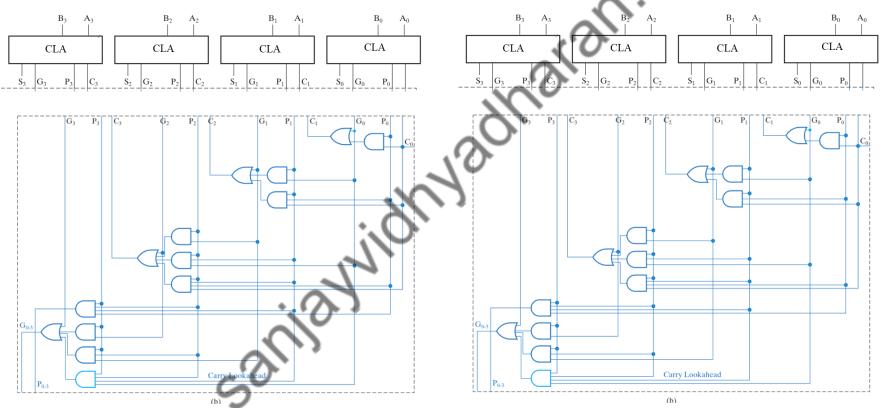

#### 8 Bit Full Adder

Delay = 2 X 3 = 6 Gate Delay

## Ripple Carry Adder

#### 8 Bit Full Adder

4-bit Ripple Carry Adder

4-bit Ripple Carry Adder

Delay = 8 X 3 Gate Delay

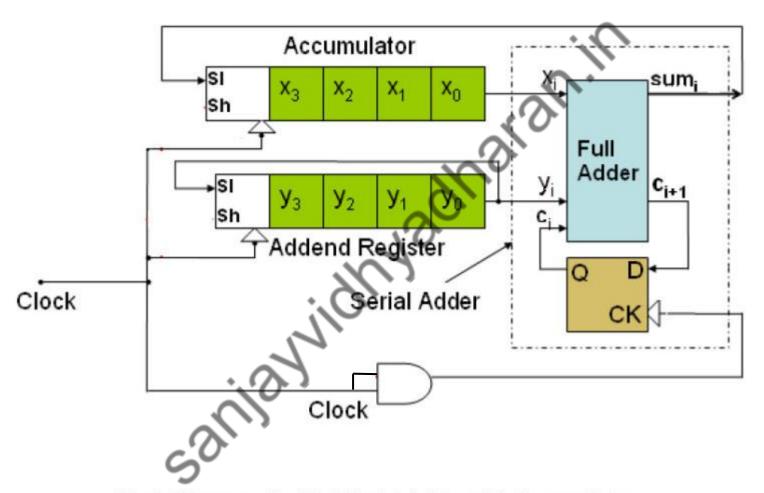

### Serial Adder

Block Diagram of a 4-bit Serial Adder with Accumulator

3/5/2022

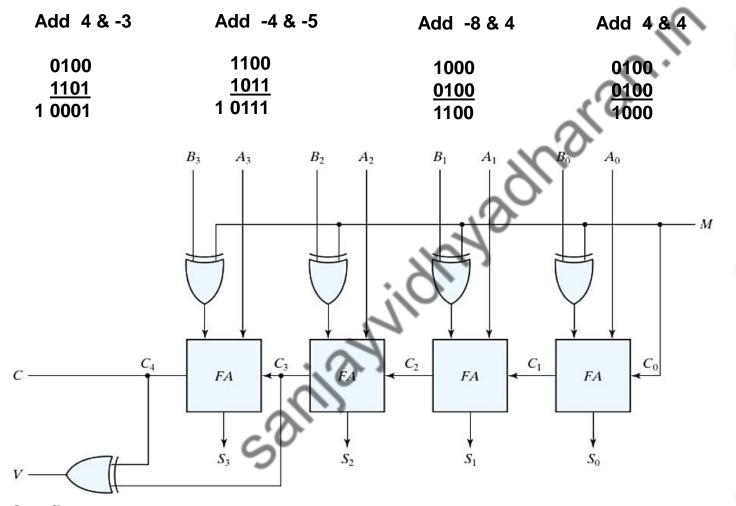

## 4 Bit-Adder Subtractor

| Decimal | 2's comp. |

|---------|-----------|

| 7       | 0111      |

| 6       | 0110      |

| 5       | 0101      |

| 4       | 0100      |

| 3       | 0011      |

| 2       | 0010      |

| 1       | 0001      |

| 0       | 0000      |

| -0      | -         |

| -1      | 1111      |

| -2      | 1110      |

| -3      | 1101      |

| -4      | 1100      |

| -5      | 1011      |

| -6      | 1010      |

| -7      | 1001      |

| -8      | 1000      |

Overflow

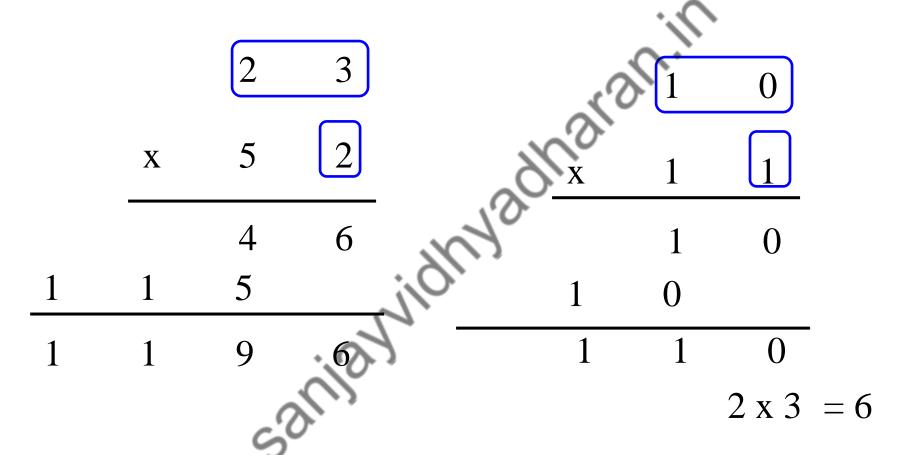

# **Binary Multiplier**

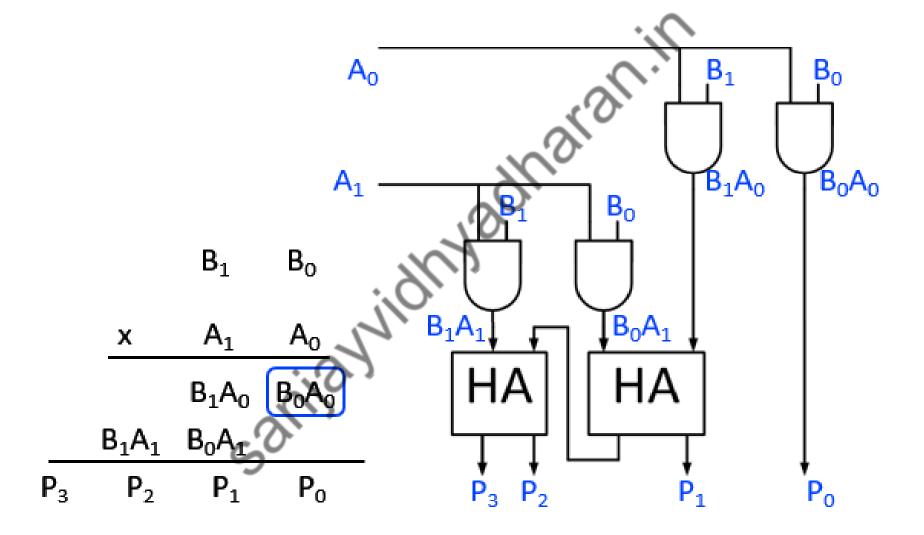

## Binary Multiplier (2-bit x 2-bit)

$$B_1 B_0$$

Gate for 1-bit Multiplication

$$(B_0A_0)$$

?

|   | X        | $A_1$    | $A_0$          |

|---|----------|----------|----------------|

|   |          | $B_1A_0$ | $B_0A_0$       |

|   | $B_1A_1$ | $B_0A_1$ |                |

| 3 | $P_2$    | $P_1$    | P <sub>0</sub> |

| 1 | $\mathbf{A}_{0}$ | B <sub>0</sub> | F |

|---|------------------|----------------|---|

| , | 0                | 0              | 0 |

|   | 0                | 1              | 0 |

|   | 1                | 0              | 0 |

|   | 1                | 1              | 1 |

## Binary Multiplier (2-bit x 2-bit)

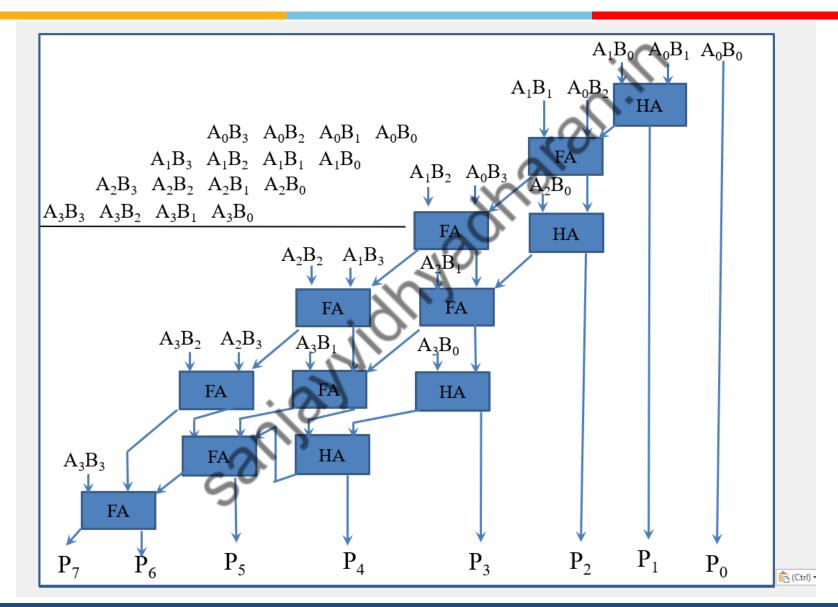

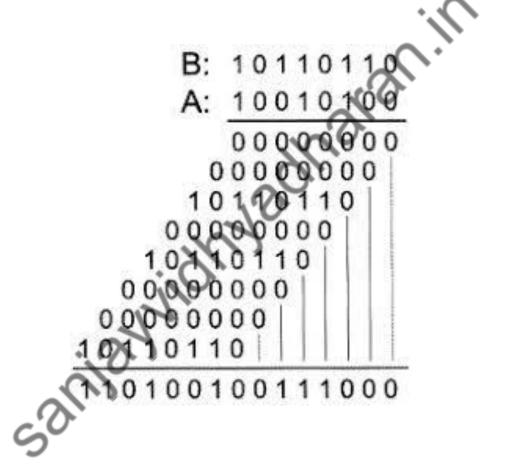

## **Binary Multiplier (4-bit x 4-bit)**

$$(Multiplicand) \ B_3 \ B_2 \ B_1 \ B_0 \\ (Multiplier) \ A3 \ A_2 \ A_1 \ A_0 \\ \hline A_0 B_3 \ A_0 B_2 \ A_0 B_1 \ A_0 B_0 \\ A_1 B_3 \ A_1 B_2 \ A_1 B_1 \ A_1 B_0 \\ A_2 B_3 \ A_2 B_2 \ A_2 B_1 \ A_2 B_0 \\ A_3 B_3 \ A_3 B_2 \ A_3 B_1 \ A_3 B_0$$

## Binary Multiplier (4-bit x 4-bit)

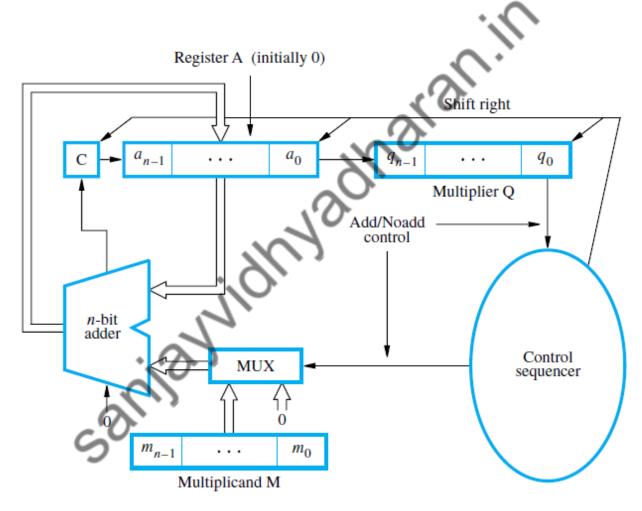

## **Booth Algorithm**

## **Booth Algorithm**

(a) Register configuration

# **Booth Algorithm**

|                     | 3x5  |       |                    |   |

|---------------------|------|-------|--------------------|---|

|                     | M    | Α «   | Q                  |   |

| Initial Condition   | 0011 | 00000 | 010 <mark>1</mark> |   |

| Clk (Load)          | 0011 | 00011 | 0101               | 1 |

| Clk ↓ (Shift Right) | 0011 | 00001 | 1010               |   |

| Clk (Load)          | 0011 | 00001 | <b>101</b> 0       | 2 |

| Clk ↓ (Shift Right) | 0011 | 00000 | 110 <mark>1</mark> |   |

| Clk (Load)          | 0011 | 00011 | 110 <mark>1</mark> | 3 |

| Clk ↓ (Shift Right) | 0011 | 00001 | <b>1110</b>        |   |

| Clk (Load)          | 0011 | 00001 | <b>1110</b>        | 4 |

| Clk ↓ (Shift Right) | 0011 | 00000 | 1111               |   |

Thank you sarianidh you

3/5/2022