# VLSI SYSTEMS AND ARCHITECTURE 2021-22

Lab-4: Handling multi-bit data and Concatenation in Verilog

By Dr. Sanjay Vidhyadharan

**ELECTRICAL**

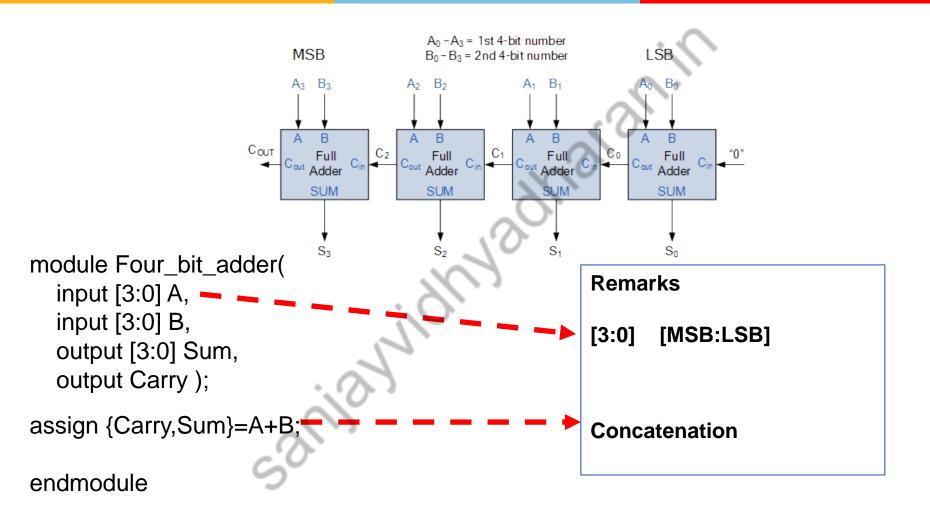

## **Demonstration: 4-bit Adder**

3/12/2022 2

### General digital systems

User enters decimal  $\rightarrow$  BCD i/p $\rightarrow$  Binary i/p $\rightarrow$  compute in binary  $\rightarrow$  Binary o/p $\rightarrow$  BCD o/p $\rightarrow$  Decimal output shown to user

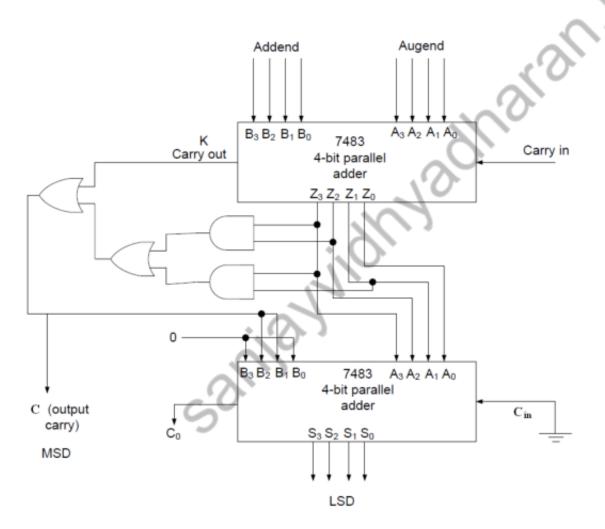

#### **BCD** addition

$$4 + 5$$

$$4 + 8$$

1 1 0 0 Is this expected Result?

Expected answer

0001 0010

is BCD of 12

#### **BCD** addition

$$4 + 8$$

Greater than 9

$$1100$$

$$0\ 0\ 0\ 1\ 0\ 0\ 1\ 0$$

#### **BCD** addition

After addition if carry out is generated or if sum is greater than 9 there is need for correction

#### **BCD** addition

0 0 0 0

0001

0010

0011

0100

0101

0 1 1 0

0111

1000

1001

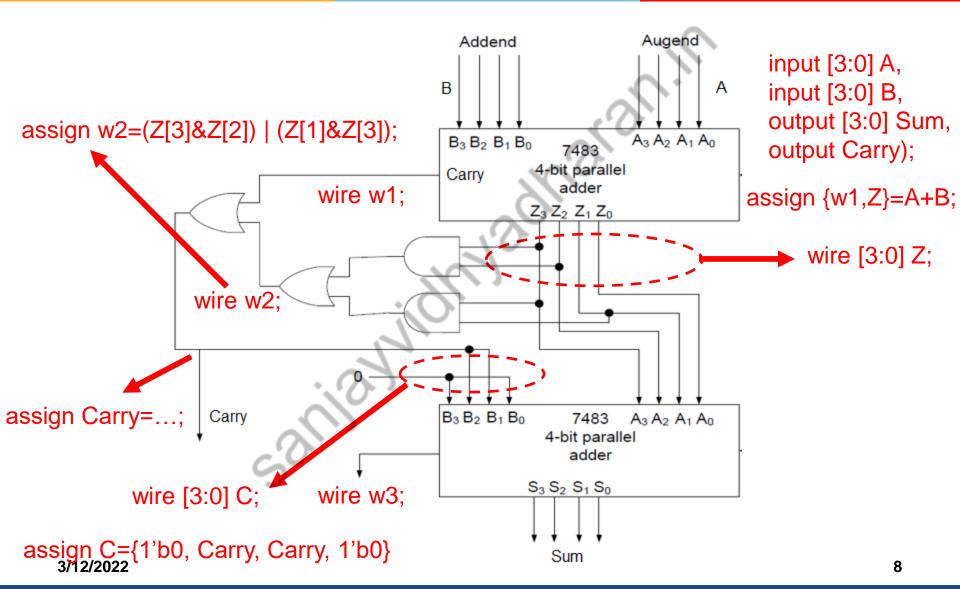

## **Problem 1: BCD Adder**

Thank you

3/12/2022