Digital Design: 2021-22

Lecture 23: Synchronous Counters

By Dr. Sanjay Vidhyadharan

ELECTRICAL

## Binary Synchronous Counter

#### 3 bit binary counter

| 0 | 0 | 0 | 0 |

|---|---|---|---|

| 1 | 0 | 0 | 1 |

| 2 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 |

| 4 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 |

| 7 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 |

- · Idea:

- to use same clock for all flip-flops

### **Synchronous Counters**

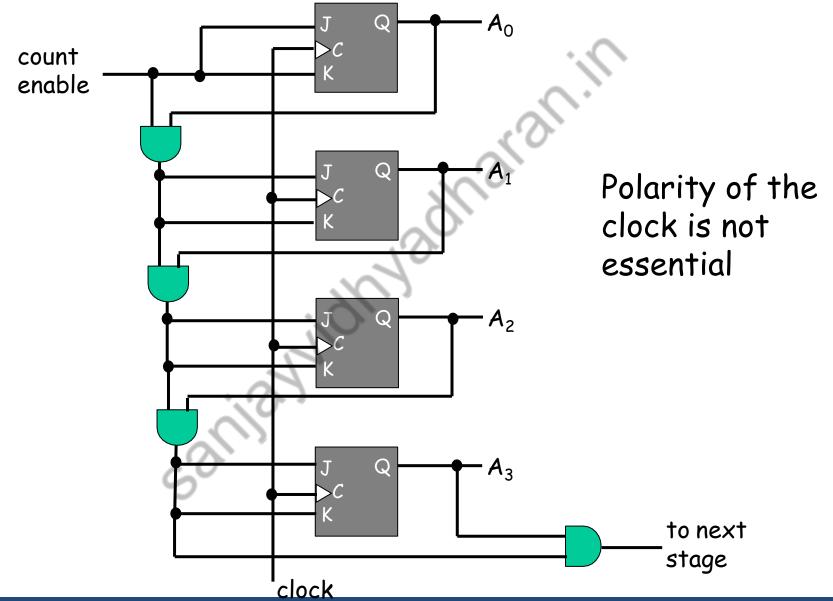

- There is a common clock

- that triggers all flip-flops simultaneously

- If T = 0 or J = K = 0 the flip-flop does not change state.

- If T = 1 or J = K = 1 the flip-flop does change state.

- Design procedure is so simple

- no need for going through sequential logic design process

- Ao is always complemented

- $A_1$  is complemented when  $A_0 = 1$

- $A_2$  is complemented when  $A_0 = 1$  and  $A_1 = 1$

- so on

# 4-bit Binary Synchronous Counter

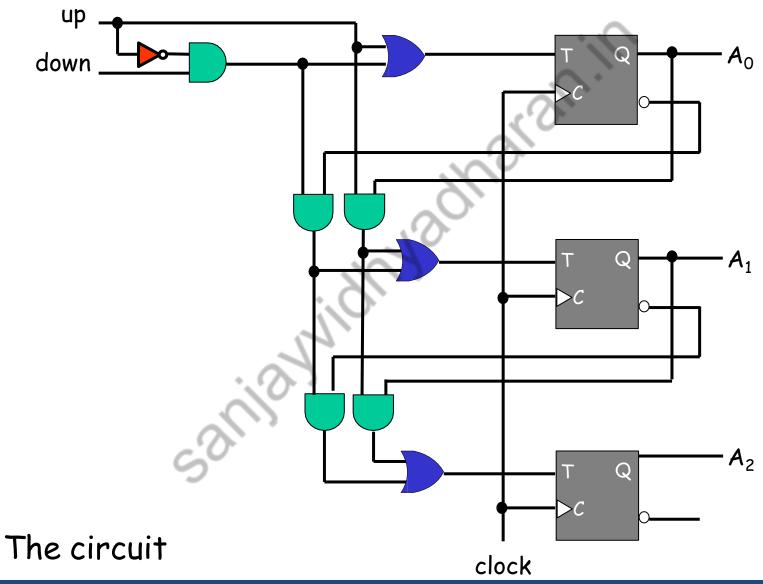

### **Up-Down Binary Counter**

- When counting downward

- the least significant bit is always complemented (with each clock pulse)

- A bit in any other position is complemented if all lower significant bits are equal to 0.

- For example: 0100

- · Next state: 0011

- For example: 1100

- · Next state: 1011

#### STATE TABLE

| COUNT | Q1 | Q0 |

|-------|----|----|

| 3     | 1  | 1  |

| 2     | 1  | 0  |

| 1     | 0  | 1  |

| 0     | 0  | 0  |

# Up-Down Binary Counter

### Synchronous BCD Counter

Better to apply the sequential circuit design procedure

| F                     | resent state Next state output Flip-Flop inputs |                |                       |                       |                       |                       | Next state            |   |                | ts             |                |       |

|-----------------------|-------------------------------------------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---|----------------|----------------|----------------|-------|

| <b>A</b> <sub>8</sub> | <b>A</b> <sub>4</sub>                           | A <sub>2</sub> | <b>A</b> <sub>1</sub> | <b>A</b> <sub>8</sub> | <b>A</b> <sub>4</sub> | <b>A</b> <sub>2</sub> | <b>A</b> <sub>1</sub> | Y | T <sub>8</sub> | T <sub>4</sub> | T <sub>2</sub> | $T_1$ |

| 0                     | 0                                               | 0              | 0                     | 0                     | 0                     | 0                     | 1/                    | 0 | 0              | 0              | 0              | 1     |

| 0                     | 0                                               | 0              | 1                     | 0                     | 0                     | 1                     | 0                     | 0 | 0              | 0              | 1              | 1     |

| 0                     | 0                                               | 1              | 0                     | 0                     | 0                     | 1                     | 7.4                   | 0 | 0              | 0              | 0              | 1     |

| 0                     | 0                                               | 1              | 1                     | 0                     | 1                     | 0                     | 0                     | 0 | 0              | 1              | 1              | 1     |

| 0                     | 1                                               | 0              | 0                     | 0                     | 1                     | 0                     | 1                     | 0 | 0              | 0              | 0              | 1     |

| 0                     | 1                                               | 0              | 1                     | 0                     | 1                     | 1                     | 0                     | 0 | 0              | 0              | 1              | 1     |

| 0                     | 1                                               | 1              | 0                     | 0                     | 1                     | 1                     | 1                     | 0 | 0              | 0              | 0              | 1     |

| 0                     | 1                                               | 1              | 1.0                   | 1                     | 0                     | 0                     | 0                     | 0 | 1              | 1              | 1              | 1     |

| 1                     | 0                                               | 0              | 0                     | 1                     | 0                     | 0                     | 1                     | 0 | 0              | 0              | 0              | 1     |

| 1                     | 0                                               | 0              | 1                     | 0                     | 0                     | 0                     | 0                     | 1 | 1              | 0              | 0              | 1     |

### Synchronous BCD Counter

- · The flip-flop input equations

- $-T_1 = 1$

- $T_2 = A_8' A_1$

- $T_4 = A_2 A_1$

- $T_8 = A_8 A_1 + A_4 A_2 A_1$

- Output equation

- $y = A_8 A_1$

- Cost

- Four Tflip-flops

- four 2-input AND gates

- one OR gate

- one inverter

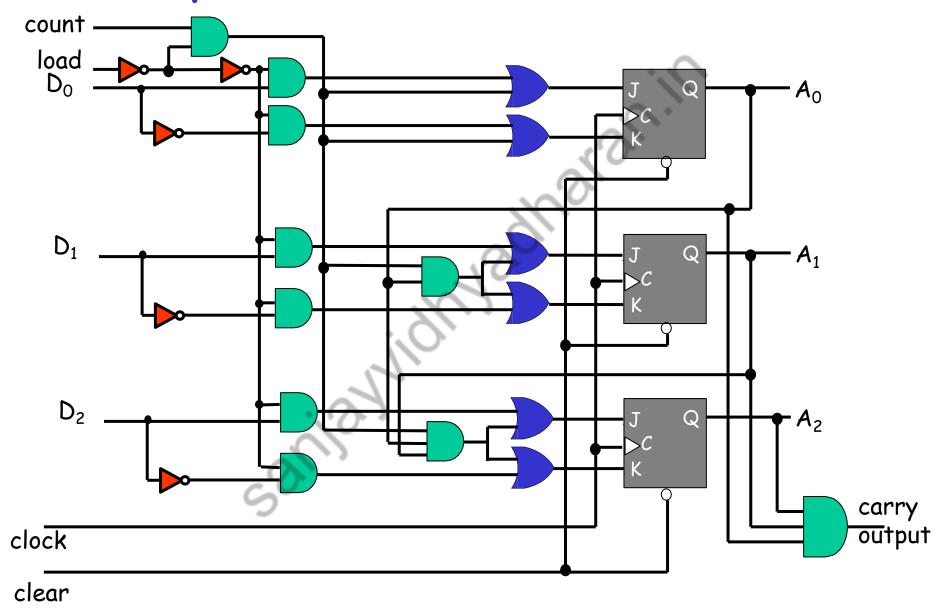

# Binary Counter with Parallel Load

### Binary Counter with Parallel Load

#### Function Table

| clear | clock    | load | Count | Function    |

|-------|----------|------|-------|-------------|

| 0     | X        | X    | X     | clear to 0  |

| 1     | <b>↑</b> | 1    | X     | load inputs |

| 1     | 1        | 10   | 1     | count up    |

| 1     | 501      | 0    | 0     | no change   |

#### **Other Counters**

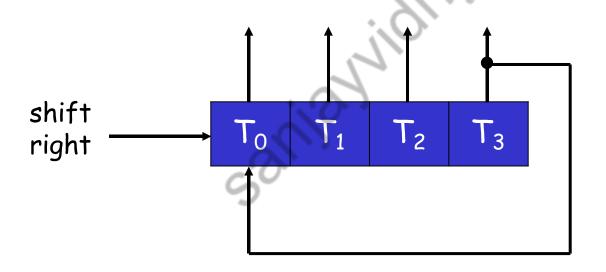

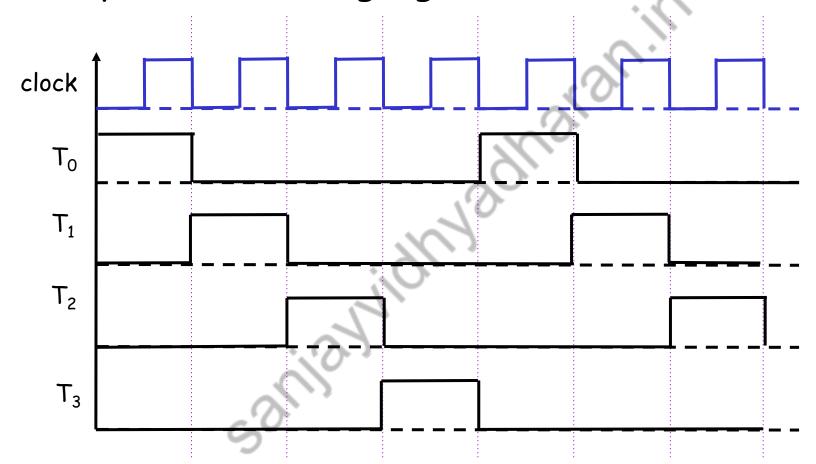

#### Ring Counter

- Timing signals control the sequence of operations in a digital system

- A ring counter is a circular shift register with only one flip-flop being set at any particular time, all others are cleared.

initial value 1000

### Ring Counter

Sequence of timing signals

### Ring Counter

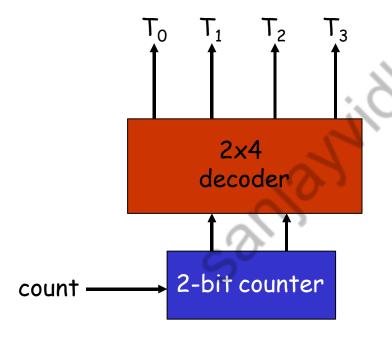

- To generate 2<sup>n</sup> timing signals,

- we need a shift register with 2<sup>n</sup> flip-flops

- or, we can construct the ring counter with a binary counter and a decoder

#### Cost:

- ·2 flip-flop

- ·2-to-4 line decoder

#### Cost in general case:

- n flip-flops

- · n-to-2<sup>n</sup> line decoder

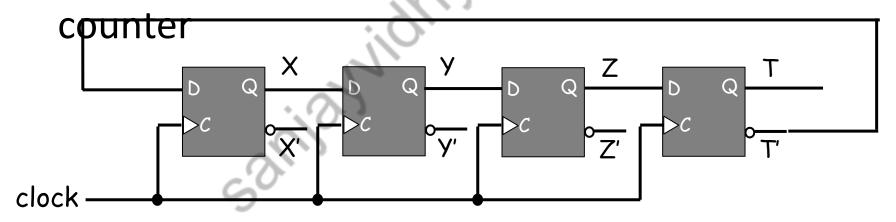

- A k-bit ring counter can generate k distinguishable states

- The number of states can be doubled if the shift register is connected as a <u>switch-tail</u> ring

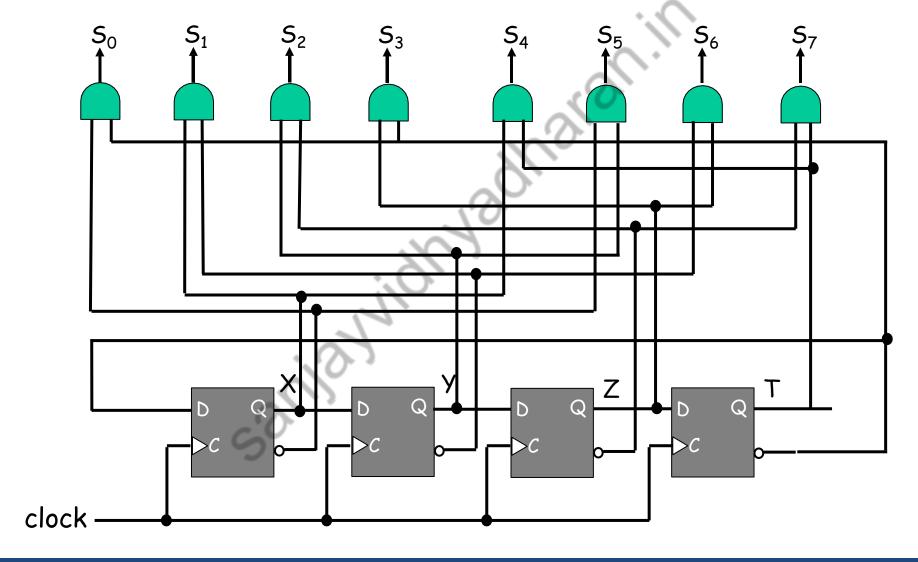

· Count sequence and required decoding

| sequence | Flip-flop outputs |   |   |   |        |

|----------|-------------------|---|---|---|--------|

| number   | X                 | У | Z | T | Output |

| 1        | 0                 | 0 | 0 | 0 | X'T'   |

| 2        | 1                 | 0 | 0 | 0 | XY'    |

| 3        | 1                 | 1 | 0 | 0 | YZ'    |

| 4        | 1                 | 1 | 1 | 0 | ZT'    |

| 5        | 1                 | 1 | 1 | 1 | XT     |

| 6        | 0                 | 1 | 1 | 1 | X'Y    |

| 7        | 0                 | 0 | 1 | 1 | Y'Z    |

| 8        | 0                 | 0 | 0 | 1 | Z'T    |

Decoding circuit

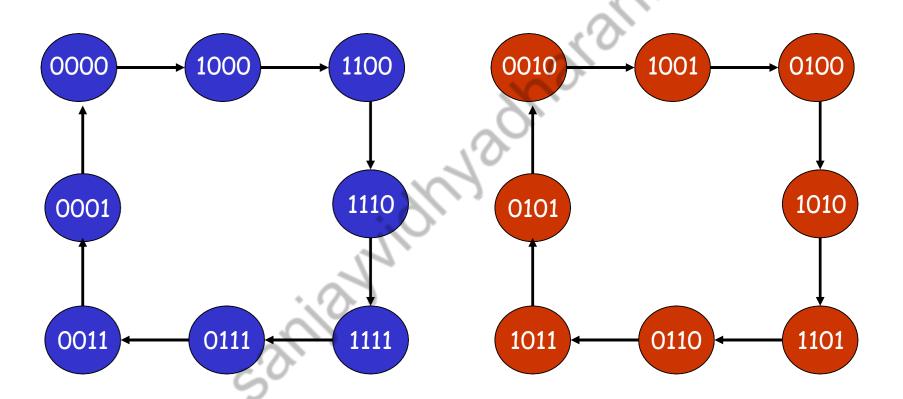

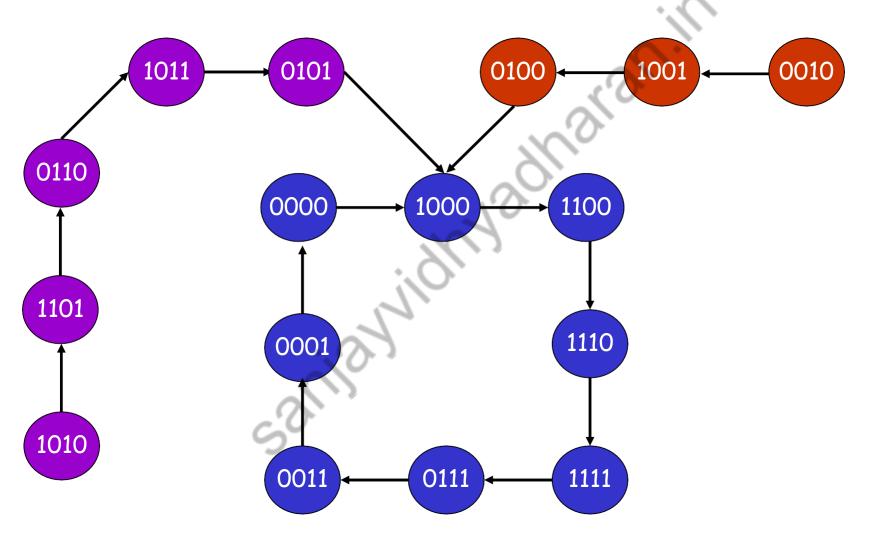

#### **Unused States in Counters**

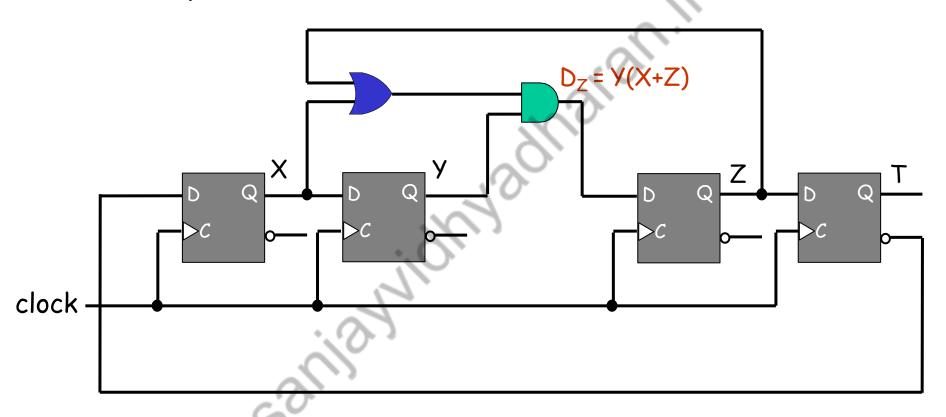

4-bit Johnson counter

|   | Inp | outs  |   |   | Out | puts |   |

|---|-----|-------|---|---|-----|------|---|

| X | У   | Z     | Т | Х | У   | Z    | Т |

| 0 | 0   | 0     | 0 | 1 | 0   | 0    | 0 |

| 1 | 0   | 0     | 0 | 1 | 1   | 0    | 0 |

| 1 | 1   | 0     | 0 | 1 | 1   | 40   | 0 |

| 1 | 1   | 1     | 0 | 1 | 1   | () L | 1 |

| 1 | 1   | 1     | 1 | 0 | 1   | 1    | 1 |

| 0 | 1   | 1     | 1 | 0 | 0   | 1    | 1 |

| 0 | 0   | 1     | 1 | 0 | 0   | 0    | 1 |

| 0 | 0   | 0     | 1 | 0 | 0   | 0    | 0 |

| 1 | 0   | 1     | 0 | 1 | 1   | 0    | 1 |

| 1 | 1   | 0     | 1 | 0 | 1   | 1    | 0 |

| 0 | 1   | 1     | 0 | 1 | 0   | 1    | 1 |

| 1 | 0   | 1     | 1 | 0 | 1   | 0    | 1 |

| 0 | 1   | $c_0$ | 1 | 0 | 0   | 0    | 0 |

| 0 | 0   | 1     | 0 | 1 | 0   | 0    | 1 |

| 1 | 0   | 0     | 1 | 0 | 1   | 0    | 0 |

| 0 | 1   | 0     | 0 | 1 | 0   | 0    | 0 |

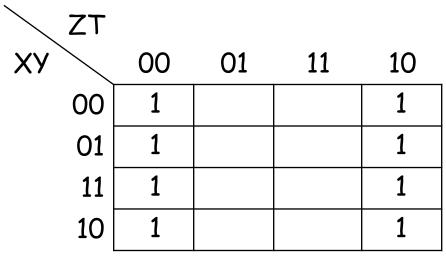

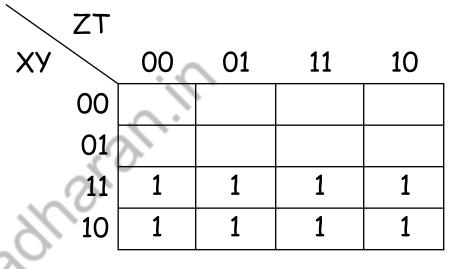

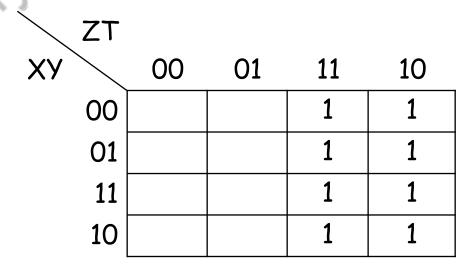

# K-Maps

$$X = T'$$

$$Y = X$$

| ZT |    |    |    | :(0) |

|----|----|----|----|------|

| XX | 00 | 01 | 11 | 10   |

| 00 |    |    | .0 |      |

| 01 |    |    |    | 1    |

| 11 | 1  | 16 | 1  | 1    |

| 10 |    |    |    |      |

$$Z = XY + YZ$$

T = Z

#### Unused States in Counters

Remedy

# . State diagram States in Counters

Thank you