INSTRUMENTATION

# VLSI Design : 2021-22 Lecture 8 CMOS Inverter Transient Response

## By Dr. Sanjay Vidhyadharan

ELECTRICAL ELECTRONICS COMMUNICATION

#### **CMOS Inverter: Transient Response**

2/12/2022

#### **CMOS Inverter: Transient Response**

2/12/2022

ELECTRICAL

#### **ELECTRONICS**

#### **CMOS Inverter: Delay-Time Definitions**

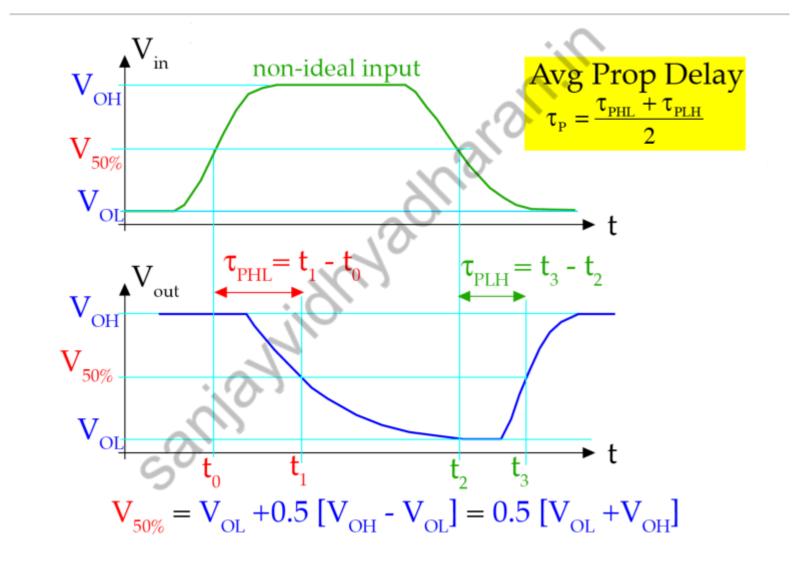

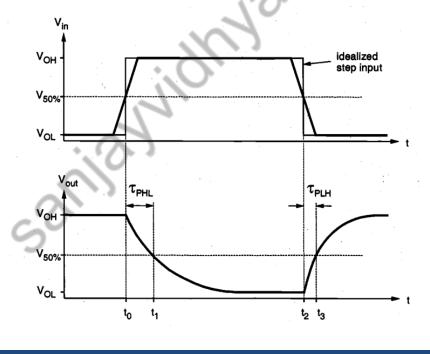

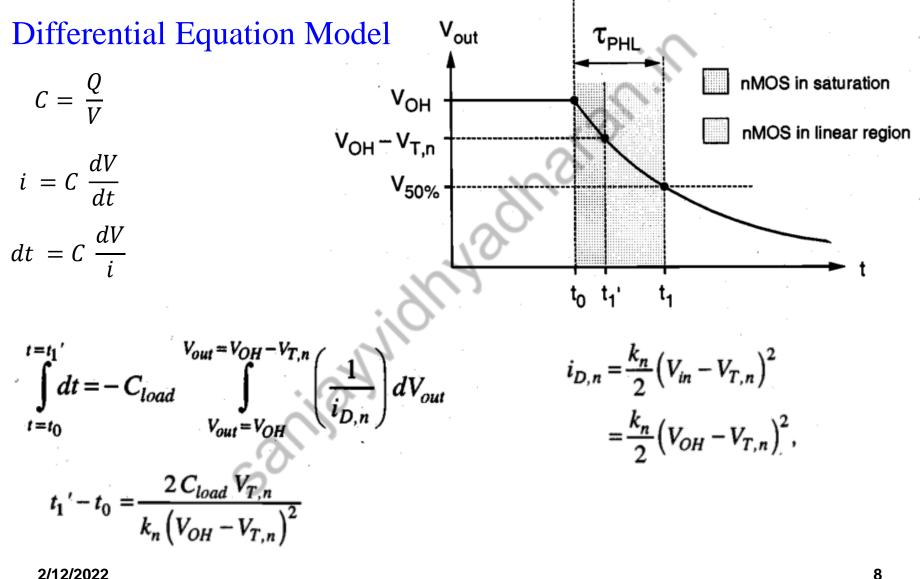

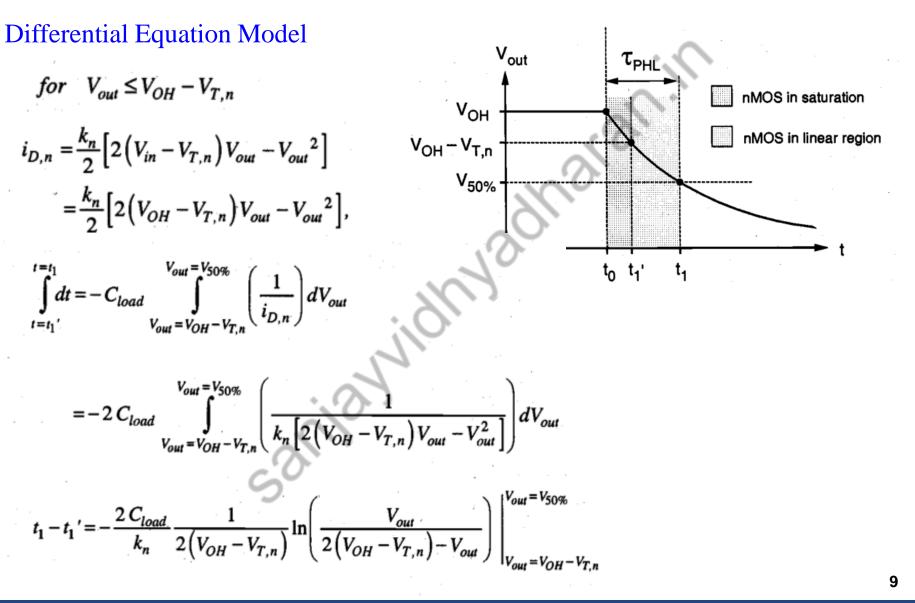

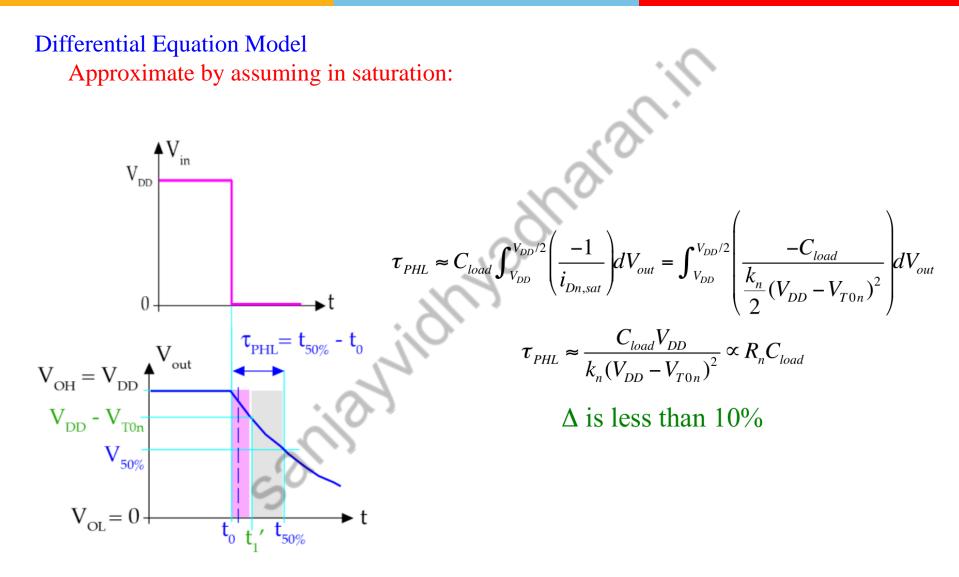

By definition,  $TP_{HL}$  is the time delay between the V50 %-transition of the rising input voltage and the V50%-transition of the falling output voltage. Similarly,  $TP_{LH}$  is defined as the time delay between the V50% -transition of the falling input voltage and the V50 %-transition of the rising output voltage.

To simplify the analysis and the derivation of delay expressions, the input voltage waveform is usually assumed to be an ideal step pulse with zero rise and fall times. Under this assumption,

COMMUNICATION

2/12/2022

ELECTRICAL

**ELECTRONICS**

#### **CMOS Inverter: Transient Response**

2/12/2022

ELECTRICAL

#### **ELECTRONICS**

#### COMMUNICATION

INSTRUMENTATION

COMMUNICATION

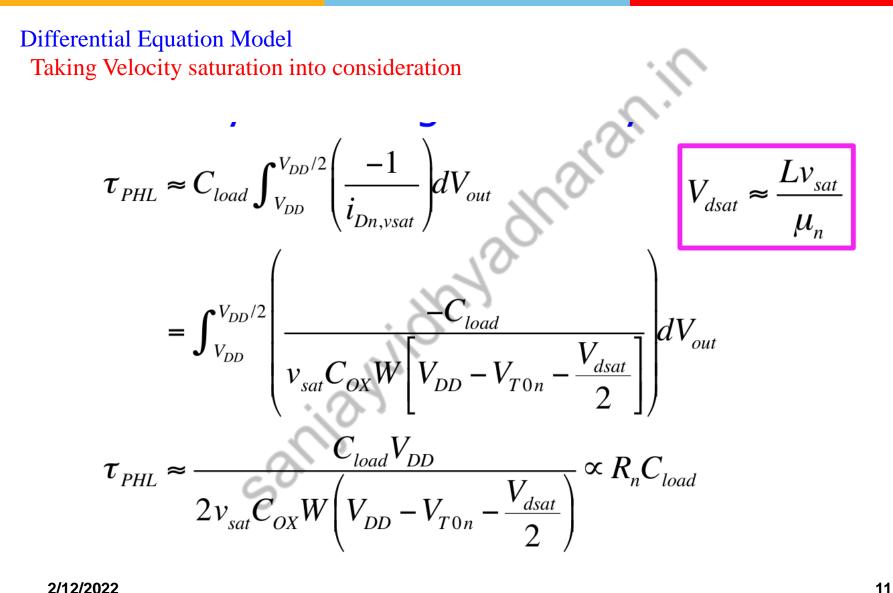

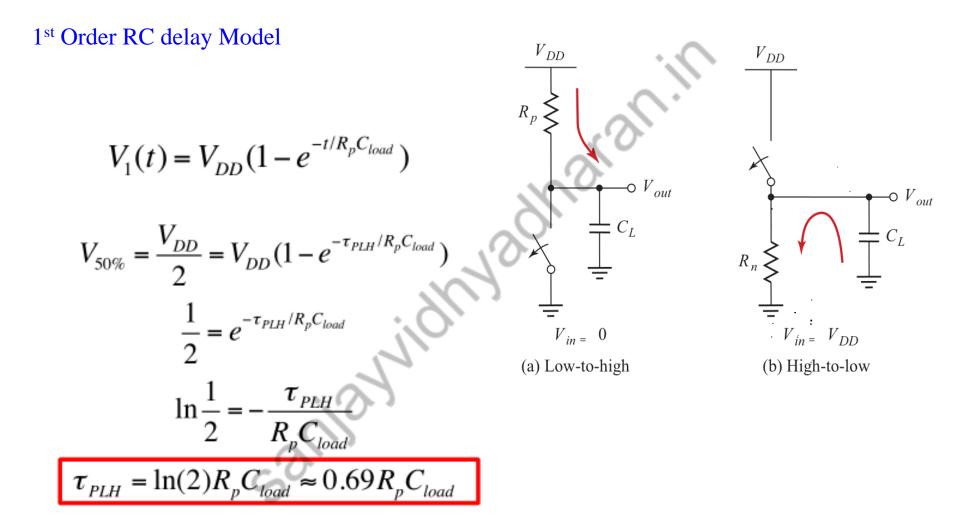

# Three Methods Vadnarani Average Current Model 1. **Differential Equation Model** 2. 1<sup>st</sup> Order RC delay Model 3.

**ELECTRONICS**

2/12/2022

**ELECTRICAL**

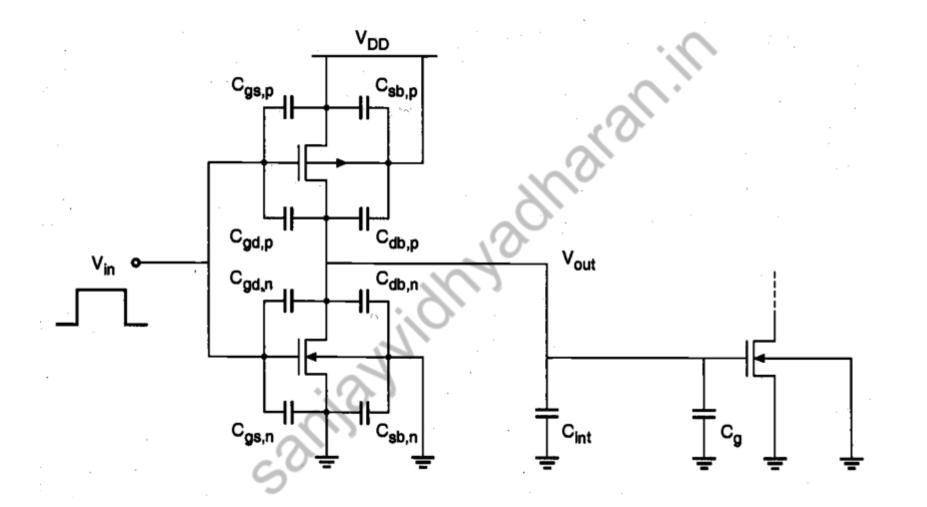

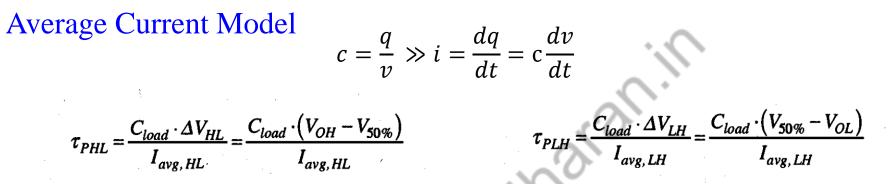

Note that the average current during high-to-low transition can be calculated by using the current values at the beginning and the end of the transition.

$$I_{avg, HL} = \frac{1}{2} \left[ i_C (V_{in} = V_{OH}, V_{out} = V_{OH}) + i_C (V_{in} = V_{OH}, V_{out} = V_{50\%}) \right]$$

$$I_D = \frac{k'_n W (V_{DD} - V_T)^2}{2L}$$

$$I_D = \frac{k'_n W (V_{DD} - V_T - \frac{V_{DD}}{2}) V_{DS}}{L}$$

$$I_D = \frac{k'_n W (V_{DD} - V_T - \frac{V_{DD}}{4}) \frac{V_{DD}}{2}}{L}$$

Similarly, the average capacitance current during low-to-high transition is

$$I_{avg,LH} = \frac{1}{2} \Big[ i_C \Big( V_{in} = V_{OL}, V_{out} = V_{50\%} \Big) + i_C \Big( V_{in} = V_{OL}, V_{out} = V_{OL} \Big) \Big]$$

2/12/2022

ELECTRICAL

ELECTRONICS

COMMUNICATION

2/12/2022

ELECTRICAL

#### ELECTRONICS

#### COMMUNICATION

INSTRUMENTATION

2/12/2022

2/12/2022

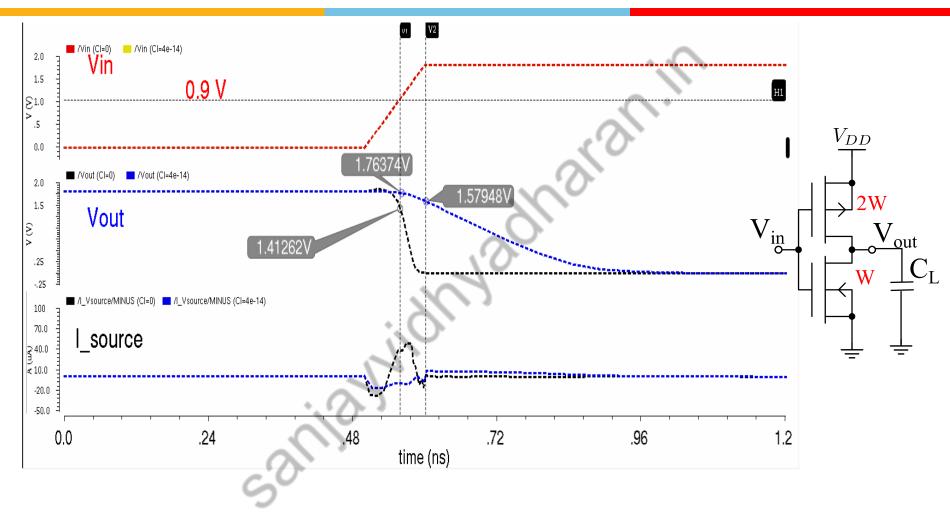

#### **CMOS Inverter: Transient Response**

#### 2/12/2022

COMMUNICATION

## **CMOS Inverter: Transient Response**

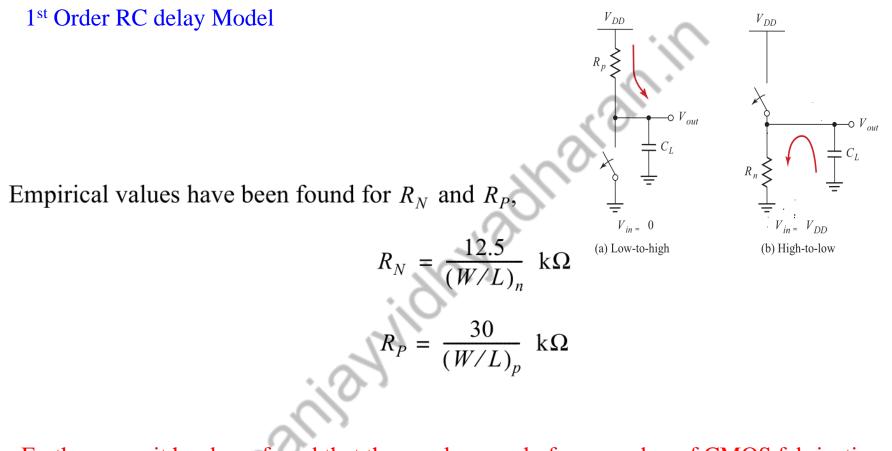

Furthermore, it has been found that these values apply for a number of CMOS fabrication processes including 0.25  $\mu$ m, 0.18  $\mu$ m, and 0.13  $\mu$ m (see Hodges et al., 2004).

COMMUNICATION

2/12/2022

**ELECTRICAL**

**ELECTRONICS**

13

INSTRUMENTATION

## **Sizing of CMOS Inverter**

**ELECTRICAL**

### **Sizing of CMOS Inverter**

$$t_p = 0.69R_{eq}(C_{int} + C_{ext})$$

= 0.69R\_{eq}C\_{int}(1 + C\_{ext}/C\_{int}) = t\_{p0}(1 + C\_{ext}/C\_{int})

$t_{p0} = 0.69 R_{eq}C_{int}$  represents the delay of the inverter only loaded by its own intrinsic capacitance ( $C_{ext} = 0$ ), and is called the *intrinsic or unloaded delay*.

- The intrinsic delay of the inverter tp0 is independent of the sizing of the gate, and is purely determined by technology and inverter layout.

- When no load is present, an increase in the drive of the gate is totally offset by the increased capacitance.

COMMUNICATION

2/12/2022

ELECTRICAL

#### **Sizing of CMOS Inverter**

$$t_{p} = 0.69R_{eq}(C_{int} + C_{ext})$$

= 0.69R\_{eq}C\_{int}(1 + C\_{ext}/C\_{int}) = t\_{p0}(1 + C\_{ext}/C\_{int})

$C_{int} = S C_{ext}$

- Making S infinitely large yields the maximum obtainable performance gain, eliminating the impact of any external load, and reducing the delay to the intrinsic one.

- Yet, any sizing factor S that is sufficiently larger than (Cext /Cint ) produces similar results at a substantial gain in silicon area.

2/12/2022

COMMUNICATION

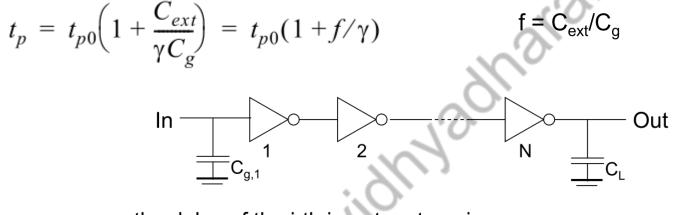

$$C_{int} = \gamma C_g$$

$\gamma$  is a proportionality factor, which is only a function of technology and is close to 1 for most sub-micron processes.

the delay of the j-th inverter stage is

and

$$\begin{aligned} t_{p,j} &= t_{p0} \left( 1 + C_{g,j+1} / (\gamma C_{g,j}) \right) = t_{p0} (1 + f_j / \gamma) \\ t_p &= t_{p1} + t_{p2} + \ldots + t_{pN} \end{aligned}$$

so

$$t_{p} = \sum t_{p,j} = t_{p0} \sum (1 + C_{g,j+1} / (\gamma C_{g,j}))$$

□ If C<sub>L</sub> is given

- How should the inverters be sized?

- How many stages are needed to minimize the delay?

2/12/2022

**ELECTRONICS**

COMMUNICATION

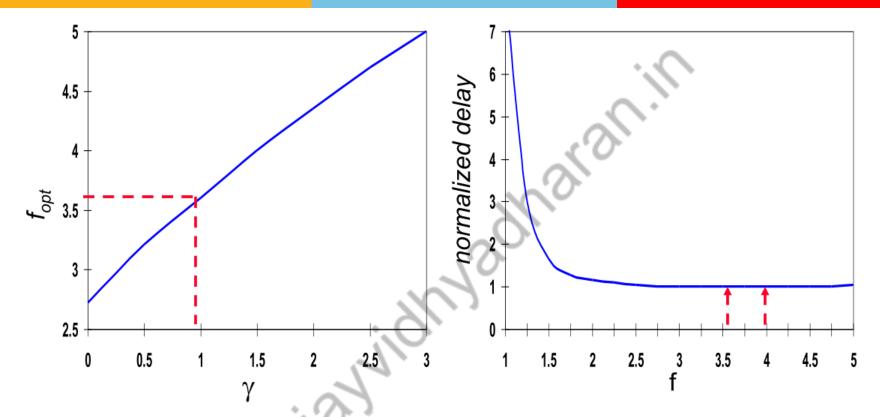

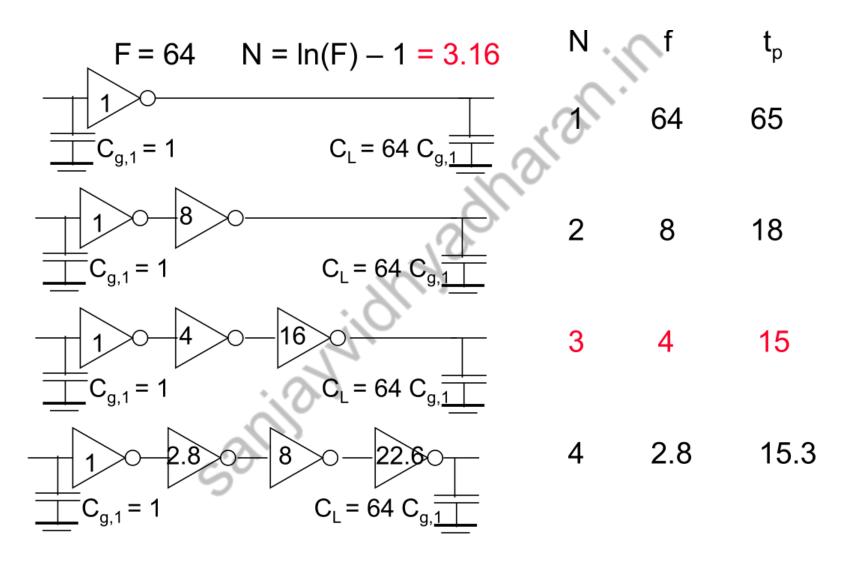

The optimum size of each inverter is the geometric mean of its neighbours – meaning that if each inverter is sized up by the same factor f wrt the preceding gate, it will have the same effective fan-out and the same delay

$$f = \sqrt[N]{C_L/C_{g,1}} = \sqrt[N]{F}$$

where the overall effective fan-out of the circuit is

$$F = C_L / C_{g,1}$$

and the minimum delay through the inverter chain is

$$t_p = N t_{p0} (1 + (\sqrt[N]{F}) / \gamma)$$

The relationship between t<sub>p</sub> and F is linear for one inverter, square root for two, etc.

2/12/2022

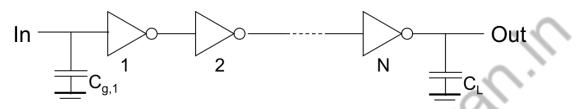

What is the optimal value for N given F (= f<sup>N</sup>)?

- if the number of stages is too large, the intrinsic delay of the stages becomes dominate

- if the number of stages is too small, the effective fan-out of each stage becomes dominate

- The optimum N is found by differentiating the minimum delay expression divided by the number of stages and setting the result to 0, giving

$\gamma + \sqrt[N]{F} - (\sqrt[N]{F} \ln(F))/N = 0$  and  $f = e^{(1 + \gamma/f)}$

- □ For  $\gamma$  = 0 (ignoring self-loading) N = In(F) and the effective-fan out (tapering factor) is f = e = 2.718

- □ For  $\gamma$  = 1 (the typical case) N = In(F) 1 and the effective fan-out (tapering factor) is f = 3.6

2/12/2022

- Choosing f larger than optimum has little effect on delay and reduces the number of stages (and area).

- So it is common practice to use f = 4 (for  $\gamma = 1$ ) and reduce N

- Too many stages has a substantial negative impact on delay

COMMUNICATION

2/12/2022

ELECTRICAL

**ELECTRONICS**

2/12/2022

COMMUNICATION

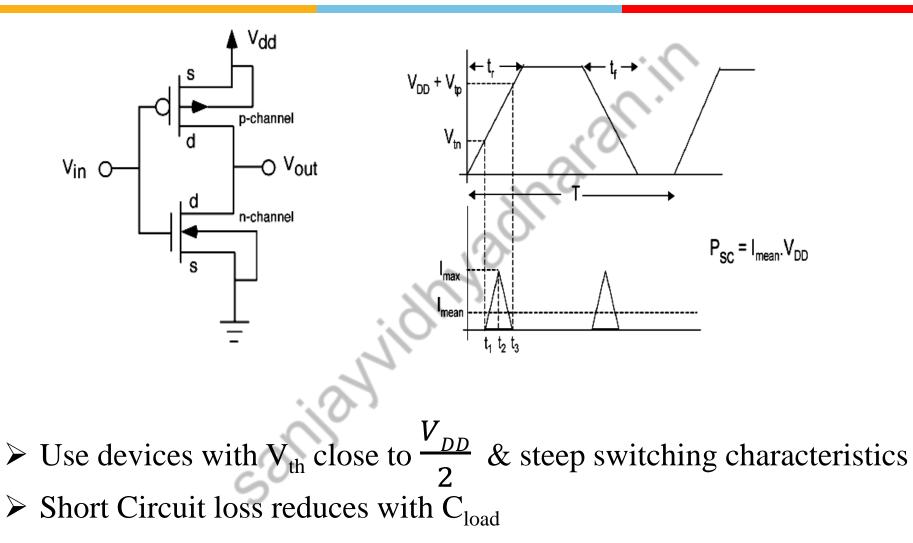

## **Short Circuit Loss**

#### ELECTRONICS COMMUNICATION

ELECTRICAL

#### **INSTRUMENTATION**

## **Short Circuit Loss**

> Short Circuit loss reduces with  $C_{load}$

**ELECTRICAL**

**ELECTRONICS**

#### COMMUNICATION

**INSTRUMENTATION**

## **Switching Loss**

Energy dissipated in nMOSFET during discharging =  $\frac{1}{2}$ .  $V_{DD}^2$ .  $C_L$ Power Consumption = Frequency.  $V_{DD}^2$ .  $C_L$

**ELECTRICAL**

ELECTRONICS

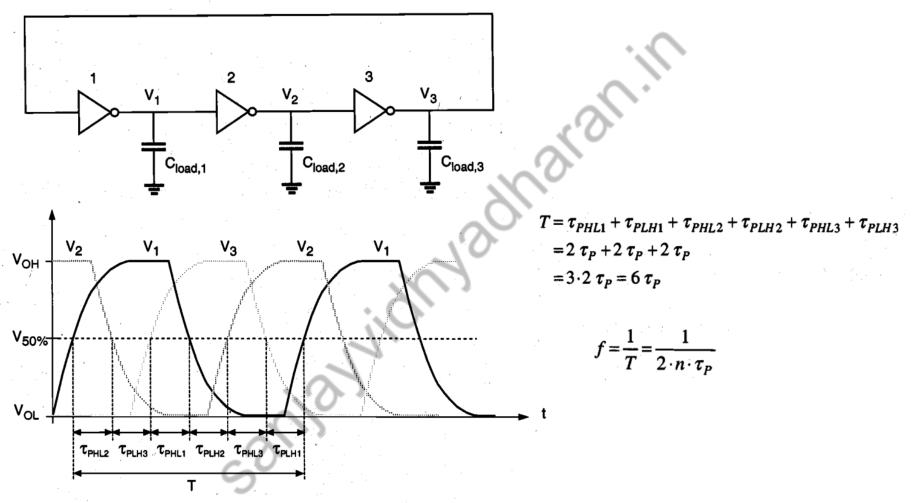

#### **Ring Oscillator Circuit**

The ring oscillator circuit can be used as a very simple pulse generator

Utilized to characterize a particular design and/or a new fabrication process.

ELECTRICAL EL

ELECTRONICS

COMMUNICATION

# Thank you

2/12/2022