# VLSI SYSTEMS AND ARCHITECTURE 2021-22 Lab-1

# Implementation of Majority Circuit using **Gate Level Modeling**

By Dr. Sanjay Vidhyadharan

**ELECTRICAL**

#### HDL

A specialized computer language used to describe the structure and behavior of electronic circuits, most commonly, digital logic circuits

More complex

Verilog and VHDL are common examples

Describe the behavior of digital circuits

#### SOFTWARE LANGUAGE

A computer language used to write a set of instructions to allow the CPU to perform a specific task

Not as complex

Java, C, C++, Python, PHP, etc. are common examples

Helps to develop various applications

Visit www.PEDIAA.com

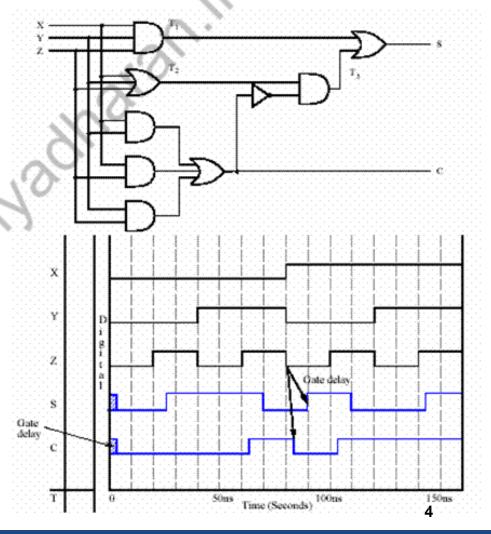

# Logic Simulation

- A simulator interprets the HDL description and produces a readable output, such as a timing diagram, that predicts how the hardware will behave before its is actually fabricated.

- ➤ Simulation allows the detection of functional errors in a design without having to physically create the circuit.

- The stimulus that tests the functionality of the design is called a test bench.

- > To simulate a digital system

- > Design is first described in HDL

- ➤ Verified by simulating the design and checking it with a test bench which is also written in HDL.

# Logic Simulation

Logic simulation is a fast, accurate method of analyzing a circuit to see its waveforms

- There are two standard HDL's that are supported by IEEE.

- VHDL (Very-High-Speed Integrated Circuits Hardware Description Language) - Sometimes referred to as VHSIC HDL, this was developed from an initiative by US. Dept. of Defense.

- Verilog HDL developed by Cadence Data systems and later transferred to a consortium called *Open Verilog International* (OVI).

2/19/2022 5

# Verilog

- ➤ Verilog HDL has a syntax that describes precisely the legal constructs that can be used in the language.

- ➤ It uses about 100 keywords pre-defined, lowercase, identifiers that define the language constructs.

- Example of keywords: *module*, *endmodule*, *input*, *output* wire, and, or, not, etc.,

- Any text between two slashes (//) and the end of line is interpreted as a comment.

- ➤ Blank spaces are ignored and names are case sensitive.

#### **Link for Xilinx Download**

https://www.xilinx.com/member/forms/download/xef.html?filename=Xilinx\_ISE\_1 4.7\_Win10\_14.7\_VM\_0213\_1.zip

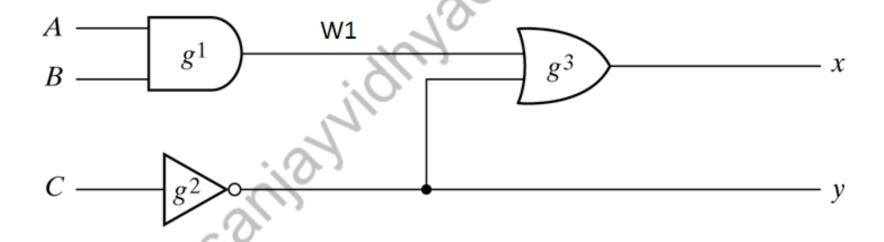

# **Simple Circuit for Demonstration**

# **Gate Level Modelling**

#### Simple Circuit to demonstrate HDL

### Simple Circuit for Demonstration

#### **Gate Level Modelling**

# $A \longrightarrow g^1$ W1 $g^3$

#### **Verilog Code**

```

module Simple_circuit (input A, input B, input C, output x, output y); wire w1;

```

```

and g1 (w1,A,B); // and gate instance not g2 (y,C); or g3 (x,w1,y);

```

endmodule

#### **Problem Definition**

# **Problem 1: Implement the Majority Circuit**

| A | В | С  | F |

|---|---|----|---|

| 0 | 0 | 0  | 0 |

| 0 | 0 | 1  | 0 |

| 0 | 1 | 0  | 0 |

| 0 | 1 | 1  | 1 |

| 1 | 0 | 0  | 0 |

| 1 | 0 | 10 | 1 |

| 1 | 1 | 0  | 1 |

| 1 | 1 | 1  | 1 |

$$F = AB + BC + CA + ABC$$

$$F = AB + BC + CA$$

Thank you