INSTRUMENTATION

# VLSI Design : 2021-22 Lecture 4 CMOS Technology

# By Dr. Sanjay Vidhyadharan

ELECTRICAL ELECTRONICS COMMUNICATION

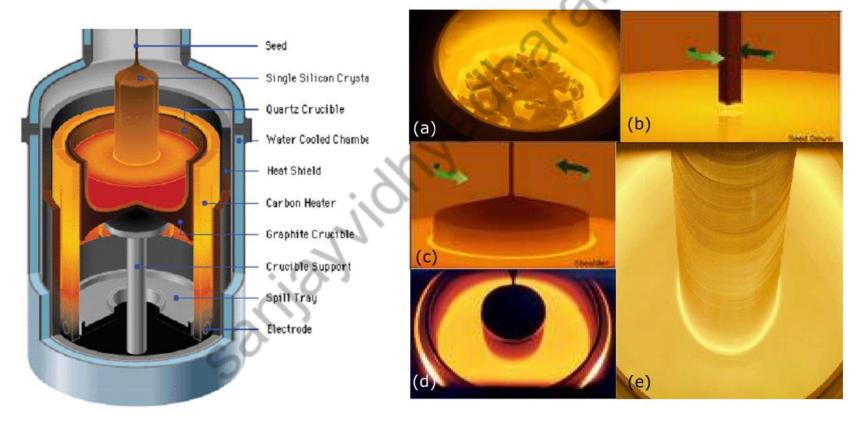

# **Crystal Growth**

#### 99.999999999% pure Si is needed for IC fabrication!! i.e.,1mg of sugar dissolved in an Olympic-size swimming pool

https://www.youtube.com/watch?v=skRmyhSOu28

**ELECTRICAL**

**ELECTRONICS**

#### COMMUNICATION

2

**Crystal Growth**

https://www.youtube.com/watch?v=skRmyhSOu28

**ELECTRICAL**

ELECTRONICS

COMMUNICATION

3

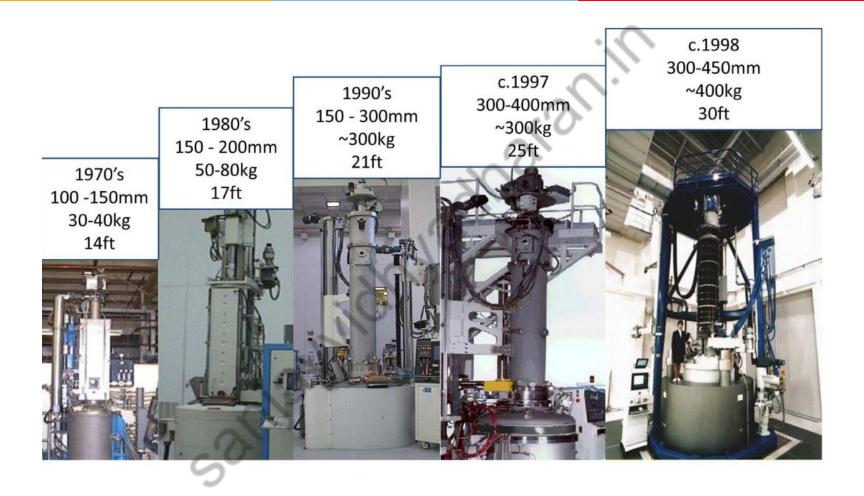

# **Silicon Ingot**

Examples of progress in Czochralski crystal puller

ELECTRONICS COMMUNICATION

**ELECTRICAL**

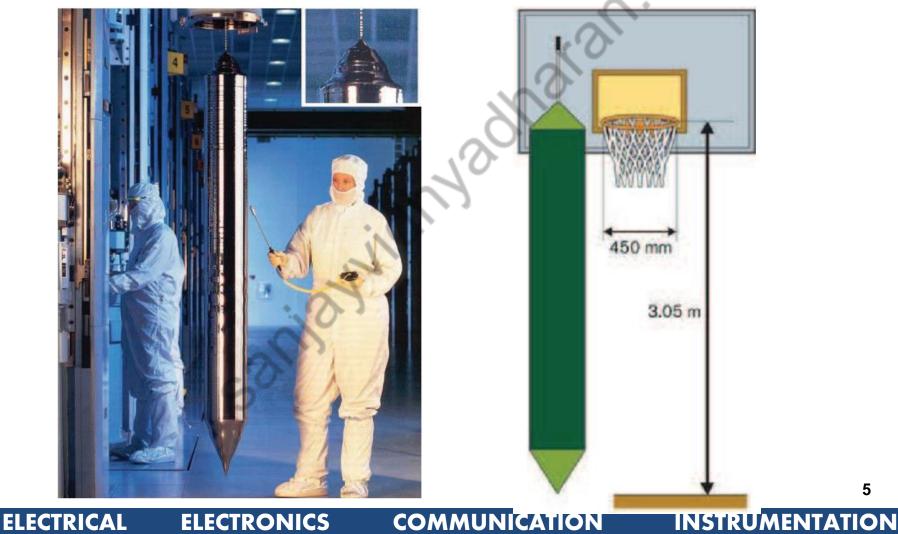

# **Silicon Ingot**

In 2017, the wafer diameter has reached 18 inch (i.e., 450 mm) and weight is several hundred kilograms

# **Choosing a Substrate**

> Type of the substrate (p- or n-type)?

Prefer P-type

### > Resistivity or doping level?

- Substrate doping level 10<sup>15</sup> cm<sup>-3</sup> → resistivity 25-50 ohm-cm

- **Crystal orientation (111) or (100)?**

- Prefer (100) surface in order to have better Si/SiO<sub>2</sub> interface and few imperfection (i.e., unsatisfied bonds)

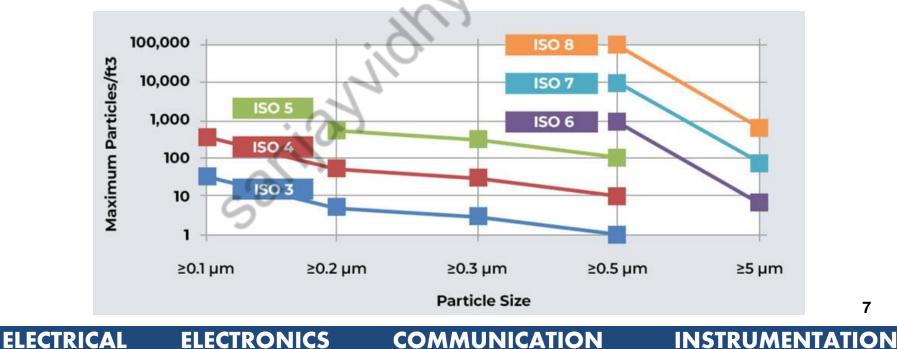

## Cleanroom

- Ambient air contains 35,000,000 particles per cubic meter with 0.5 mm and larger  $\succ$ in diameter!

- Clean Room : It is a controlled environment with low level of pollutants such as  $\succ$ dust, airborne microbes, aerosol particles, and chemical vapors.

- Semiconductor fabs follow the ISO 14644 standard. Specification for device  $\succ$ fabrication cleanrooms vary based on process type, line width, and wafer size requirements. Semiconductor cleanrooms requirements can range from ISO-4 (Class 10) to ISO-6 (Class 1,000) cleanrooms.

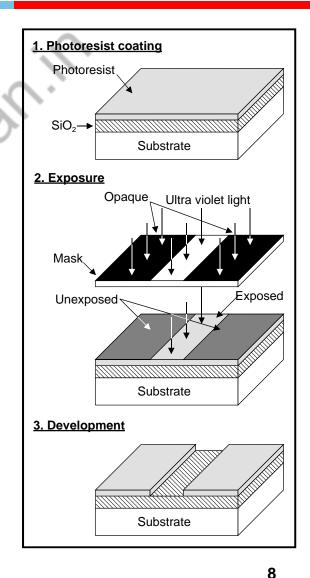

# Lithography

#### **Basic sequence**

- The surface to be patterned is:

- spin-coated with photoresist

- the photoresist is dehydrated in an oven (photo resist: light-sensitive organic polymer)

- The photoresist is exposed to ultra-violet light:

- For a positive photoresist exposed areas become soluble and non exposed areas remain hard

- The soluble photoresist is chemically removed (development).

- The patterned photoresist will now serve as an etching mask for the SiO<sub>2</sub>

1/23/2022

COMMUNICATION

# Lithography

- The SiO<sub>2</sub> is etched away leaving the substrate exposed:

- the patterned resist is used as the etching mask

- Ion Implantation:

- the substrate is subjected to highly energized donor or acceptor atoms

- The atoms impinge on the surface and travel below it

- The patterned silicon SiO<sub>2</sub> serves as an implantation mask

- The doping is further driven into the bulk by a thermal cycle

1/23/2022

COMMUNICATION IN

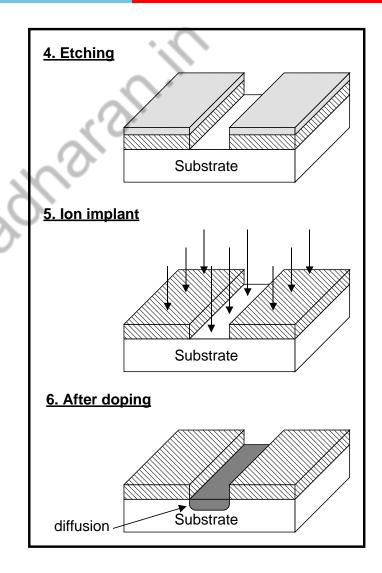

## Lithography

#### **Patterning a layer above the silicon surface**

**ELECTRONICS**

**ELECTRICAL**

COMMUNICATION

**INSTRUMENTATION**

10

# **Basic VLSI Fabrication Steps**

- 1. Crystal growth

- Crystal orientation, type and resistivity

- 2. Photolithography

- 3. Oxidation

- Dry or wet oxidation, duration of oxidation

COMMUNICATION

- 4. Diffusion

- 5. Epitaxy

ELECTRICAL

6. Ion-implantation

ELECTRONICS

- 7. Annealing

- 8. Metallization

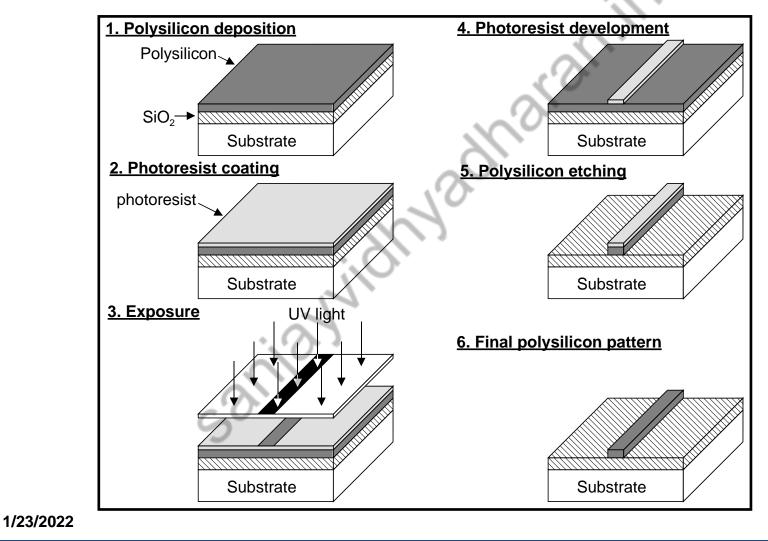

## Oxidation

COMMUNICATION

•slow growth of oxide

•high density

•high breakdown voltage

#### **ELECTRICAL**

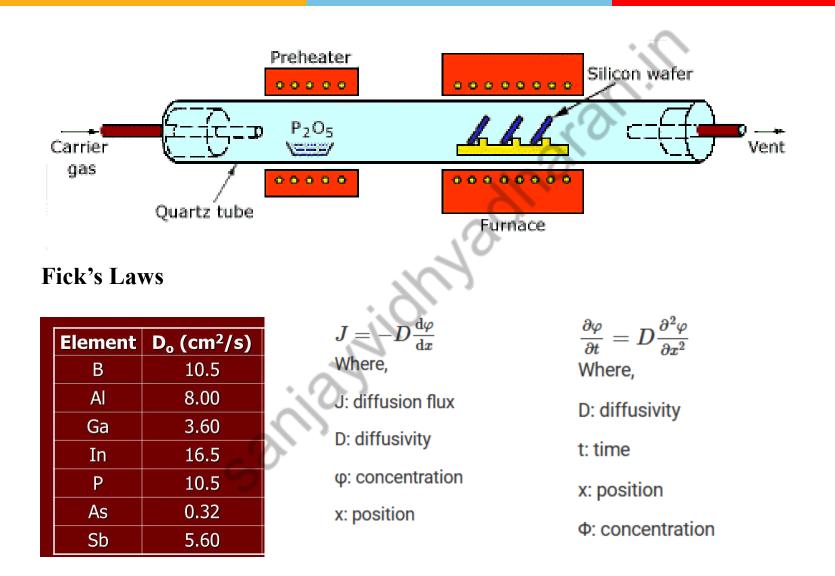

## Diffusion

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

13

COMMUNICATION

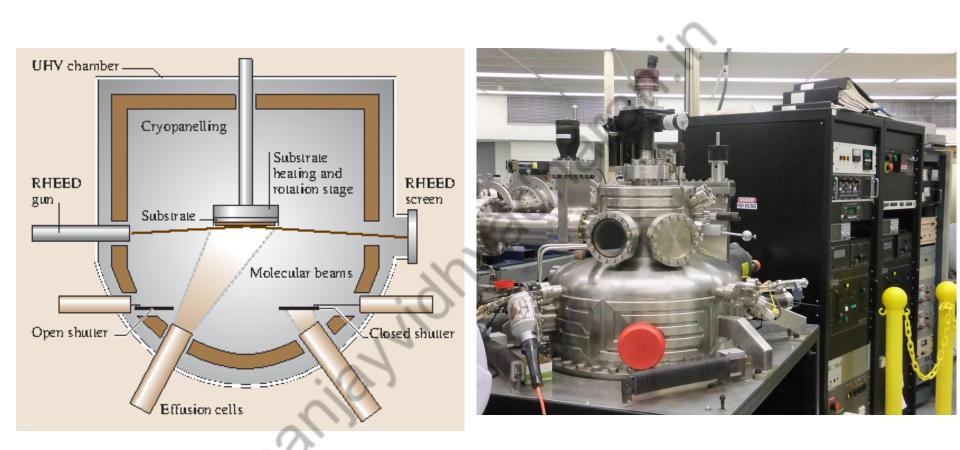

**Reflection high energy electron diffraction**

**ELECTRONICS**

**ELECTRICAL**

**Epitaxy**

The chemical reactions used for the production of undoped and doped epitaxial

```

silicon and Si<sub>1-x</sub>Ge<sub>x</sub> include:

•SiCl<sub>4</sub> + 2H<sub>2</sub> \rightarrow Si + 4HCl (~1200°C)

•SiHCl<sub>3</sub> + H<sub>2</sub> \rightarrow Si + 3HCl (~1150°C)

•SiH<sub>2</sub>Cl<sub>2</sub> \rightarrow Si + 2HCl (~1100°C)

•SiH<sub>4</sub> \rightarrow Si + 2H<sub>2</sub> (~1050°C)

•GeH<sub>4</sub> \rightarrow Ge + 2H<sub>2</sub>

•B<sub>2</sub>H<sub>6</sub> \rightarrow 2B + 3H<sub>2</sub>

•PH<sub>3</sub> \rightarrow P + 3/2H<sub>2</sub>

•AsH<sub>3</sub> \rightarrow As + 3/2H<sub>2</sub>

```

15

ELECTRICAL

COMMUNICATION

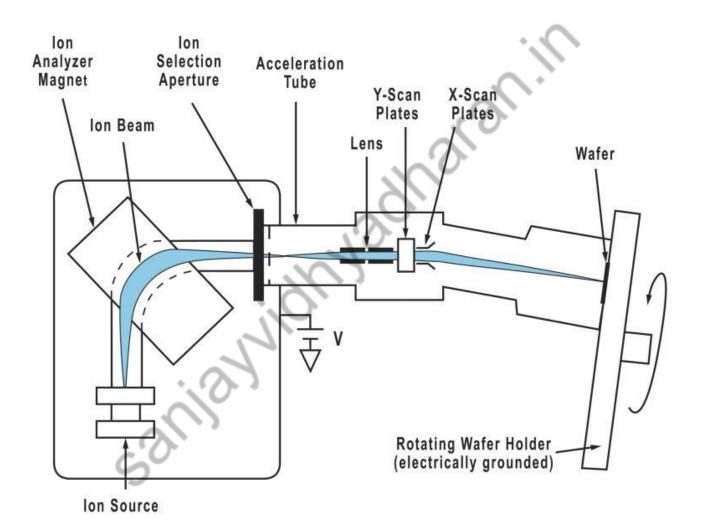

## **Ion-implantation**

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

## **Ion-implantation**

17

**ELECTRICAL**

ELECTRONICS

COMMUNICATION

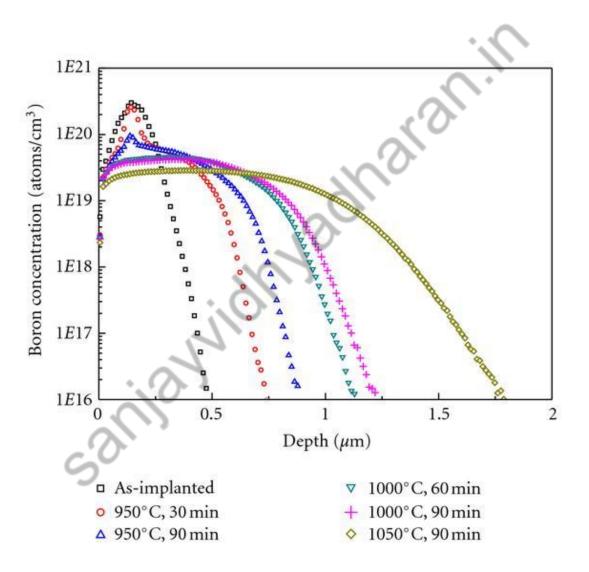

## Annealing

**ELECTRONICS**

**ELECTRICAL**

COMMUNICATION

18

# How do you fabricate??

19

**ELECTRICAL**

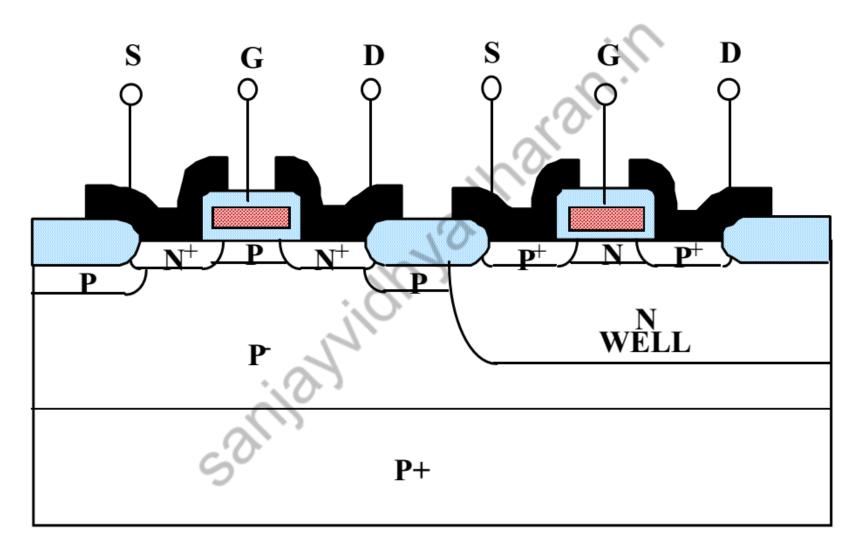

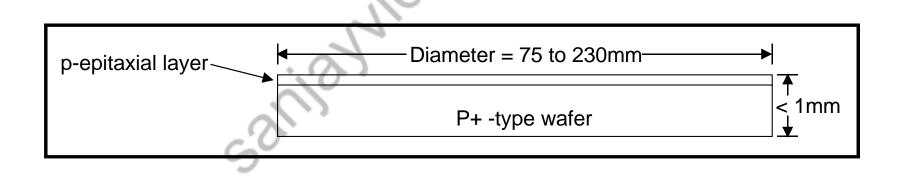

#### 0. Start:

ELECTRICAL

- For an n-well process the starting point is a p-type silicon wafer:

- wafer: typically 75 to 230mm in diameter and less than 1mm thick

#### 1. Epitaxial growth:

ELECTRONICS

- A single p-type single crystal film is grown on the surface of the wafer by:

- subjecting the wafer to high temperature and a source of dopant material

- The epi layer is used as the base layer to build the devices

COMMUNICATION

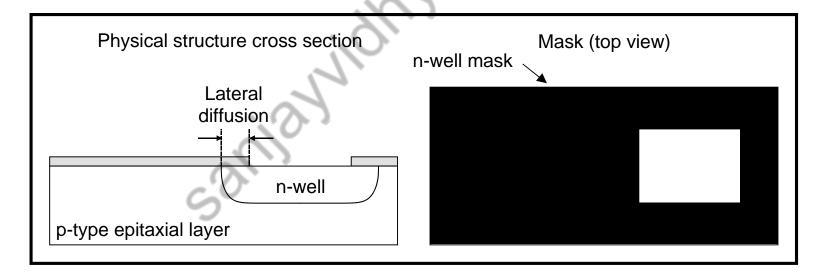

#### 2. N-well Formation:

ELECTRICAL

- PMOS transistors are fabricated in n-well regions

- The first mask defines the n-well regions

ELECTRONICS

- N-well's are formed by ion implantation or deposition and diffusion

- Lateral diffusion limits the proximity between structures

- Ion implantation results in shallower wells compatible with today's fineline processes

COMMUNICATION

21

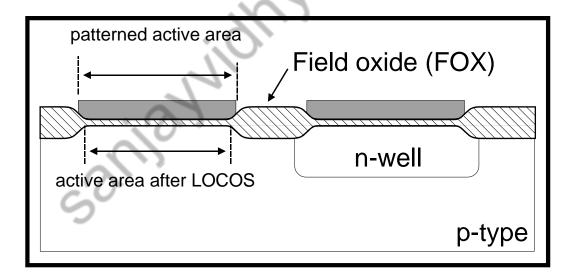

#### 3. Active area definition:

- Active area:

ELECTRICAL

- planar section of the surface where transistors are build

- defines the gate region (thin oxide)

- defines the n+ or p+ regions

**ELECTRONICS**

- A thin layer of  $SiO_2$  is grown over the active region and covered with silicon nitride

| Stress-relief oxide | Silicon Nitride | Active mask |

|---------------------|-----------------|-------------|

|                     | S               |             |

|                     | n-well          |             |

| p-type              |                 |             |

COMMUNICATION

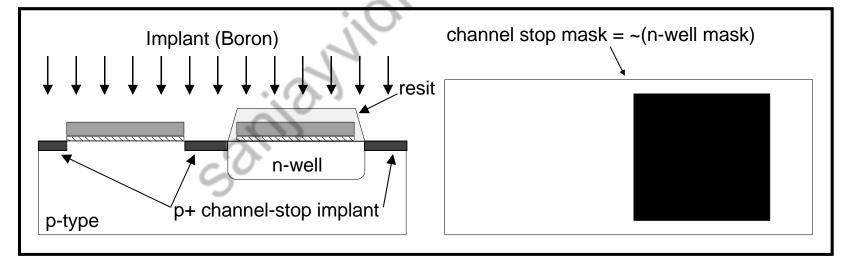

#### 4. Isolation:

ELECTRICAL

- Parasitic (unwanted) FET's exist between unrelated transistors (Field Oxide FET's)

- Source and drains are existing source and drains of wanted devices

- Gates are metal and polysilicon interconnects

**ELECTRONICS**

- The threshold voltage of FOX FET's are higher than for normal FET's

#### 4.1 Channel-stop implant

The silicon nitride (over n-active) and the photoresist (over n-well) act as masks for the channel-stop implant

COMMUNICATION

INSTRUMENTATION

23

#### 4.2 Local oxidation of silicon (LOCOS)

- The photoresist mask is removed

**ELECTRONICS**

ELECTRICAL

- The  $SiO_2/SiN$  layers will now act as a masks

- The thick field oxide is then grown by:

- exposing the surface of the wafer to a flow of oxygen-rich gas

- The oxide grows in both the vertical and lateral directions

- This results in a active area smaller than patterned

COMMUNICATION

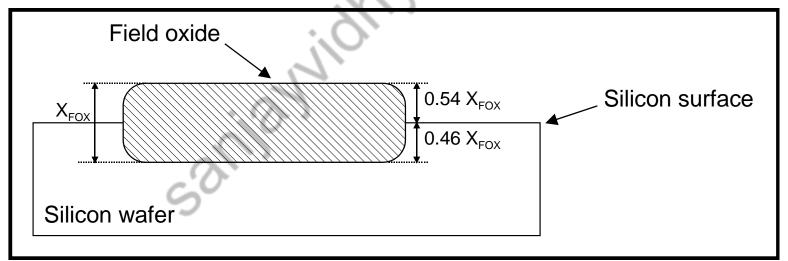

- Silicon oxidation is obtained by:

- Heating the wafer in a oxidizing atmosphere:

- Wet oxidation: water vapor, T = 900 to  $1000^{\circ}C$  (rapid process)

- Dry oxidation: Pure oxygen, T = 1200°C (high temperature required to achieve an acceptable growth rate)

- Oxidation consumes silicon

ELECTRONICS

ELECTRICAL

- $SiO_2$  has approximately twice the volume of silicon

- The FOX is recedes below the silicon surface by  $0.46X_{FOX}$

COMMUNICATION

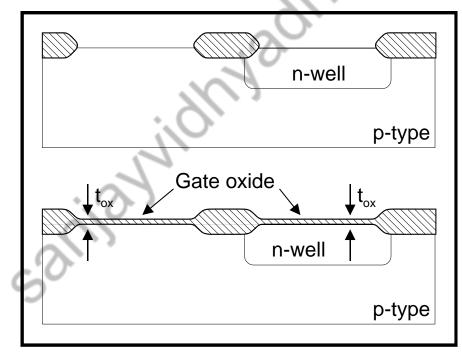

#### 5. Gate oxide growth

ELECTRICAL

- The nitride and stress-relief oxide are removed

- The devices threshold voltage is adjusted by:

ELECTRONICS

- adding charge at the silicon/oxide interface

- The well controlled gate oxide is grown with thickness  $t_{ox}$

COMMUNICATION

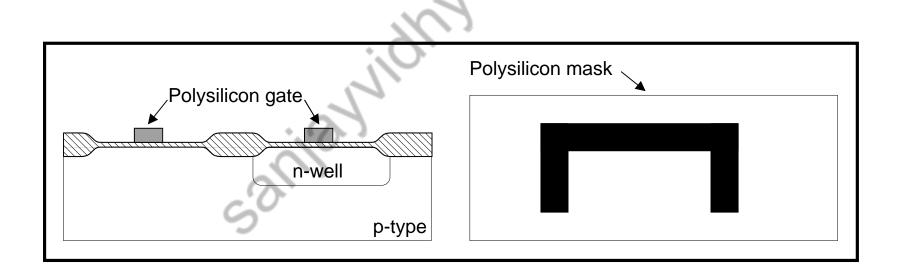

#### 6. Polysilicon deposition and patterning

ELECTRONICS

ELECTRICAL

- A layer of polysilicon is deposited over the entire wafer surface

- The polysilicon is then patterned by a lithography sequence

- All the MOSFET gates are defined in a single step

- The polysilicon gate can be doped (n+) while is being deposited to lower its parasitic resistance (important in high speed fine line processes)

COMMUNICATION

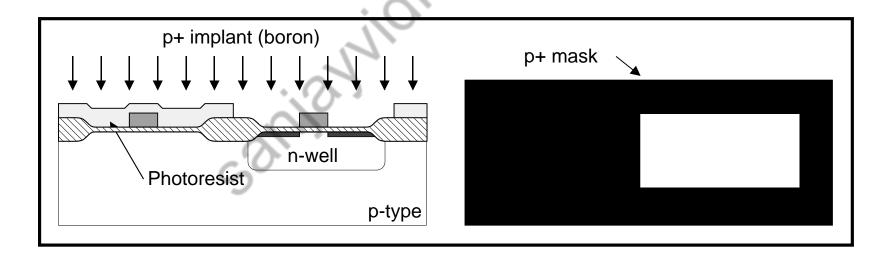

#### 7. PMOS formation

ELECTRICAL

- Photoresist is patterned to cover all but the p+ regions

- A boron ion beam creates the p+ source and drain regions

- The polysilicon serves as a mask to the underlying channel

- This is called a **self-aligned process**

ELECTRONICS

- It allows precise placement of the source and drain regions

- During this process the gate gets doped with p-type impurities

- Since the gate had been doped n-type during deposition, the final type (n or p) will depend on which dopant is dominant

COMMUNICATION

28

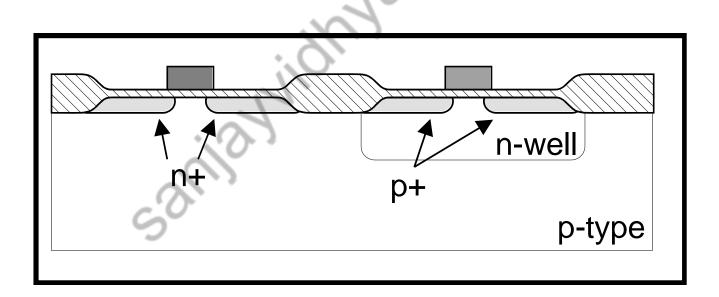

#### 8. NMOS formation

ELECTRICAL

- Photoresist is patterned to define the n+ regions

- Donors (arsenic or phosphorous) are ion-implanted to dope the n+ source and drain regions

- The process is self-aligned

**ELECTRONICS**

- The gate is n-type doped

| n+ implant (arsenic or phosphorous) | n+ mask |

|-------------------------------------|---------|

| n-well                              |         |

| Photoresist                         |         |

| p-type                              |         |

COMMUNICATION

#### 9. Annealing

ELECTRICAL

**ELECTRONICS**

- After the implants are completed a thermal annealing cycle is executed

- This allows the impurities to diffuse further into the bulk

- After thermal annealing, it is important to keep the remaining process steps at as low temperature as possible

COMMUNICATION

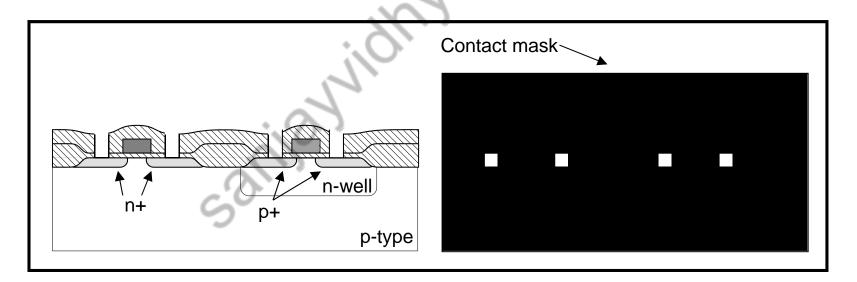

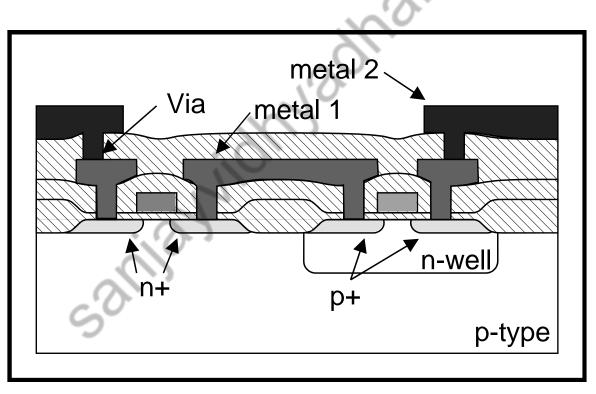

#### **10.** Contact cuts

ELECTRICAL

ELECTRONICS

- The surface of the IC is covered by a layer of CVD oxide

- The oxide is deposited at low temperature (LTO) to avoid that underlying doped regions will undergo diffusive spreading

- Contact cuts are defined by etching SiO<sub>2</sub> down to the surface to be contacted

- These allow metal to contact diffusion and/or polysilicon regions

COMMUNICATION

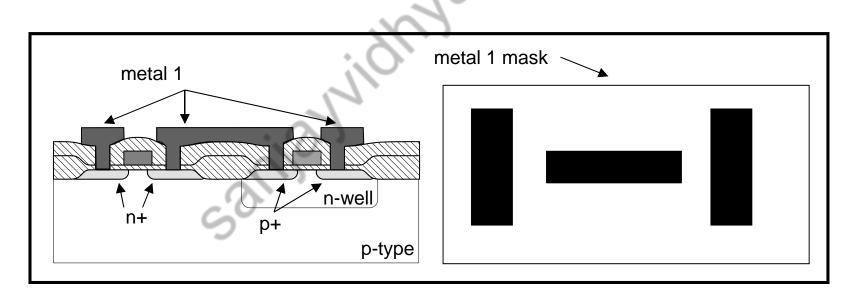

#### 11. Metal 1

**ELECTRICAL**

**ELECTRONICS**

A first level of metallization is applied to the wafer surface and selectively etched to produce the interconnects

COMMUNICATION

#### 12. Metal 2

**ELECTRICAL**

- Another layer of LTO CVD oxide is added

- Via openings are created

- Metal 2 is deposited and patterned

**ELECTRONICS**

COMMUNICATION

#### 13. Over glass and pad openings

- A protective layer is added over the surface:

- The protective layer consists of:

- A layer of SiO<sub>2</sub>

- Followed by a layer of silicon nitride

- The SiN layer acts as a diffusion barrier against contaminants (passivation)

- Finally, contact cuts are etched, over metal 2, on the passivation to allow for wire bonding.

# **Detailed Mask Views**

- Six masks

- n-well

- Polysilicon

- n+ diffusion

- p+ diffusion

**ELECTRONICS**

- Contact

- Metal

ELECTRICAL

COMMUNICATION

varan.

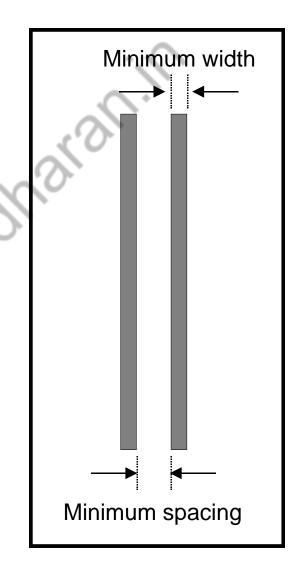

- The limitations of the patterning process give rise to a set of mask design guidelines called design rules

- Design rules are a set of guidelines that specify the minimum dimensions and spacings allowed in a layout drawing

- Violating a design rule might result in a non-functional circuit or in a highly reduced yield

- The design rules can be expressed as:

ELECTRONICS

ELECTRICAL

- A list of minimum feature sizes and spacings for all the masks required in a given process

- Based on single parameter  $\lambda$  that characterize the linear feature (e.g. the minimum grid dimension).  $\lambda$  base rules allow simple scaling. Generally  $\lambda = L/2$ .

COMMUNICATION

COMMUNICATION

- Minimum line-width:

- smallest dimension permitted for any object in the layout drawing (minimum feature size)

- Minimum spacing:

- smallest distance permitted between the edges of two objects

- This rules originate from the resolution of the optical printing system, the etching process, or the surface roughness

Minimum line width of a process is  $2\lambda$

**ELECTRONICS**

ELECTRICAL

COMMUNICATION

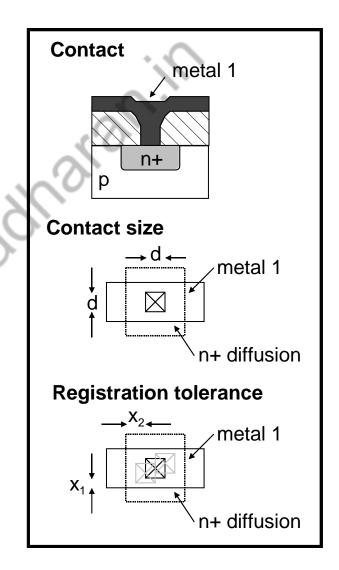

• Contacts and vias:

ELECTRICAL

- minimum size limited by the lithography process

- large contacts can result in cracks and voids

- Dimensions of contact cuts are restricted to values that can be reliably manufactured

- A minimum distance between the edge of the oxide cut and the edge of the patterned region must be specified to allow for misalignment tolerances (registration errors)

**ELECTRONICS**

COMMUNICATION

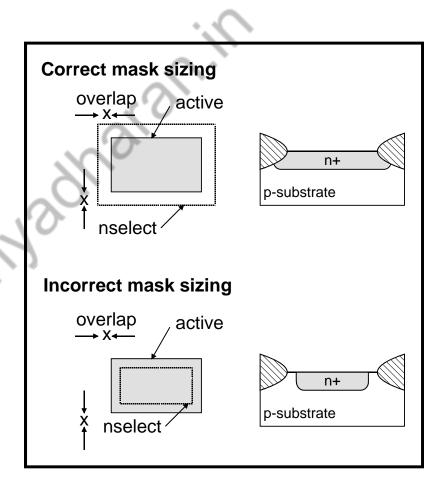

• MOSFET rules

ELECTRICAL

- n+ and p+ regions are formed in two steps:

- the <u>active</u> area openings allow the implants to penetrate into the silicon substrate

- the <u>nselect</u> or <u>pselect</u> provide photoresist openings over the active areas to be implanted

- Since the formation of the diffusions depend on the overlap of two masks, the nselect and pselect regions must be larger than the corresponding active areas to allow for misalignments

**ELECTRONICS**

COMMUNICATION

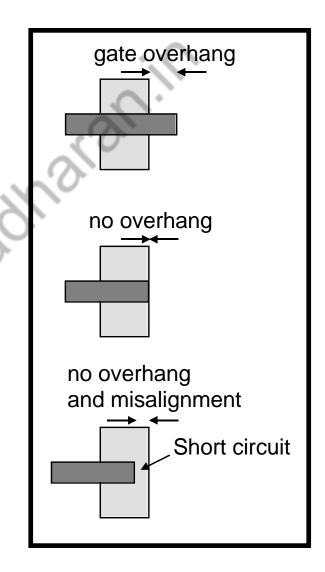

• Gate overhang:

ELECTRICAL

- The gate must overlap the active area by a minimum amount

- This is done to ensure that a misaligned gate will still yield a structure with separated drain and source regions

- A modern process has may hundreds of rules to be verified

- Programs called <u>Design Rule</u>

<u>Checkers assist the designer in</u>

that task

**ELECTRONICS**

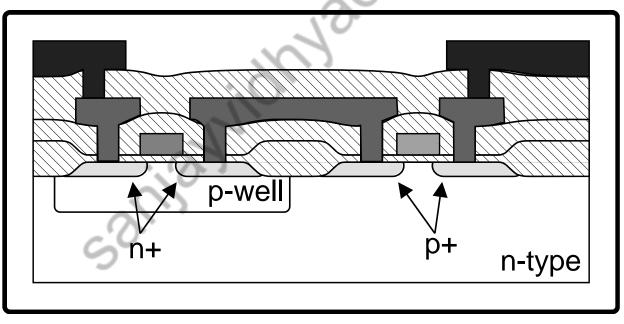

#### • P-well process

ELECTRICAL

- NMOS devices are build on a implanted p-well

- PMOS devices are build on the substrate

ELECTRONICS

- P-well process moderates the difference between the p- and the ntransistors since the P devices reside in the native substrate

- Advantages: better balance between p- and n-transistors

COMMUNICATION

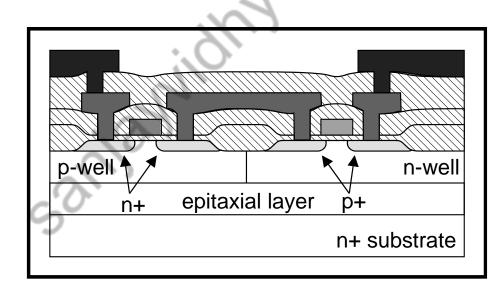

#### • Twin-well process

- n+ or p+ substrate plus a lightly doped epi-layer (latchup prevention)

- wells for the n- and p-transistors

- Advantages, simultaneous optimization of p- and n-transistors:

- threshold voltages

- body effect

- gain

42

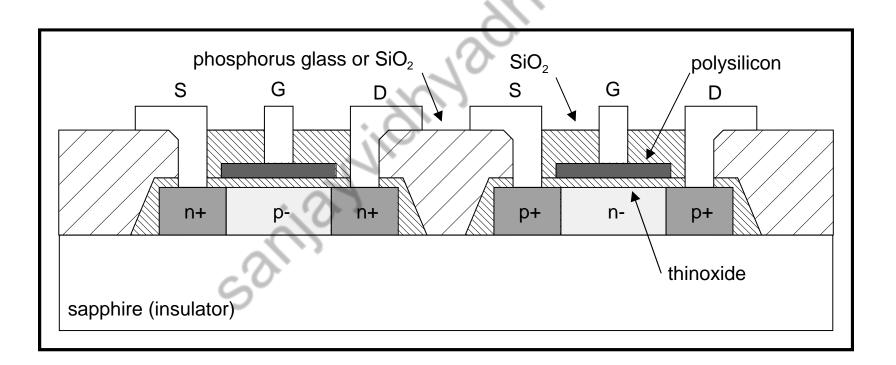

• Silicon On Insulator (SOI)

**ELECTRONICS**

**ELECTRICAL**

- Islands of silicon on an insulator form the transistors

COMMUNICATION

43

#### **Silicon On Insulator (SOI)**

- Advantages:

- No wells  $\Rightarrow$  denser transistor structures

- Lower substrate capacitances

- Very low leakage currents

- No FOX FET exists between unrelated devices

- No latchup

- No body-effect:

- However, the absence of a backside substrate can give origin to the "kink effect"

COMMUNICATION

- Radiation tolerance

- Disadvantages:

ELECTRICAL

- Absence of substrate diodes (hard to implement protection circuits)

- Higher number of substrate defects  $\Rightarrow$  lower gain devices

- More expensive processing

ELECTRONICS

# **Process Enhancements**

- Up to six metal levels in modern processes

- Copper for metal levels 2 and higher

- Stacked contacts and vias

- Chemical Metal Polishing for technologies with several metal levels

COMMUNICATION

- For analogue applications some processes offer:

- capacitors

- resistors

ELECTRICAL

bipolar transistors (BiCMOS)

ELECTRONICS

# Thank you

COMMUNICATION

1/23/2022

**ELECTRICAL**

**ELECTRONICS**