# Advanced VLSI Design: 2021-22 Lecture 2 Sequential Circuits: Latch and Flip-flops

By Dr. Sanjay Vidhyadharan

ELECTRICAL

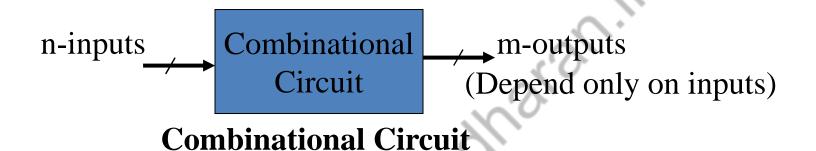

# Combinational vs. Sequential Circuits

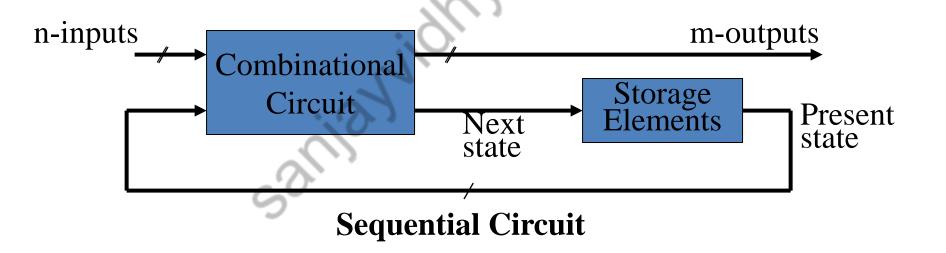

# Latch vs. Flip-flop

- Latch: Level sensitive

- a.k.a. transparent latch, D latch

- Flip-flop: edge triggered

- A.k.a. master-slave flip-flop, D flip-flop, D register

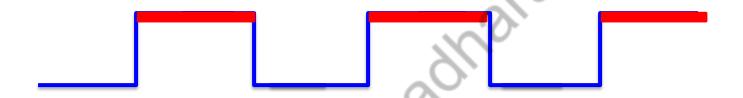

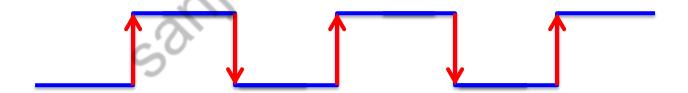

- Timing Diagrams

- Transparent

- Opaque

- Edge-trigger

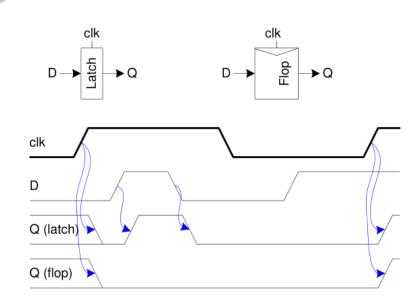

## Latch

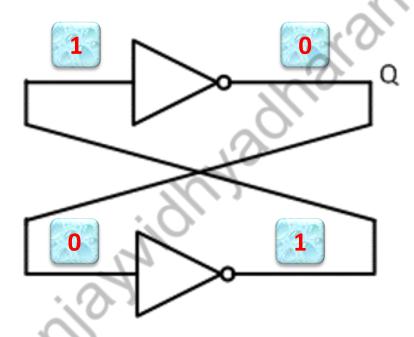

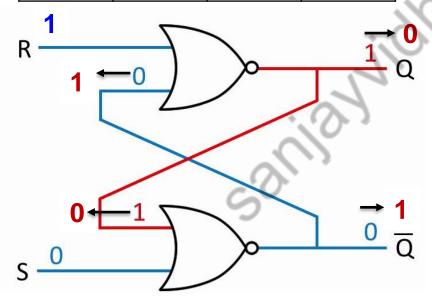

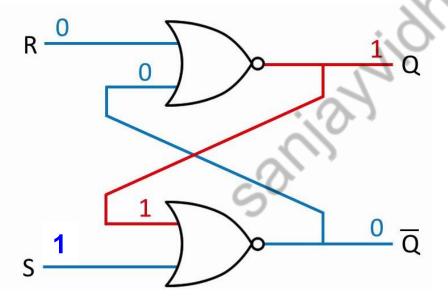

## Storing 1

Stores 1 as Long as Power Supply is Provided

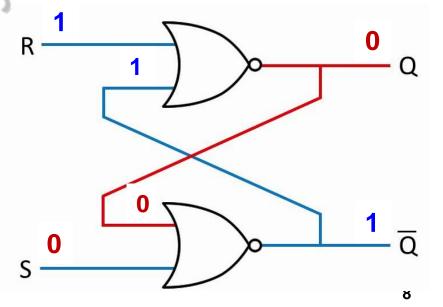

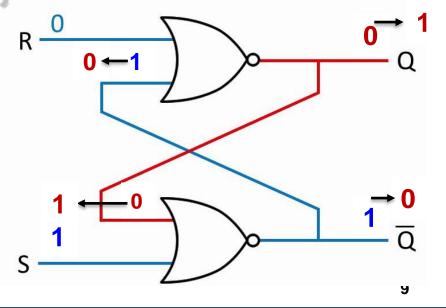

## Latch

## Storing 0

Stores 0 as Long as Power Supply is Provided

## Latch

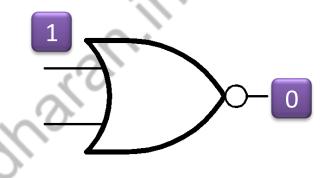

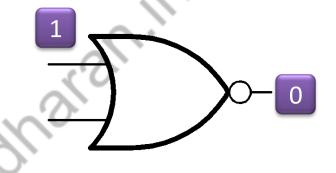

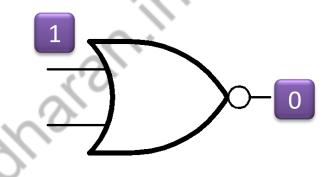

How to Write Data into a Latch?

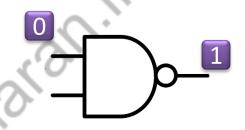

We are going to use this property of NOR and NAND to write data into the latch

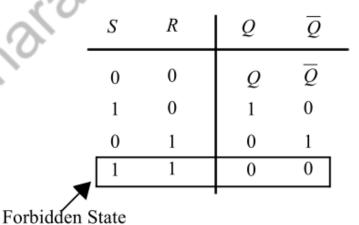

| S | R | Q | $\overline{Q}$    |

|---|---|---|-------------------|

| 0 | 0 | Q | $\overline{m{Q}}$ |

| 0 | 1 | 0 | 1                 |

| 1 | 0 | 1 | 0                 |

| 1 | 1 | 0 | 0                 |

| S | R | Q | $\overline{Q}$    |

|---|---|---|-------------------|

| 0 | 0 | Q | $\overline{m{Q}}$ |

| 0 | 1 | 0 | 1                 |

| 1 | 0 | 1 | 0                 |

| 1 | 1 | 0 | 0                 |

| S | R | Q | $\overline{Q}$    |

|---|---|---|-------------------|

| 0 | 0 | Q | $\overline{m{Q}}$ |

| 0 | 1 | 0 | 1                 |

| 1 | 0 | 1 | 0                 |

| 1 | 1 | 0 | 0                 |

| S | R | Q | $\overline{Q}$    |

|---|---|---|-------------------|

| 0 | 0 | Q | $\overline{m{Q}}$ |

| 0 | 1 | 0 | 1                 |

| 1 | 0 |   | 0                 |

| 1 |   | 0 | 0                 |

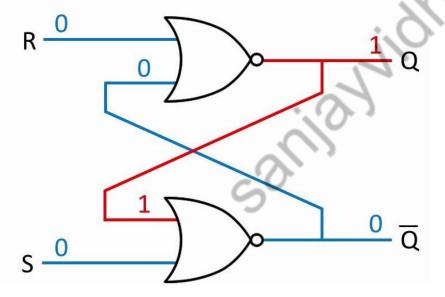

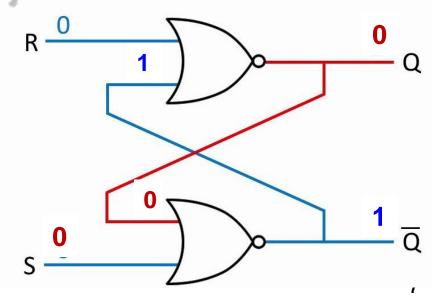

No change

Reset Q = 0

Set Q = 1

Forbidden

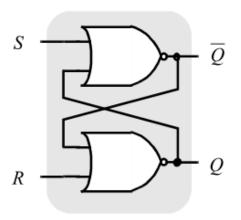

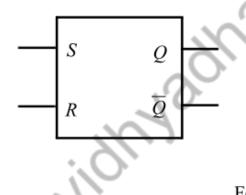

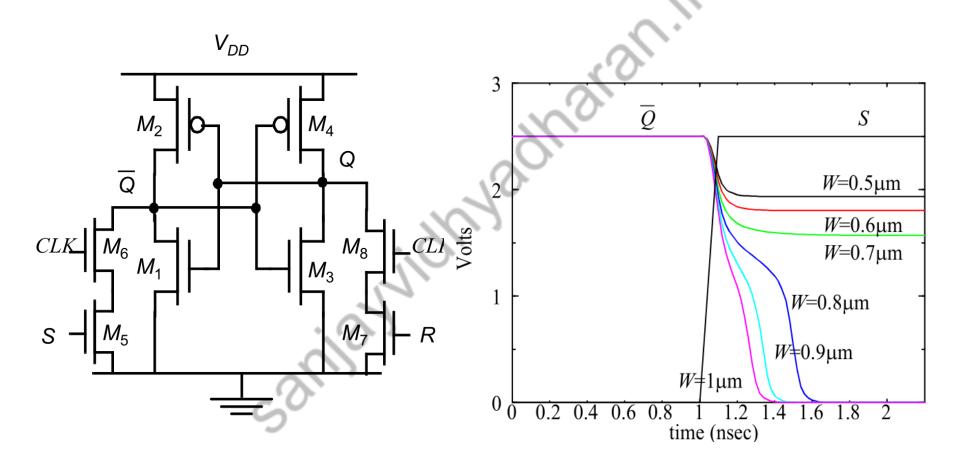

#### **SR Latch with NOR Gates**

(a) Schematic diagram

(b) Logic symbol

(c) Characteristic table

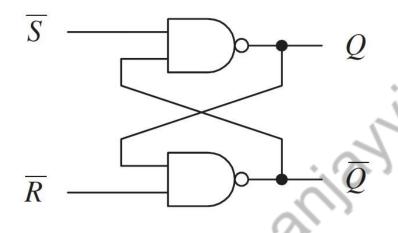

#### **SR Latch with NAND Gates**

| S' | R' | Q | Q' |

|----|----|---|----|

| 0  | 0  | 1 | 1  |

| 0  | 1  | 1 | 0  |

| 1  | 0  | 0 | 1  |

| 1  | 1  | Q | Ŷ  |

Forbidden

Set

Reset

No change

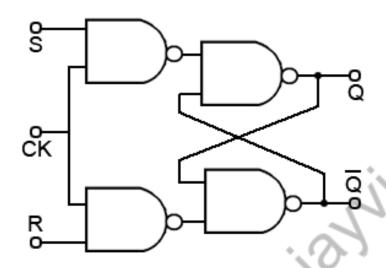

#### **Clocked SR Latch**

**NAND Implementation**

**AND-NOR Implementation**

#### **Clocked SR Latch**

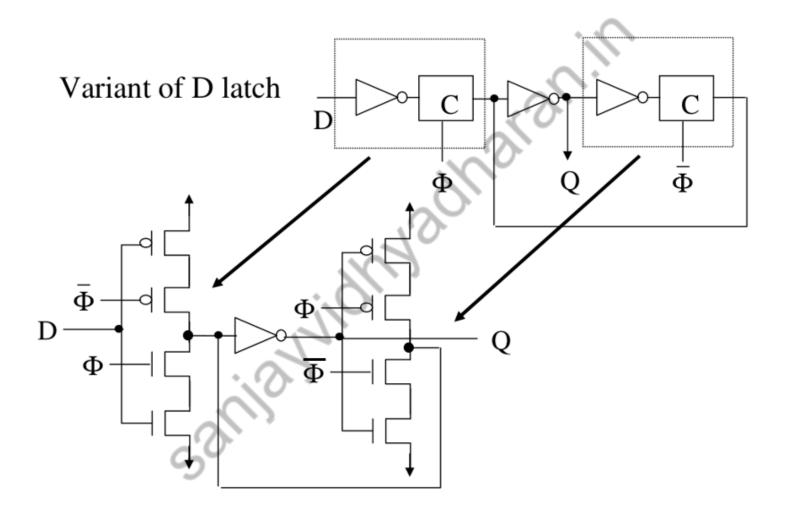

Static D latch

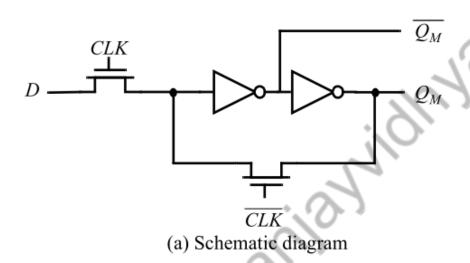

#### **Mux Based Latch**

#### **Mux Based Latch**

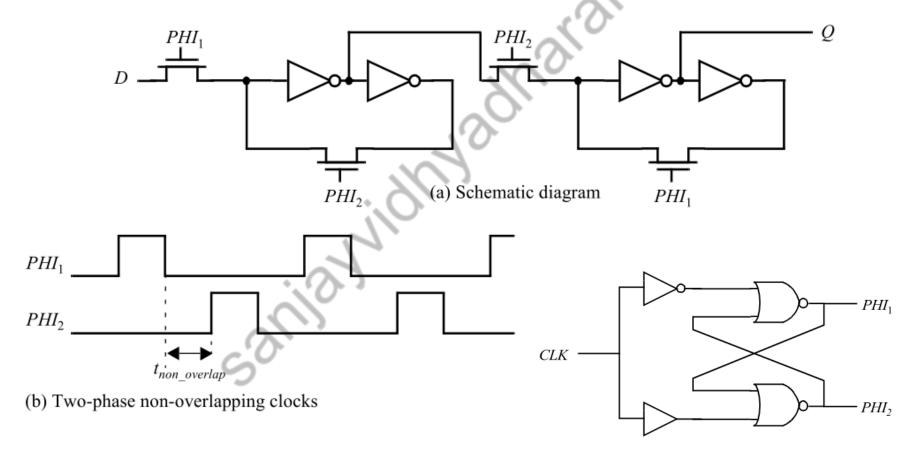

Multiplexer-based NMOS latch using NMOS-only pass transistors.

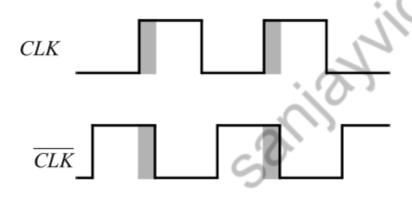

(b) Non-overlapping clocks

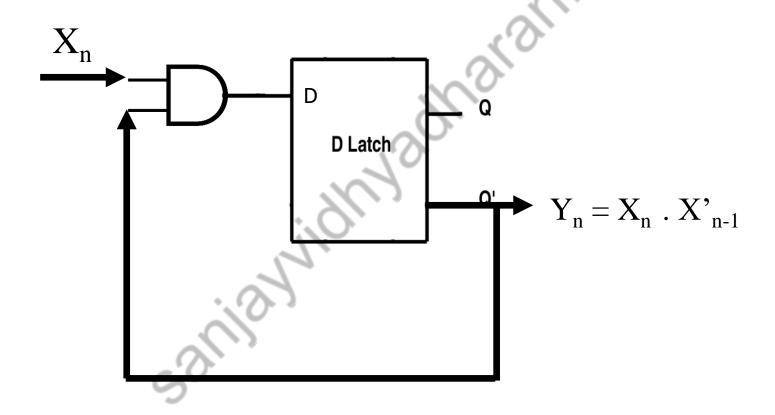

## Race around in Latches

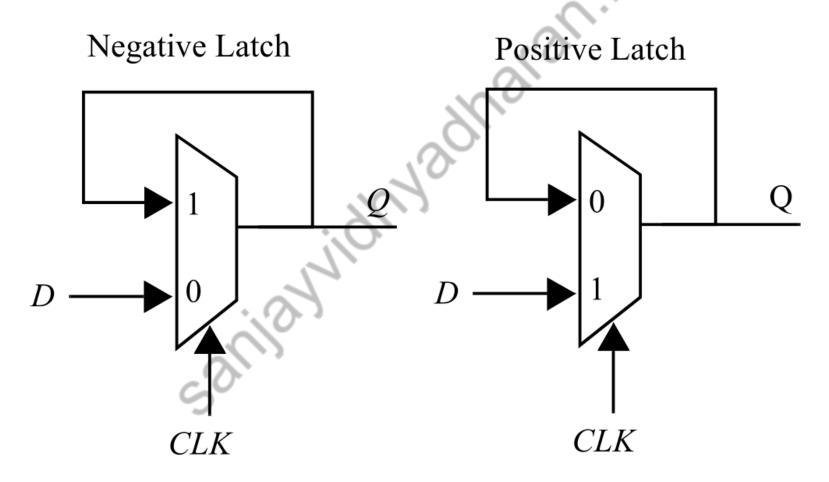

# Latch vs. Flip-flop

Latch – Responds to change in level of clock pulse

The key to the proper operation of a flip-flop is to trigger it only during signal transition.

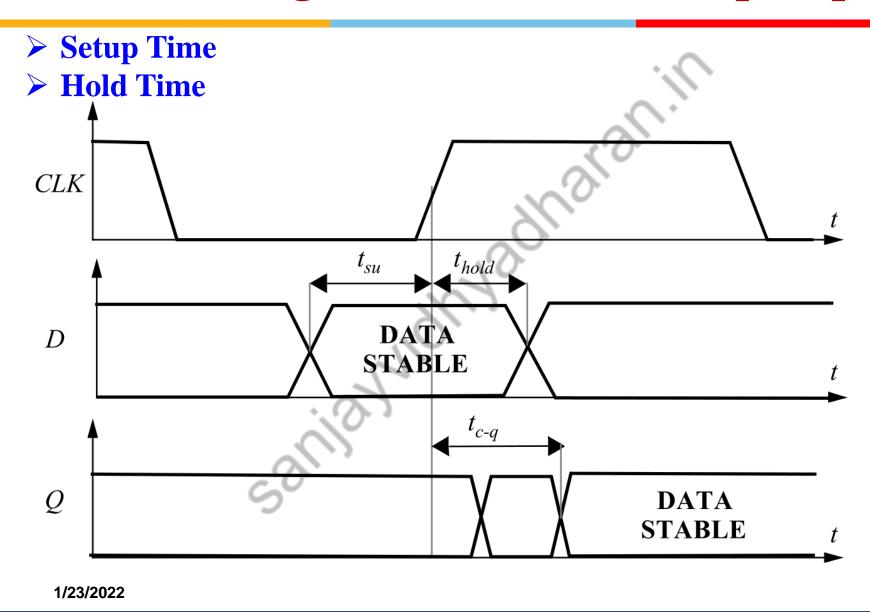

# Timing Constraints of a Flip-flop

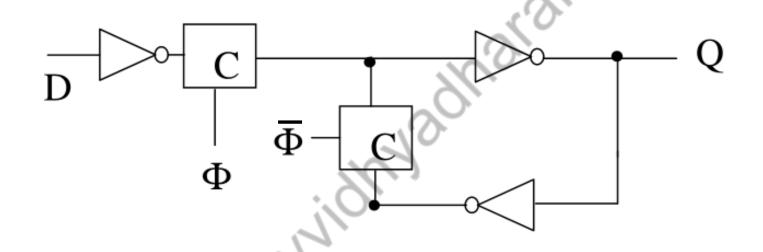

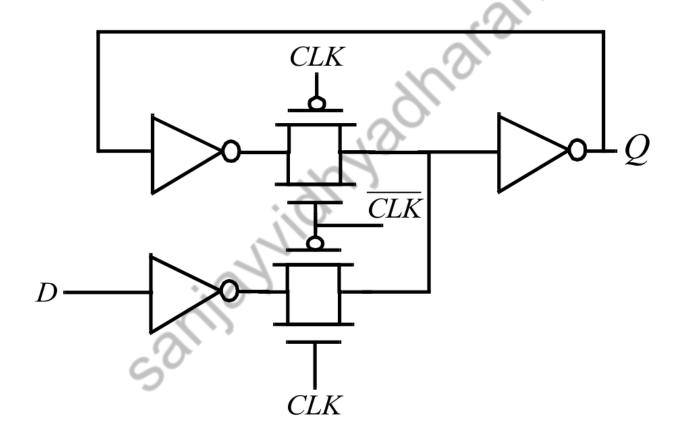

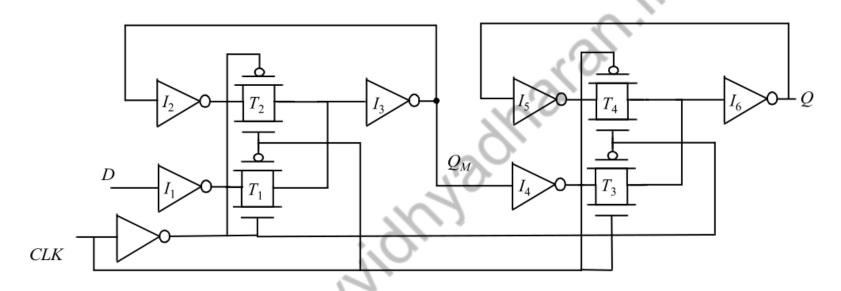

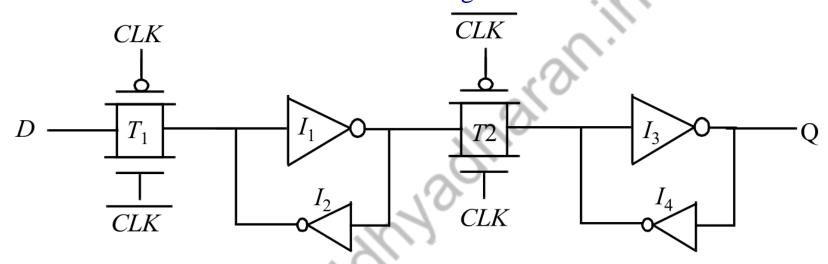

Master-slave positive edge-triggered register using multiplexers.

The set-up time is equal to  $3*t_{pd\_inv} + t_{pd\_tx}$

Hold time is Nil

Propagation delay =

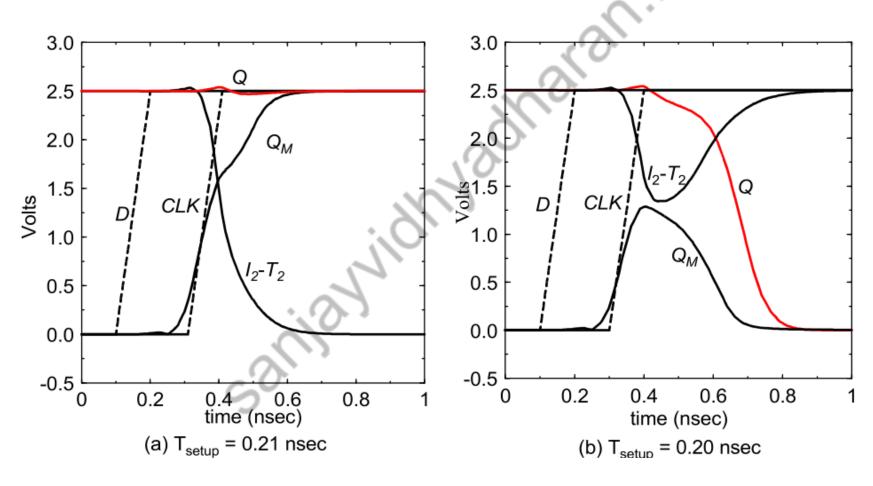

#### Set-up time simulation

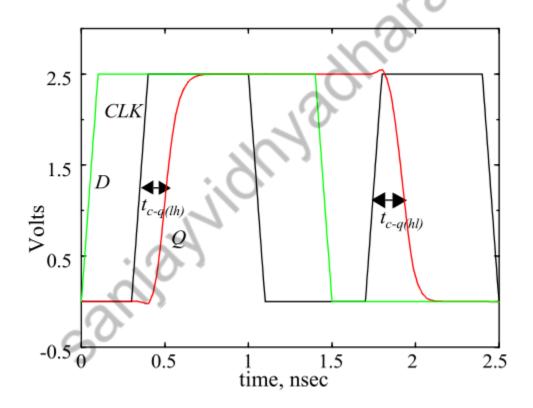

#### Simulation of propagation delay

Reduced load clock load static master-slave register.

The penalty for the reduced clock load is increased design complexity. The transmission gate  $(T_1)$  and its source driver must overpower the feedback inverter  $(I_2)$  to switch the state of the cross-coupled inverter.

The transistors of inverter  $I_2$  should be made weaker. This can be accomplished by making their channel-lengths larger than minimum.

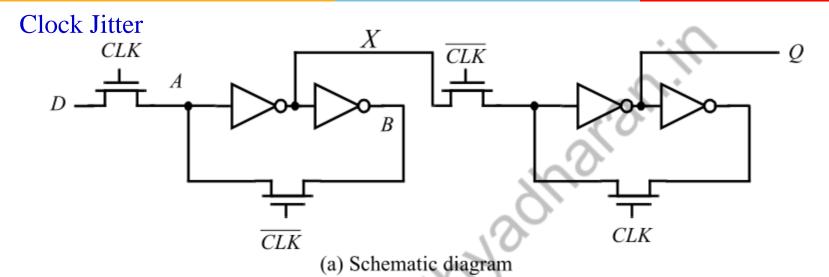

When the clock goes high, the slave stage should stop sampling the master stage output and go into a hold mode. However, since CLK and CLK are both high for a short period of time (the overlap period), both sampling pass transistors conduct and there is a direct path from the D input to the Q output. As a result, data at the output can change on the rising edge of the clock, which is undesired for a negative edge- triggered register.

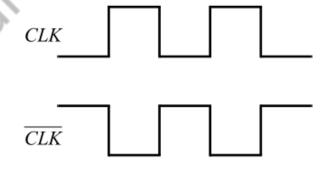

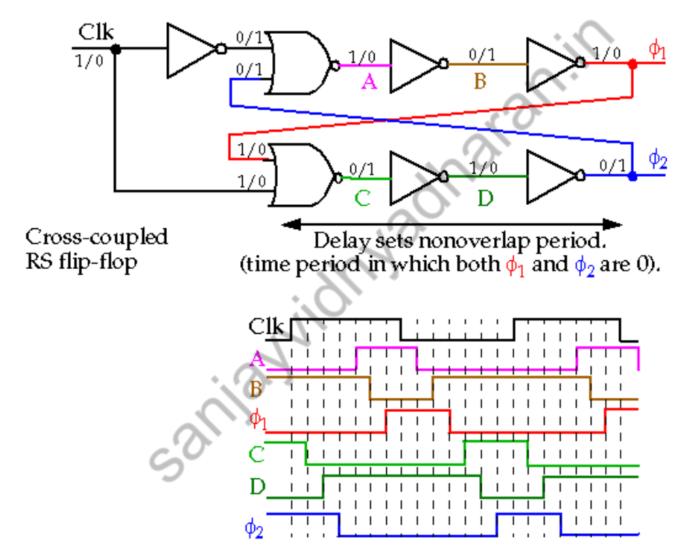

#### Two-phase non-overlapping clocks

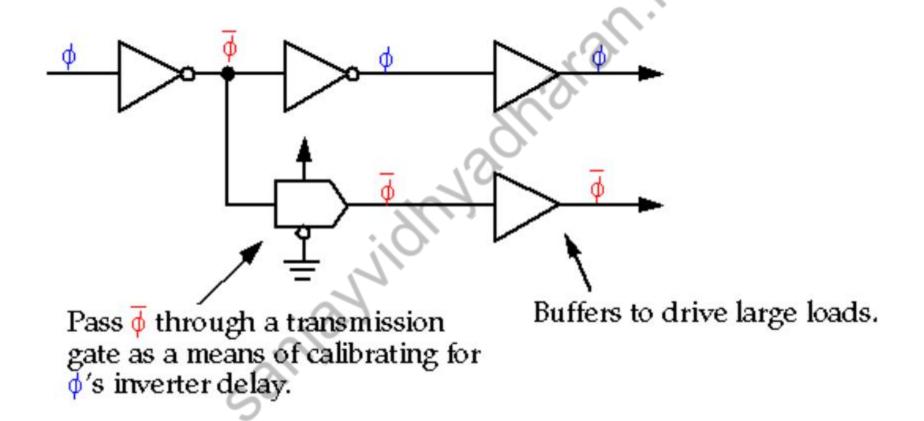

# Single Phase Global Clock Generation

## Non-overlapping Clock Generation

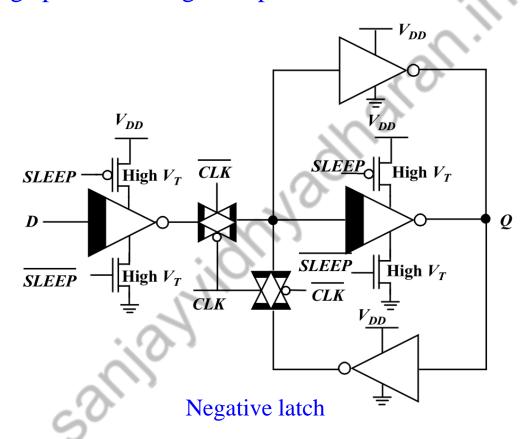

Solving the leakage problem using multiple-threshold CMOS.

- > During normal mode of operation, the sleep devices are tuned on.

- ➤ The shaded inverters and transmission gates are implemented in low-threshold devices.

Thank you