# VLSI Design / Advanced VLSI Design: 2021-22 Lecture 1 **Introduction to VLSI Design** By Dr. Sanjay Vidhyadharan

ELECTRICAL

ELECTRONICS

COMMUNICATION

# **VLSI Design**

Integrated circuits are also categorized according to the number of transistors or other active circuit devices they contain.

- ➤ An IC is said to use small-scale integration (SSI) if it contains fewer than 10 transistors.

- An IC that contains from 10 to 100 transistors is said to use medium-scale integration.

- A large-scale integration (LSI) IC contains from 100 to 1,000 transistors

- And one that uses Very-Large-Scale Integration (VLSI) contains more than 1,000 transistors.

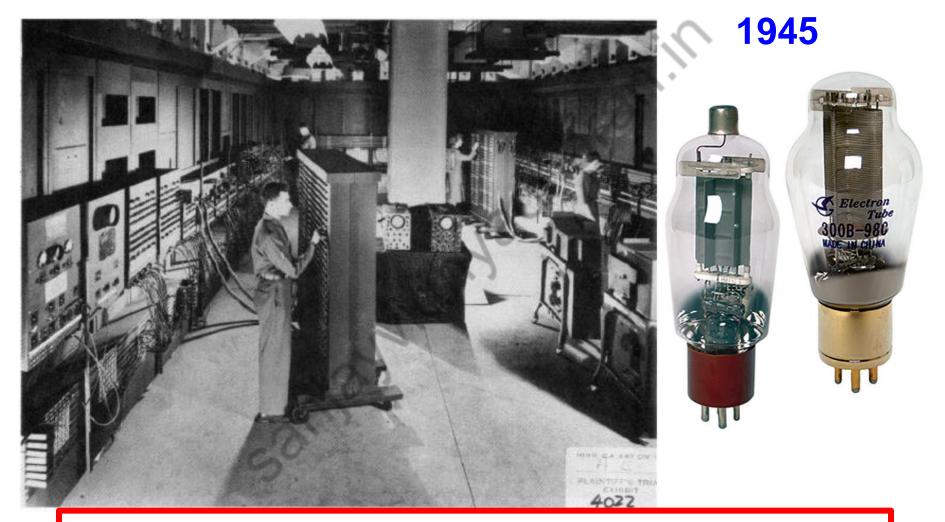

## **ENAIC - The First Electronic Computer**

## 17,468 vacuum tubes and consumed 160 kW

ELECTRICAL

**ELECTRONICS**

COMMUNICATION

# **Evolution of Digital Technology**

- Resistor Transistor Logic

- Diode Transistor Logic

- > Transistor Transistor Logic

- Emitter-coupled Logic

- > CMOS :

- > 1974 Intel 4004 which had 2000 Transistors Channel Length of 10 μm.

- 2021 AMD 7 nm has billions of Transistors Channel Length of 7 nm.

- : 1961

- : 1962

: 1963 Discrete IC

First Microprocessor 360

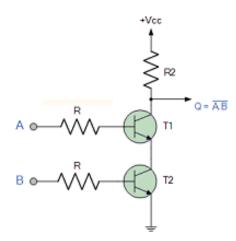

# **RTL Logic**

#### Advantages

The primary advantage of RTL technology was that it involved a minimum number of transistors, which was an important consideration before integrated circuit technology

#### Disadvantages

- The obvious disadvantage of RTL is its high current dissipation when the transistor conducts to overdrive the output biasing resistor.

- > Passive Pull up.

- Limited Fanout

- ➢ No Rail-to-Rail Output

#### 1/15/2022 RTL NOR gate

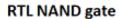

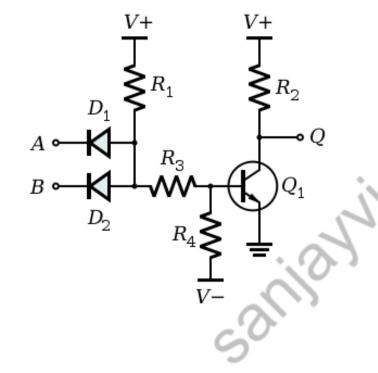

# **DTL Logic**

#### Advantages

Diodes perform the logical function

#### Disadvantages

- The obvious disadvantage of DTL is its high current dissipation when the transistor conducts to overdrive the output biasing resistor.

- > Passive Pull up.

- Limited Fanout

- ➢ No Rail-to-Rail Output

1/15/2022

COMMUNICATION

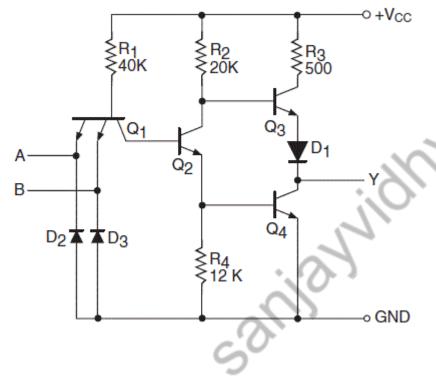

# **TTL Logic**

#### Advantages

- Multi-Emitter perform the logical function

- Active Pull-up and Active Pull down

#### Disadvantages

- The obvious disadvantage of TTL is its high current dissipation

- ➢ No Rail-to-Rail Output

#### 1/15/2022

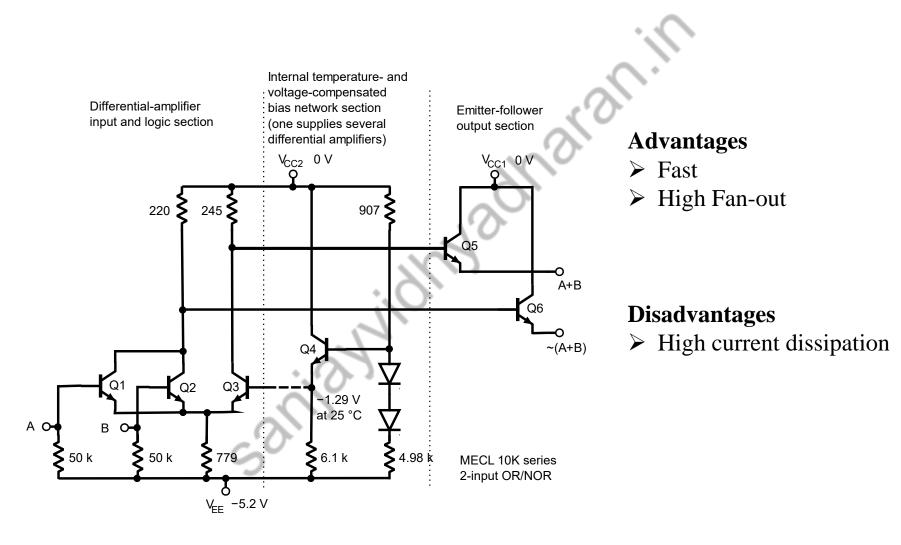

# **ECL Logic**

1/15/2022

#### COMMUNICATION

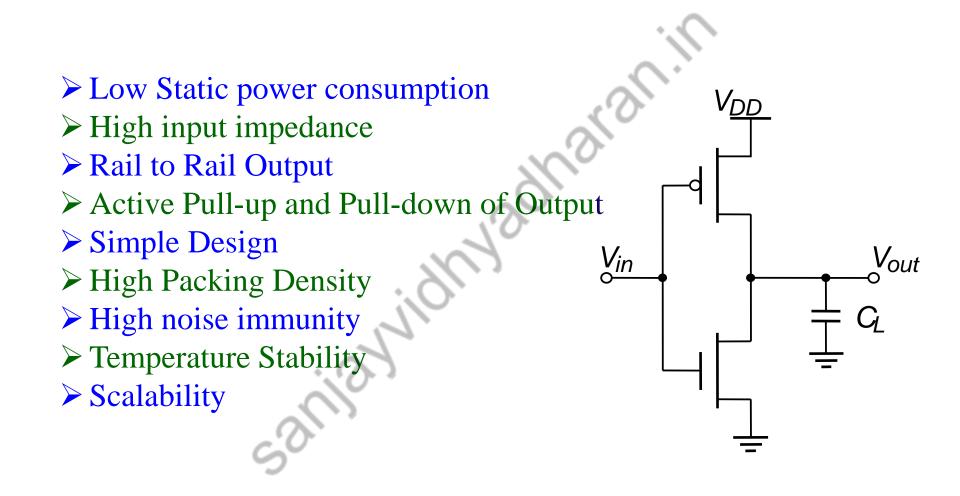

## **Advantages of CMOS Technology**

1/15/2022

## Pentium

1993 : Technology : 0.8 μm (16.7 mm by 17.6 mm) 60–66 MHz

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

## Latest CPUs and GPUs

#### Latest Trends :- Intel : 14 nm AMD : 7nm

**ELECTRICAL**

ELECTRONICS COMMUNICATION

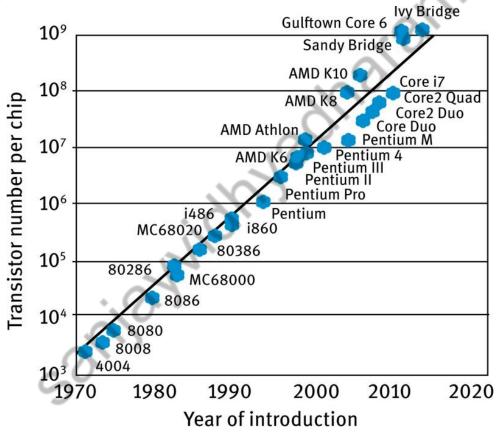

## **Moore's Law**

In 1965, Gordon E. Moore—co-founder of Intel (NASDAQ: INTC)—postulated that the number of **transistors** that can be packed into a given **unit of space will double about every two years.**

Million-transistor/chip barrier crossed in the late 1980s

ELECTRICAL

**ELECTRONICS**

COMMUNICATION

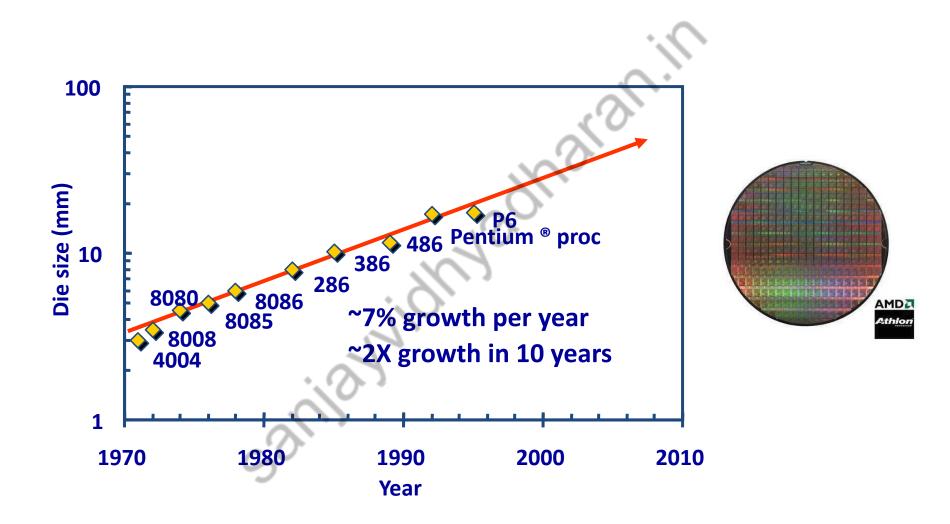

# **Die Size Growth**

COMMUNICATION

**ELECTRICAL**

**ELECTRONICS**

13

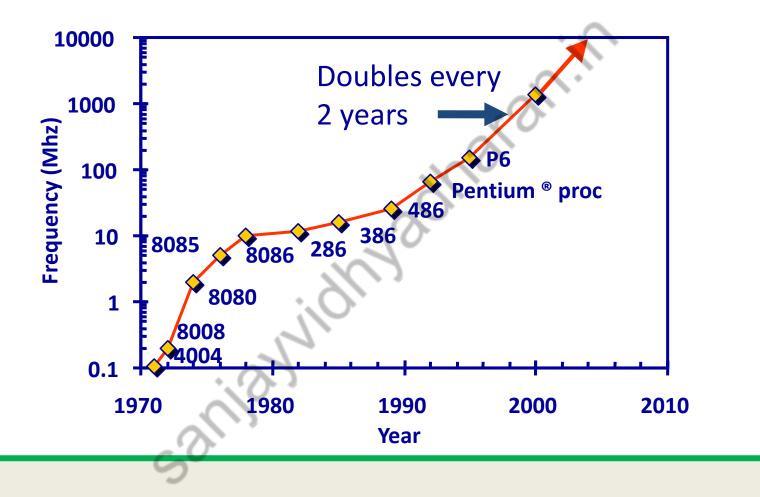

# Frequency

**Microprocessors frequency doubles every 2 years**

ELECTRICAL

ELECTRONICS

COMMUNICATION

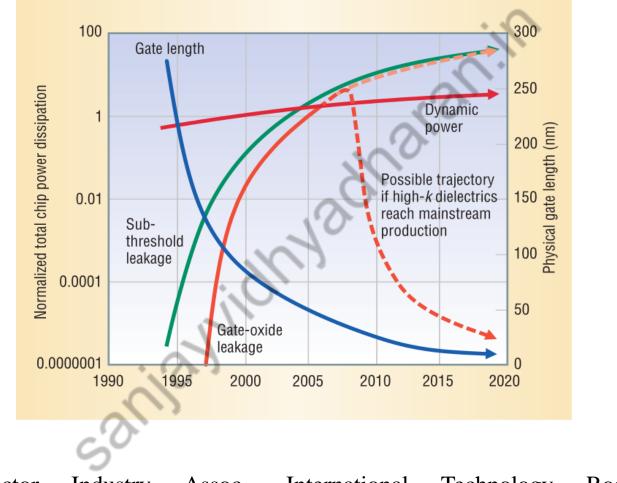

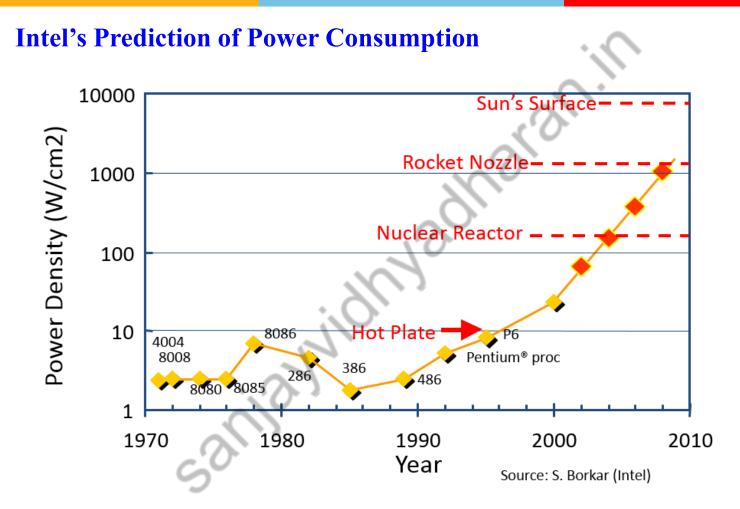

## **ITRS Prediction of Power Consumption**

Semiconductor Industry Assoc., International Technology Roadmap for Semiconductors, 2002 Update; http://public.itrs.net.

1/15/2022

## **Limitations of Static CMOS**

Online Available: http://computerscience.chemeketa.edu/cs160Reader/Parallel Processing/ MooresLaw.html

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

16

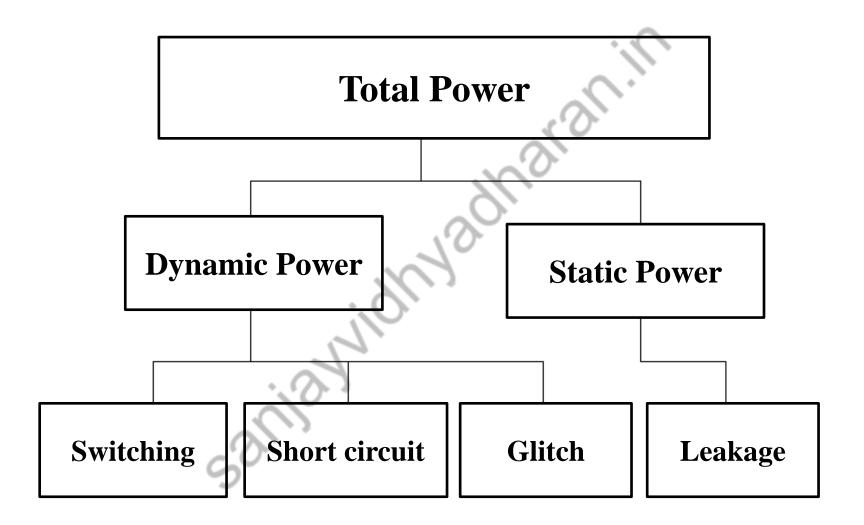

## **Power Dissipation in CMOS Circuits**

COMMUNICATION

**ELECTRONICS**

ELECTRICAL

ELECTRICAL ELECTRONICS COMMUNICATION

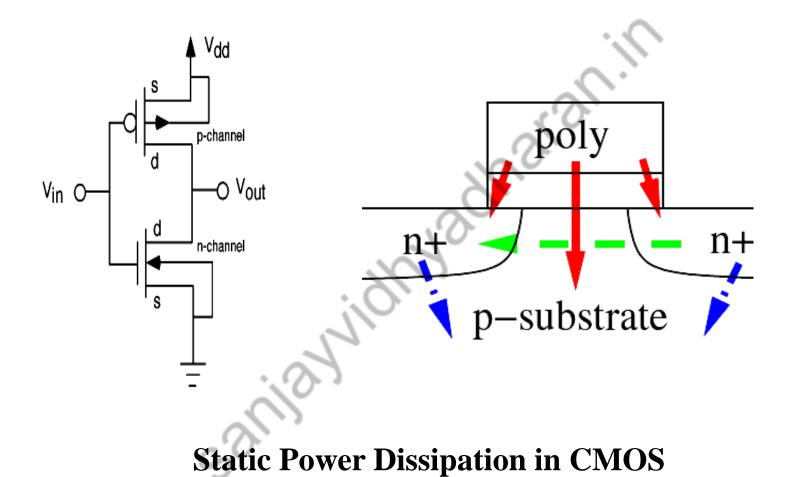

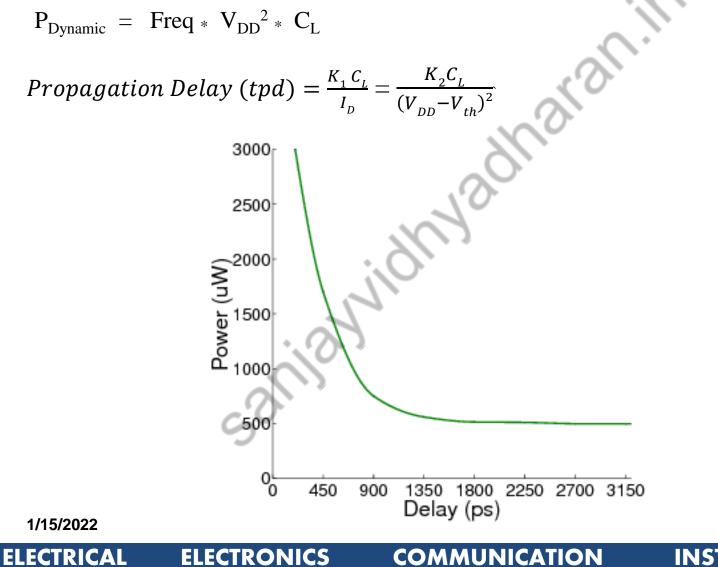

# Causes for High Static Power Consumption Effect of Decreasing V<sub>DD</sub> on Delay Propagation Delay (tpd) = $\frac{K_1 C_L}{I_D} = \frac{K_2 C_L}{(V_{DD} - V_{th})^2}$ Effect of Decreasing V<sub>th</sub> on Power

- Intel estimated leakage power consumption at more than 50W for a 100nm technology node.

- Leakage depends strongly on a Threshold voltage  $(V_{th})$  of the transistor

**INSTRUMENTATION**

#### ELECTRICAL ELECTRONICS COMMUNICATION

ELECTRONICS CO

**ELECTRICAL**

COMMUNICATION

### > Reducing Static Loss

- Device Level Techniques Tunnel Field Effect Transistors CNFETs

- Circuit Level Techniques when using CMOS

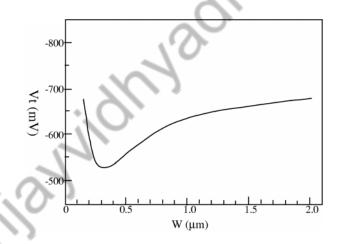

Fig. 12 Variation of threshold voltage with gate width in the case of trench isolated buried channel P-MOSFET showing the anomalous behavior [27].

[3] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," Proceedings of the IEEE, vol. 91, no. 2, pp. 305–327, Feb. 2003.

ELECTRICAL ELECTRONICS

IICS COMMUNICATION

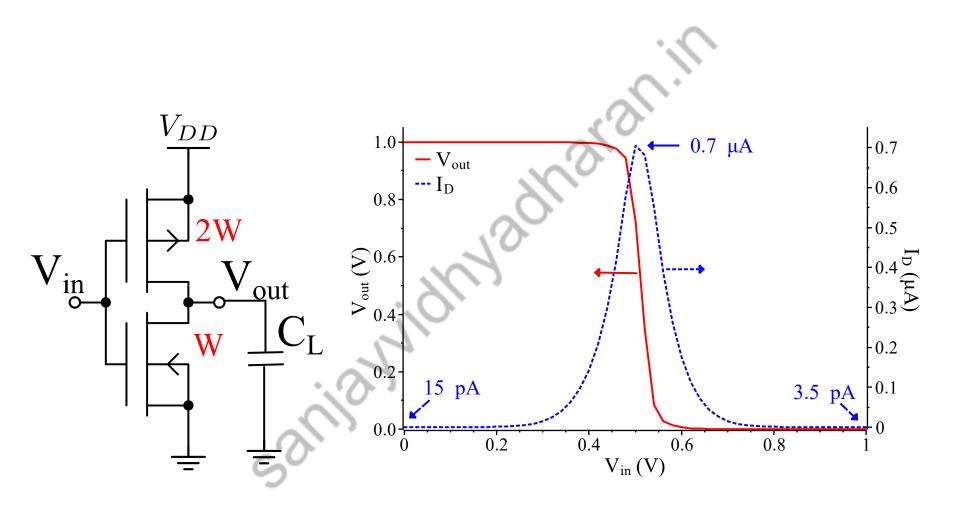

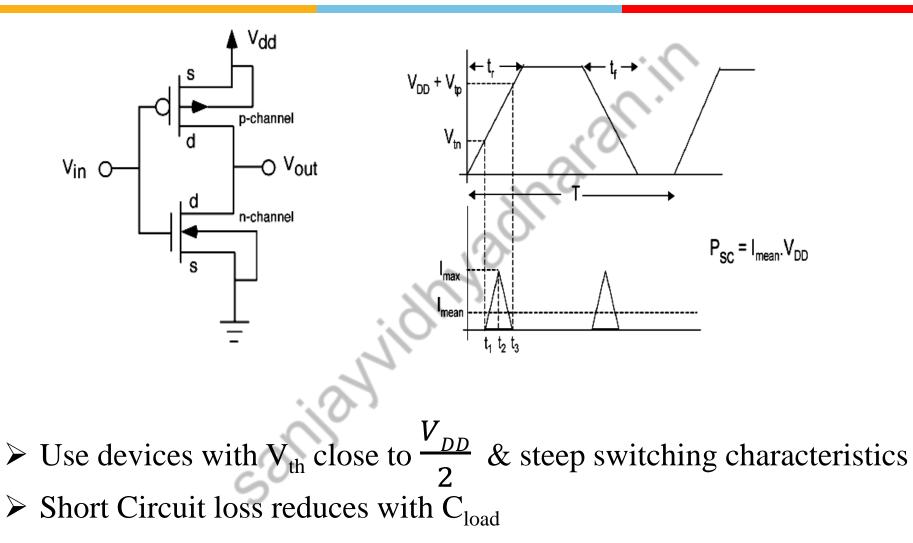

## **Short Circuit Loss**

#### ELECTRONICS COMMUNICATION

ELECTRICAL

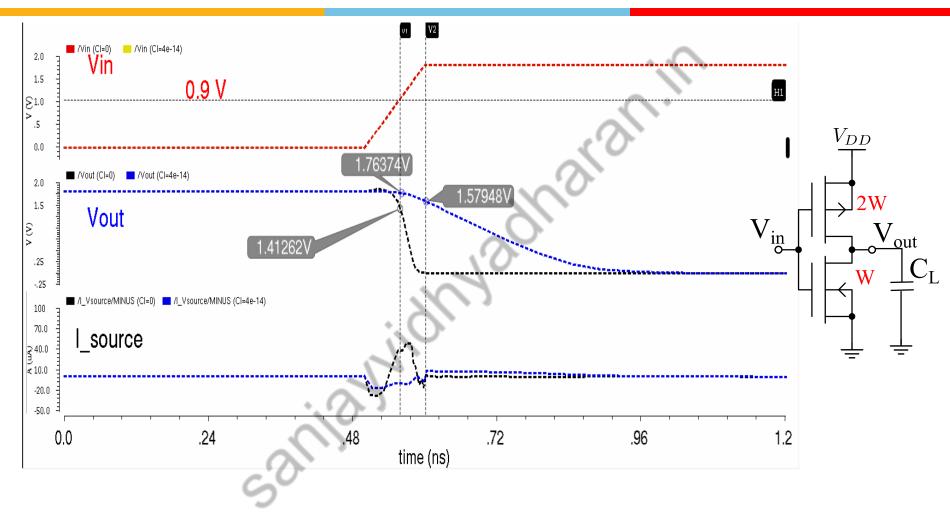

## **Short Circuit Loss**

> Short Circuit loss reduces with  $C_{load}$

**ELECTRICAL**

**ELECTRONICS**

#### COMMUNICATION

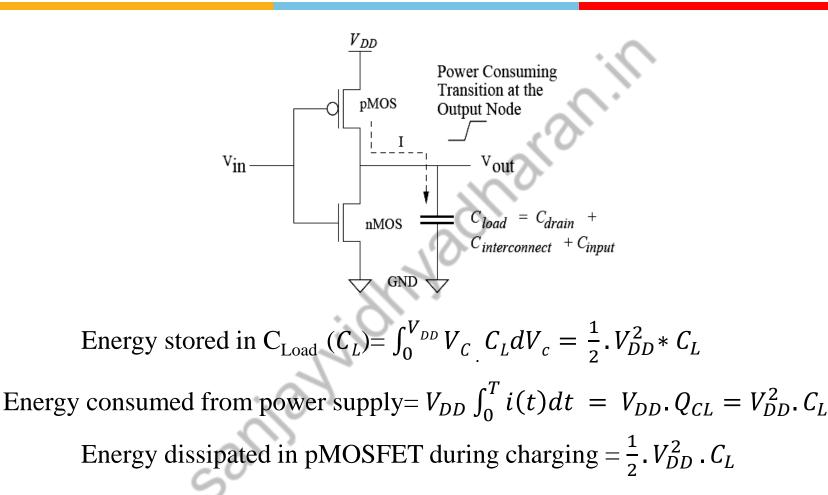

## **Switching Loss**

Energy dissipated in nMOSFET during discharging =  $\frac{1}{2}$ .  $V_{DD}^2$ .  $C_L$

Power Consumption = Frquency.  $V_{DD}^2$ .  $C_L$

ELECTRICAL

ELECTRONICS

COMMUNICATION

## **High Dynamic Power Consumption**

- $P_{Dynamic} = Freq * V_{DD}^2 * C_L$

- $> V_{DD} \& C_L$  : Reduced by 30 % each generation

- > Frequency : 43 % Increase

- Architectural optimizations

- Consumer requirements

- > Transistors per chip : Increased exponentially

- Advancement in lithography

- Multilayer metallization

- Efficient partitioning and routing techniques

INSTRUMENTATION

ELECTRICAL ELECTRONICS COMMUNICATION

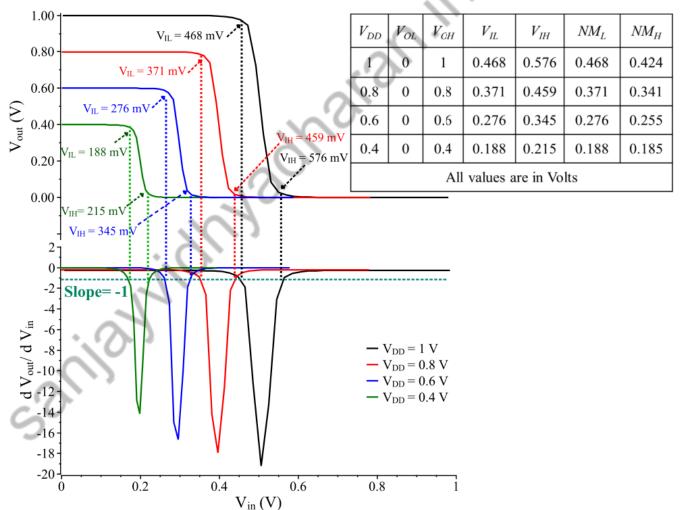

#### **1. Noise Margin**

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

**ELECTRONICS**

**ELECTRICAL**

COMMUNICATION

COMMUNICATION

1/15/2022

**ELECTRICAL**

**ELECTRONICS**

#### 4. Power and Energy Consumption

ELECTRONICS

#### Power consumption of design determine

- How much energy is consumed per operation

- How much heat the circuit dissipates

### > Determine critical design decision

- > Power supply capacity, battery lifetime,

- > Supply line sizing, packaging and cooling

- > Peak power is important for supply line sizing

- Average power dissipation is important for cooling or battery requirements

COMMUNICATION

1/15/2022

ELECTRICAL

#### **5. Power Delay Product**

1/15/2022

COMMUNICATION