# MPI Tutorial-9 8086 Memory Organisation and Interrupts

By Dr. Sanjay Vidhyadharan

- How many address and data lines are required for the following memory chips?

- **256 X 4**

- 1K X 8

- 32K X 16

Sanii

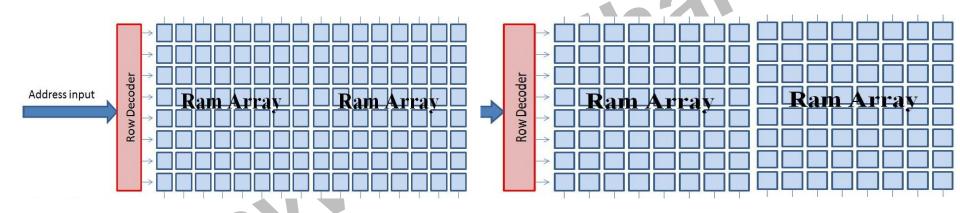

Suppose the memory chips are now of size 16K X 8. How should the memory be organized for the third case.

#### Solution:

Saniayionyadha

#### Solution:

Sani

Now we need to realize a 32KX16 memory using 16KX8 memory chips. Therefore, we would be needing 4 memory chips of 16KX8 arranged as even and odd memory banks. That is 16KX16 can be realized using using 2 16KX8 where one word of 16 bits can be mapped into even and odd bank address space, respectively.

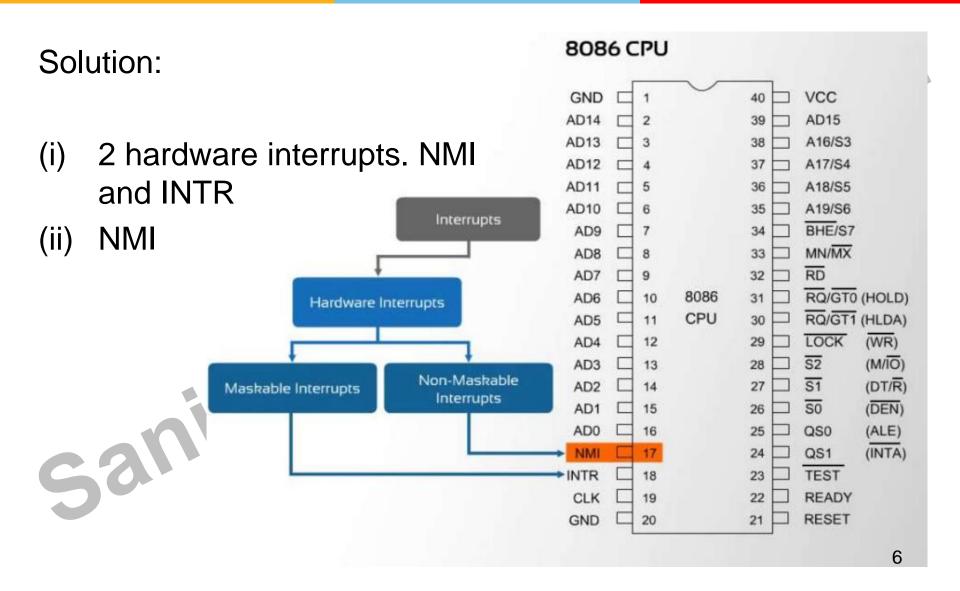

(i) How many hardware interrupts are there in 8086? Stau

a)2

b)3

c)1

d)4

(ii) Which interrupt has the highest priority?

a)TRAP

b)INTR

c) INTO

d)NMI

wnich flag

Solution:

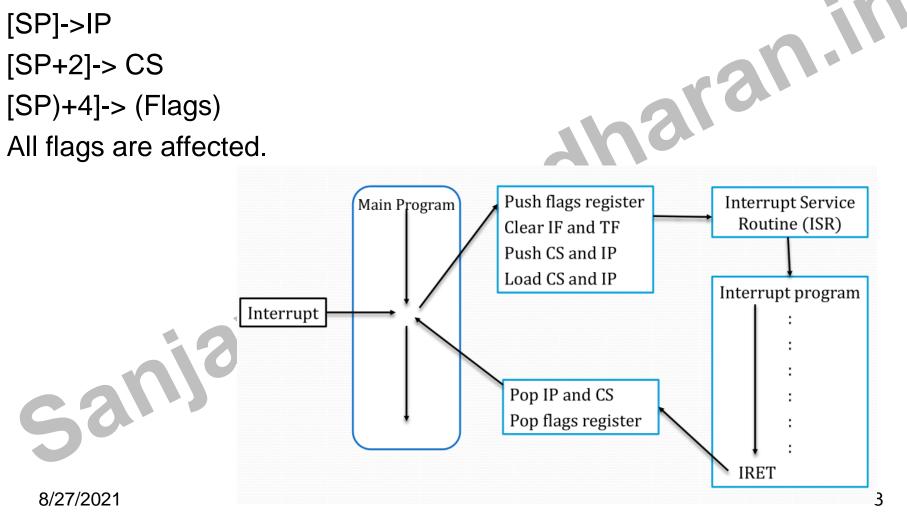

[SP]->IP

[SP+2]-> CS

[SP)+4]-> (Flags)

All flags are affected.

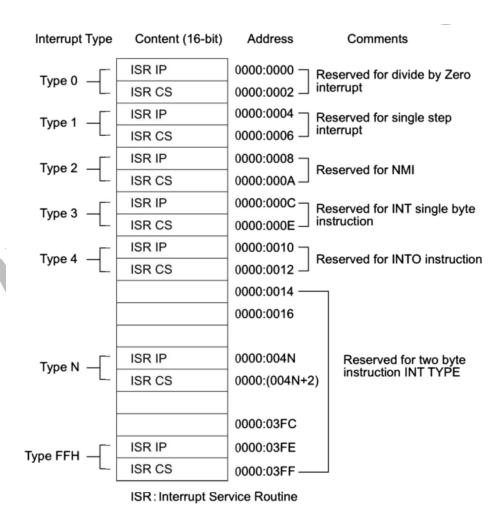

(i) Mention the address at which  $CS_{40}$  and  $IP_{40}$  corresponding to the vector 40 would be stored in memory?

(ii) Mention five dedicated interrupt types and their purpose?

#### Solution

(i) INT 40, for its storage, requires four memory locations

Two for IP40 and two for CS40.

The addresses are calculated as follows:

$4 \times 40 = (160)_{10} = (1010\ 0000)_2 = A0H.$

Thus, IP40 is stored starting at 000A0 H and CS40 is stored starting at 000A2 H.

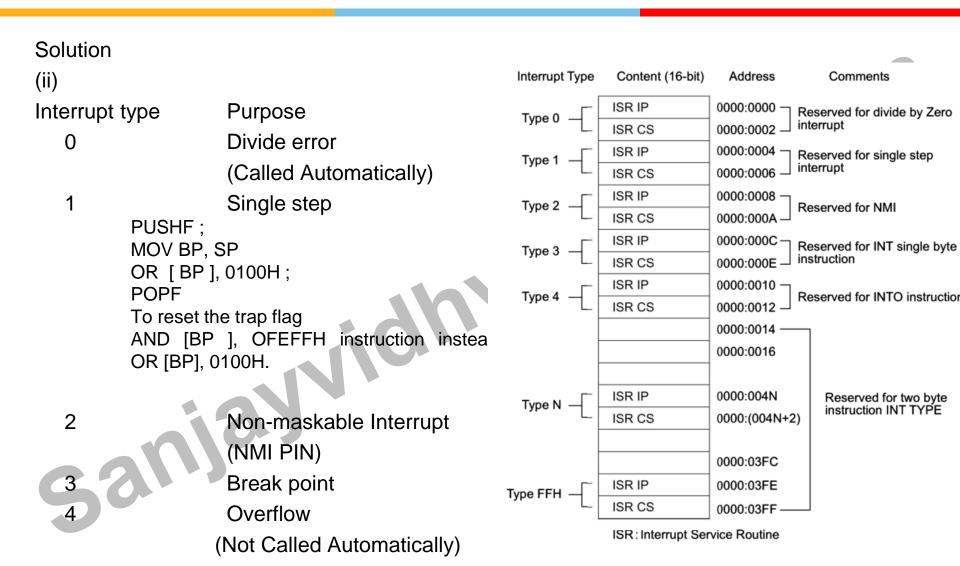

(ii)

| Interrupt type | Purpose                |

|----------------|------------------------|

| 0              | Divide error           |

| 1              | Single step            |

| 2 3            | Non-maskable Interrupt |

|                | Break point            |

| 4              | Overflow               |

8/27/2021

#### Solution:

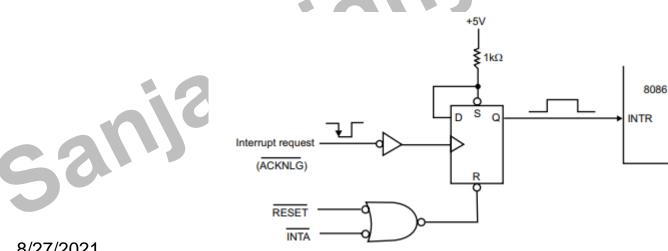

The figure below makes INTR input of 8086 to go into 1 state once the interrupt request comes from some external agency. The falling edge of the peripheral clocks the flip-flop which makes INTR to become 1.

The first  $\overline{INTR}$  pulse then resets Q, making INTR to become 0. This ensures that no second interrupt request is recognized by the system. The reset input sees to it that INTR remains in the 0 state when the system is reset.

8/27/2021

# Thank You -.ank