### Microprocessors and Interfaces: 2021-22 Lecture 4 8086 Architecture

### By Dr. Sanjay Vidhyadharan

**S**3N

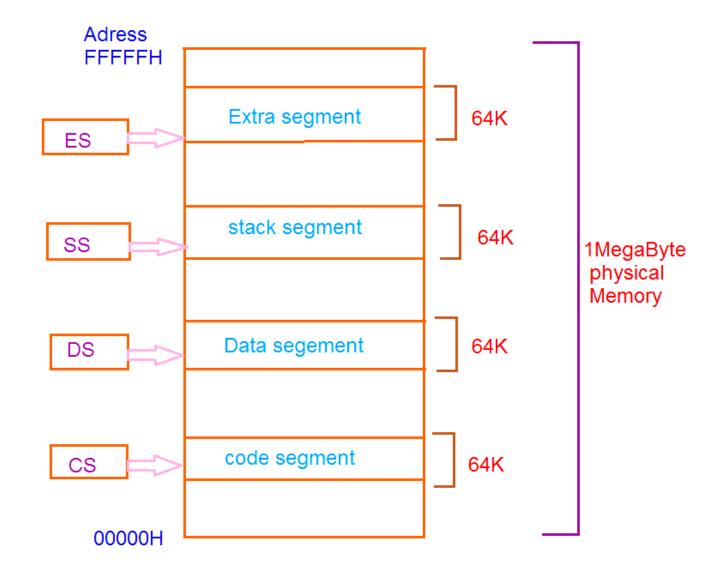

# **Memory Segmentation**

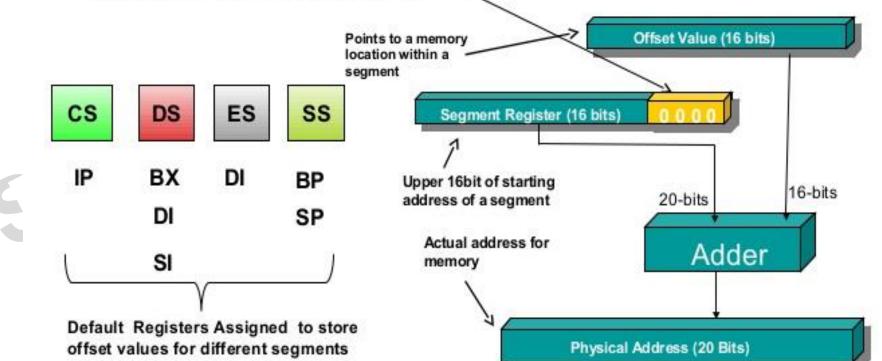

#### **Physical Address Generation in 8086**

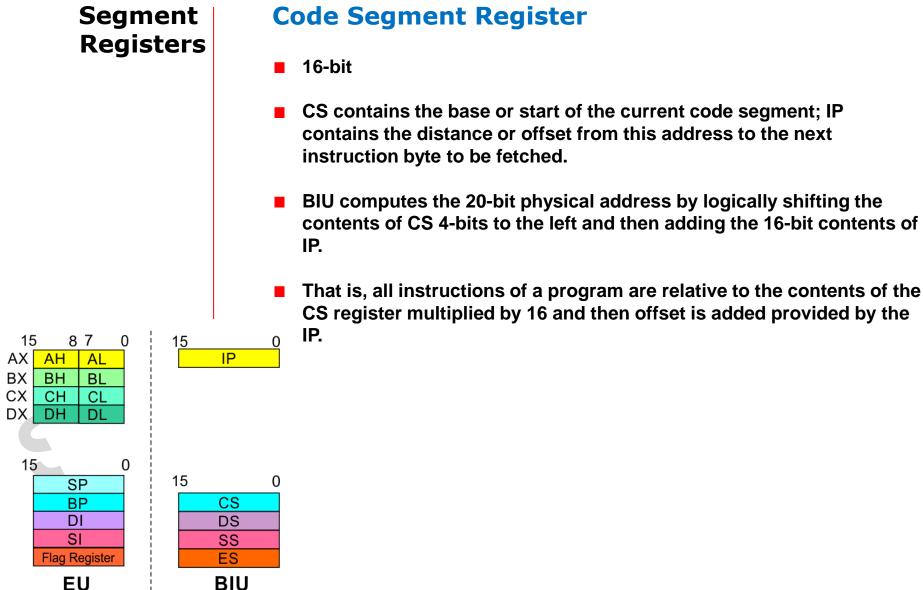

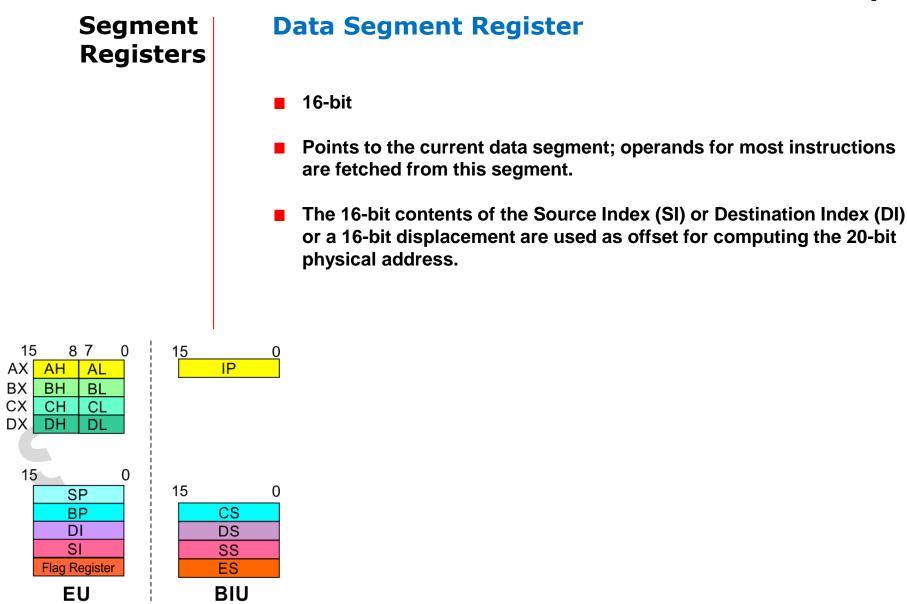

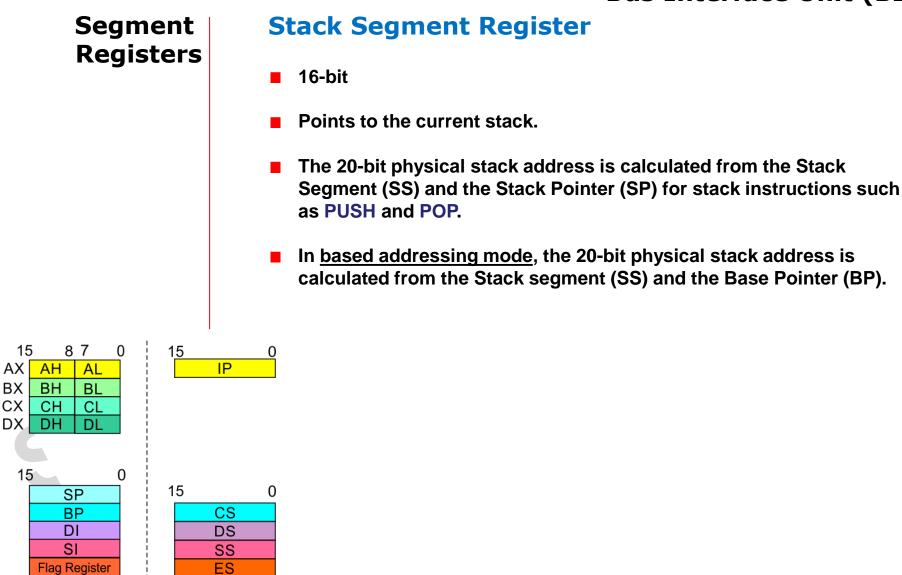

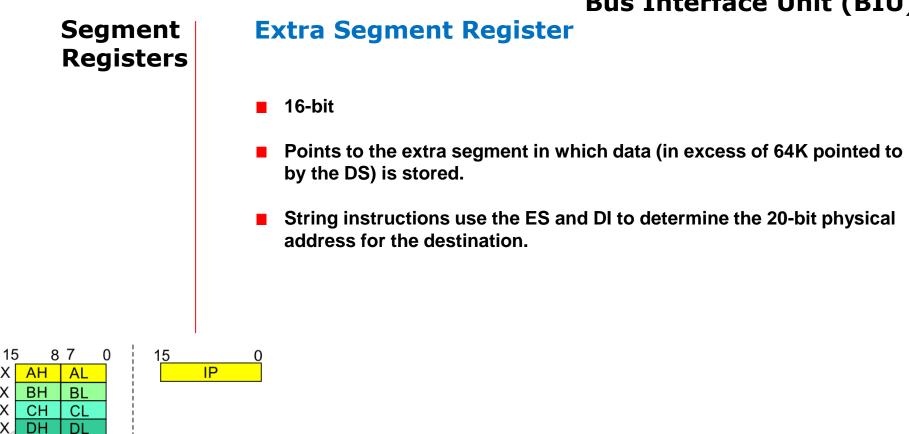

- The 20-bit physical address is generated by adding 16-bit contents of a segment register with an 16-bit offset value (also called Effective Address) which is stored in a corresponding default register (either in IP, BX, SI, DI, BP or SP. Different segments have different default register for offset, for example IP is default offset register for Code Segment)

- BIU always appends 4 zeros automatically to the 16-bit address of a segment register (to make it 20-bit) because it knows the starting address of a segment always ends with 4 zeros

5

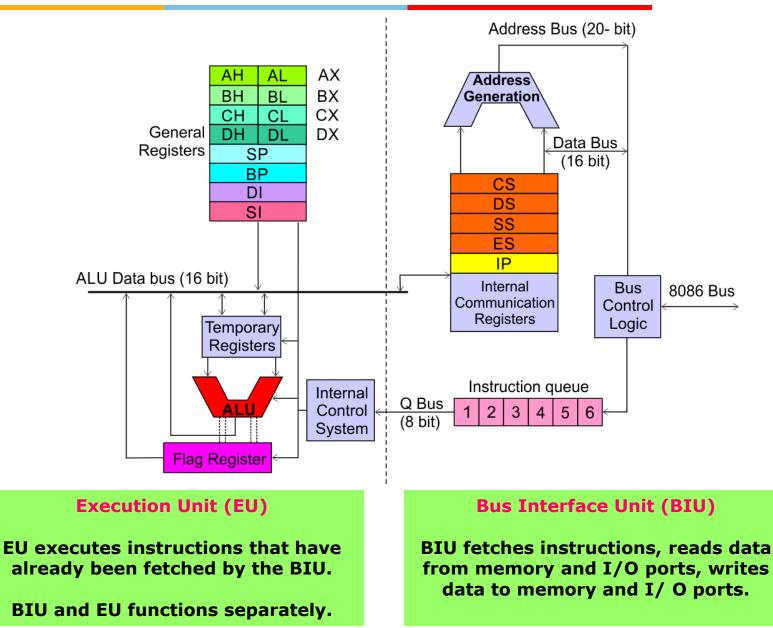

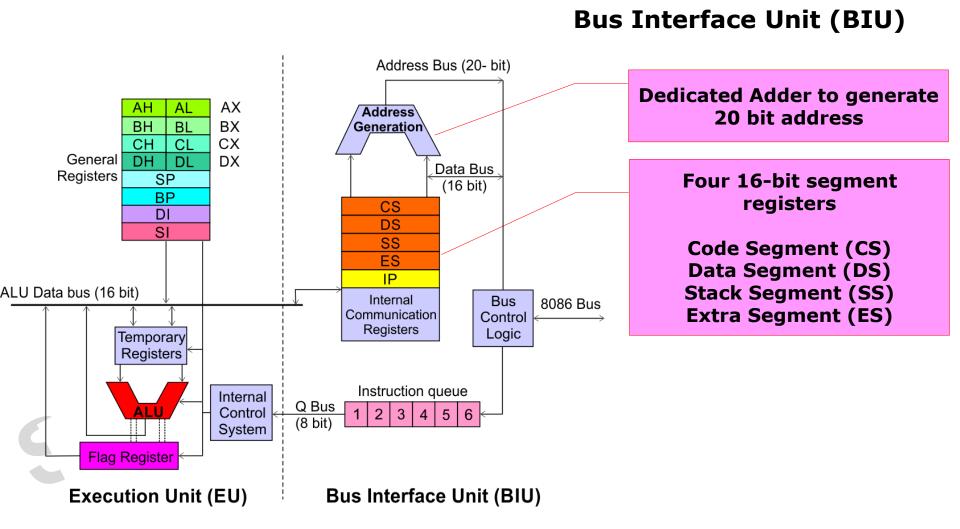

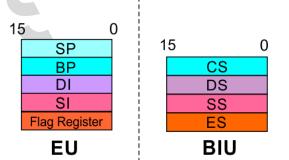

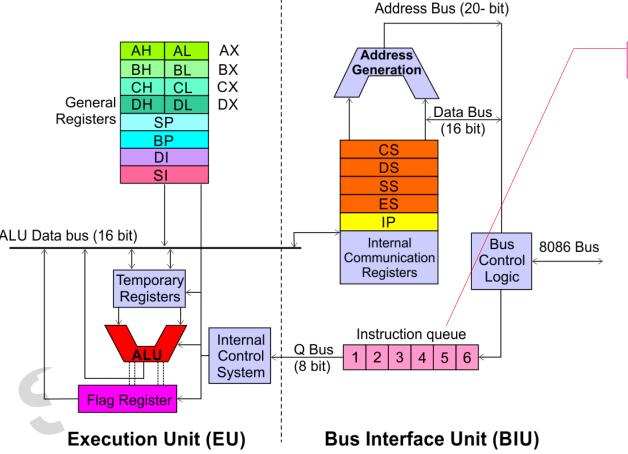

#### **Bus Interface Unit (BIU)**

#### **Bus Interface Unit (BIU)**

#### **Bus Interface Unit (BIU)**

BIU

EU

#### **Bus Interface Unit (BIU)**

AX

ΒX СХ

DX

DL

#### **Bus Interface Unit (BIU)**

SS ES

BIU

**Flag Register**

EU

#### **Bus Interface Unit (BIU)**

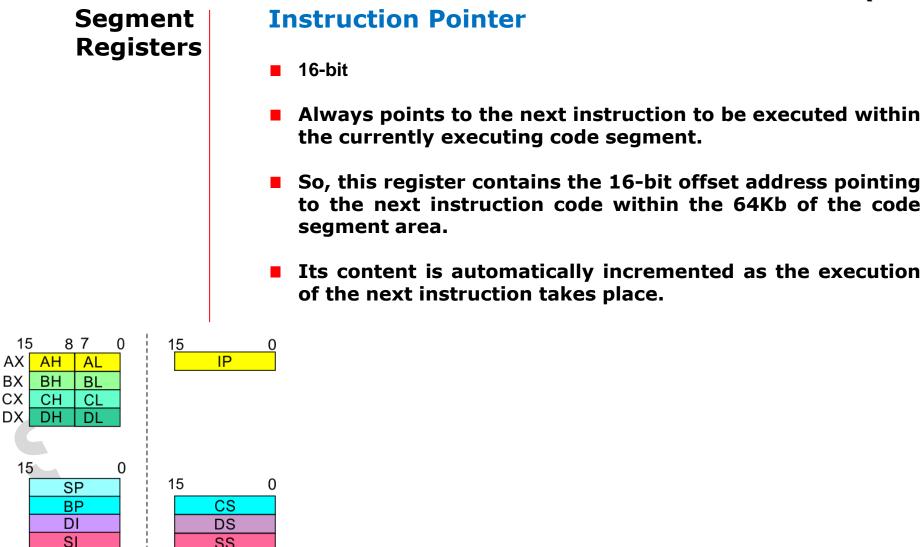

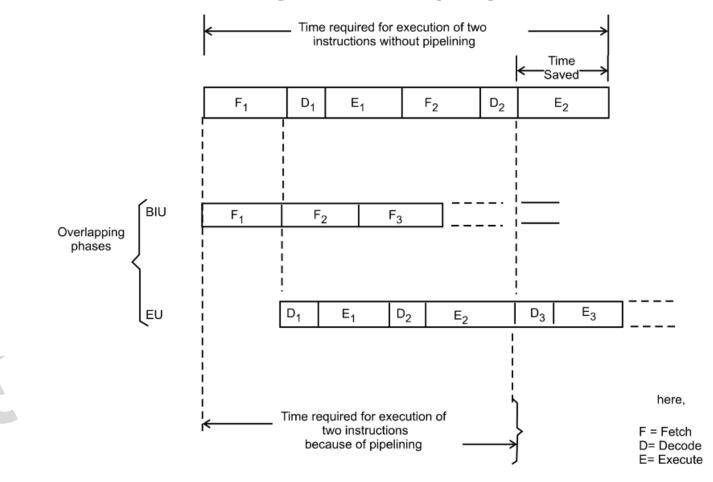

- Instruction queue

- A group of First-In-First-Out (FIFO) in which up to 6 bytes of instruction code are pre fetched from the memory ahead of time.

- This is done in order to speed up the execution by overlapping instruction fetch with execution.

- This mechanism is known as pipelining.

Because of the instruction queue, there is an overlap between the instruction execution and instruction fetching. This feature of fetching the next instruction when the current instruction is being executed, is called *Pipelining*.

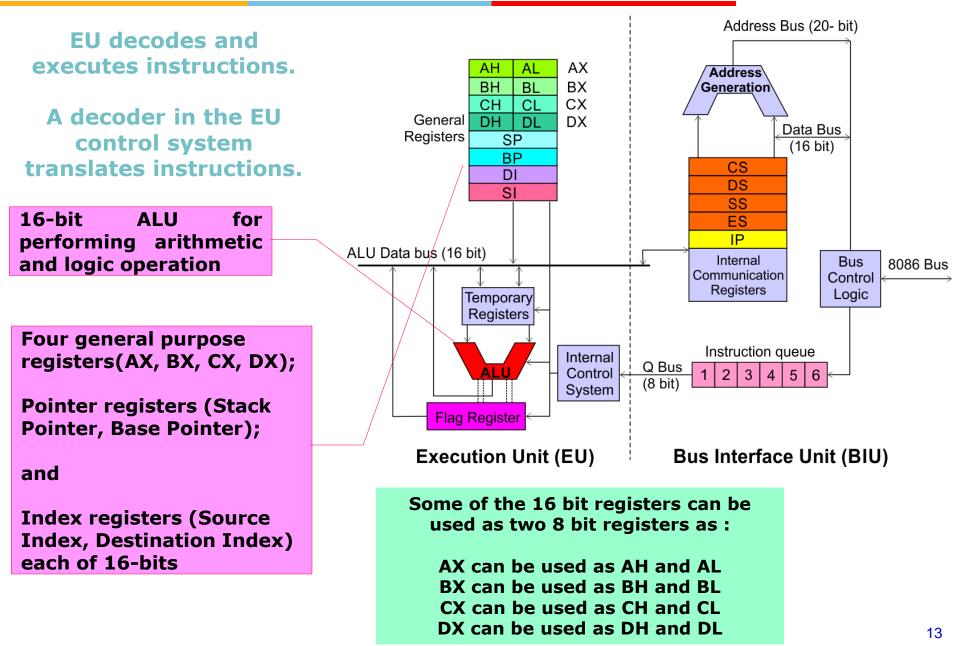

# 8086 Architecture Execution Unit (EU)

#### **Execution Unit (EU)**

EU

BIU

#### **Execution Unit (EU)**

#### **Execution Unit (EU)**

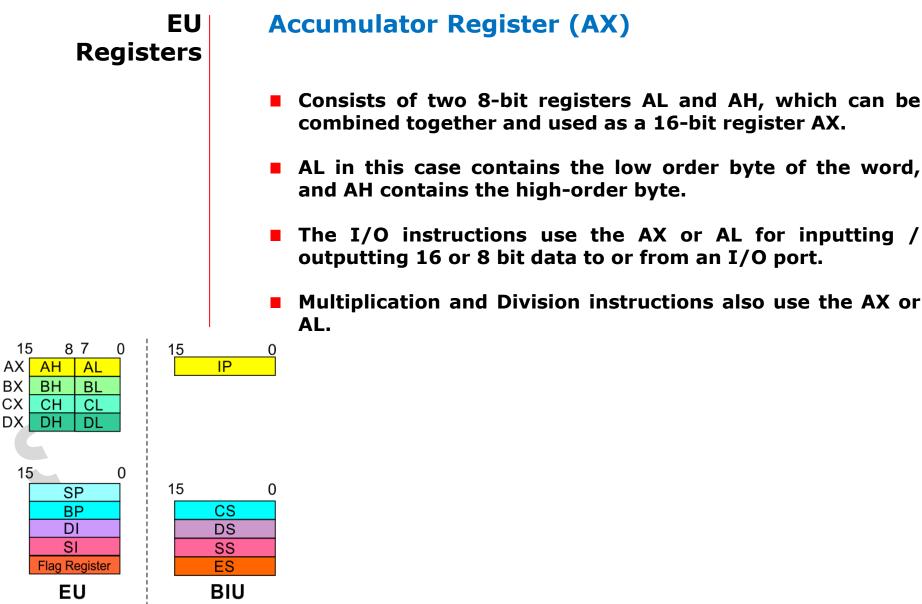

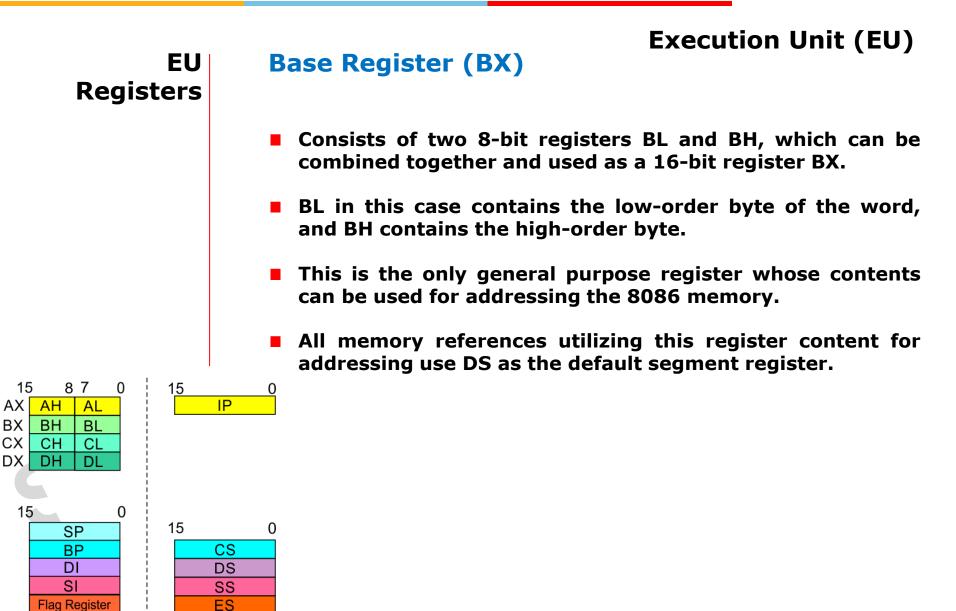

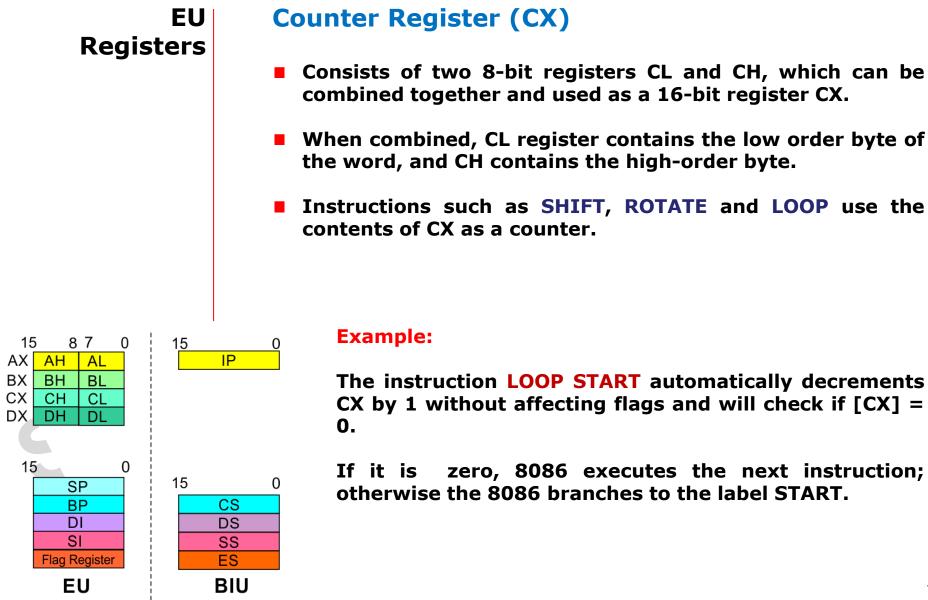

#### EU Registers

#### **Data Register (DX)**

- Consists of two 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX.

- When combined, DL register contains the low order byte of the word, and DH contains the high-order byte.

- Used to hold the high 16-bit result (data) in 16 X 16 multiplication or the high 16-bit dividend (data) before a 32 ÷ 16 division and the 16-bit reminder after division.

#### Data Register (DX)

- Consists of two 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX.

- When combined, DL register contains the low order byte of the word, and DH contains the high-order byte.

- Used to hold the high 16-bit result (data) in 16 X 16 multiplication or the high 16-bit dividend (data) before a 32 ÷ 16 division and the 16-bit reminder after division.

#### **Execution Unit (EU)**

#### **Execution Unit (EU)**

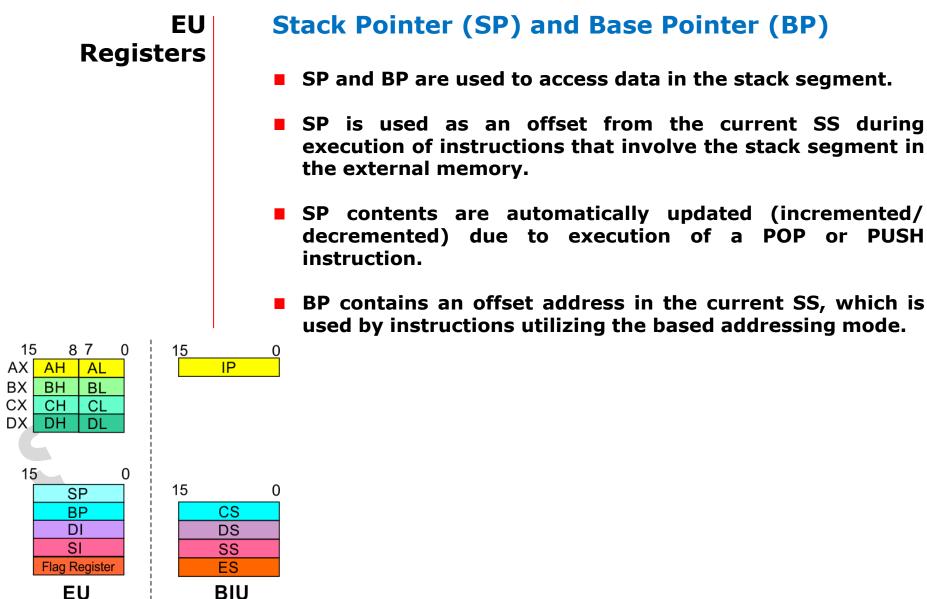

EU Registers

#### Source Index (SI) and Destination Index (DI)

- Used in indexed addressing.

- Instructions that process data strings use the SI and DI registers together with DS and ES respectively in order to distinguish between the source and destination addresses.

### **Execution Unit (EU)**

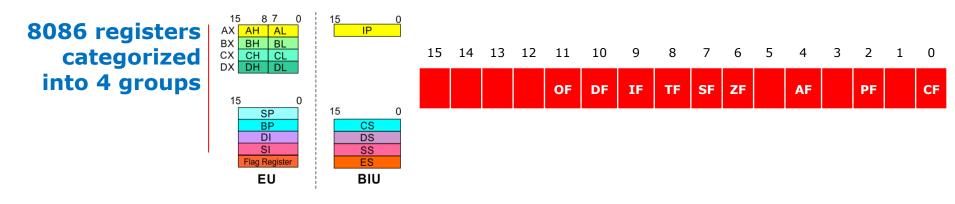

| Auxiliary Carry Flag                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |                             |            |                                                                                                                   |                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------|------------|-------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Flag Register                                                                                                                                                                                                                                                                                                                                         | This is set, if there is a<br>lowest nibble, i.e, bit<br>addition, or borrow f<br>nibble, i.e, bit t<br>subtraction. | carry fr<br>three<br>or the | during     | Carry Flag<br>This flag is set, when th<br>a carry out of MSB in ca<br>addition or a borrow in<br>of subtraction. | case of            |  |

| Sign Flag                                                                                                                                                                                                                                                                                                                                             | Zero Flag                                                                                                            |                             |            | Parity Flag                                                                                                       |                    |  |

| This flag is set, when the result of any computation is negative                                                                                                                                                                                                                                                                                      | This flag is set, if the result of<br>the computation or comparison<br>performed by an instruction is<br>zero        |                             | byte of th | is set to 1, if the lower<br>he result contains even<br>of 1's ; for odd number<br>t to zero.                     |                    |  |

| 15 14 13 12                                                                                                                                                                                                                                                                                                                                           | 11 10 9 8 7                                                                                                          | 6                           | 5 4        | 3 2 1 0                                                                                                           | /                  |  |

|                                                                                                                                                                                                                                                                                                                                                       | OF DF IF TF SF                                                                                                       | ZF                          | AF         | PF CF                                                                                                             |                    |  |

| Over flow Flag<br>This flag is set, if an overflow occurs, i.e, if the result of a signed<br>operation is large enough to accommodate in a destination<br>register. The result is of more than 7-bits in size in case of 8-bit<br>signed operation and more than 15-bits in size in case of 16-bit<br>sign operations, then the overflow will be set. |                                                                                                                      |                             |            |                                                                                                                   | ecution<br>nternal |  |

#### **Direction Flag**

This is used by string manipulation instructions. If this flag bit is '0', the string is processed beginning from the lowest address to the highest address, i.e., auto incrementing mode. Otherwise, the string is processed from the highest address towards the lowest address, i.e., auto incrementing mode.

#### **Interrupt Flag**

Causes the 8086 to recognize external mask interrupts; clearing IF disables these interrupts.

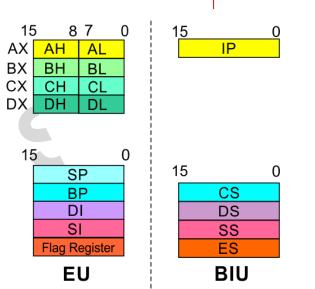

| SI.No. | Туре                       | Register width | Name of register               |

|--------|----------------------------|----------------|--------------------------------|

| 1      | General purpose register   | 16 bit         | AX, BX, CX, DX                 |

|        |                            | 8 bit          | AL, AH, BL, BH, CL, CH, DL, DH |

| 2      | Pointer register           | 16 bit         | SP, BP                         |

| 3      | Index register             | 16 bit         | SI, DI                         |

| 4      | <b>Instruction Pointer</b> | 16 bit         | IP                             |

| 5      | Segment register           | 16 bit         | CS, DS, SS, ES                 |

| 6      | Flag (PSW)                 | 16 bit         | Flag register                  |

#### **Registers and Special Functions**

| Register | Name of the Register | Special Function                                                                                  |

|----------|----------------------|---------------------------------------------------------------------------------------------------|

| AX       | 16-bit Accumulator   | Stores the 16-bit results of arithmetic and logic operations                                      |

| AL       | 8-bit Accumulator    | Stores the 8-bit results of arithmetic and logic operations                                       |

| BX       | Base register        | Used to hold base value in base addressing mode to access memory data                             |

| СХ       | Count Register       | Used to hold the count value in SHIFT, ROTATE and LOOP instructions                               |

| DX       | Data Register        | Used to hold data for multiplication and division operations                                      |

| SP       | Stack Pointer        | Used to hold the offset address of top stack memory                                               |

| BP       | Base Pointer         | Used to hold the base value in base addressing using SS register to access data from stack memory |

| SI       | Source Index         | Used to hold index value of source operand (data) for string instructions                         |

| DI       | Data Index           | Used to hold the index value of destination operand (data) for string operations                  |

### Thankyou

Ę