# **Microprocessors and Interfaces: 2021-22** 31.7 Lecture 32 **ANALOG-TO-DIGITAL (ADC) DIGITAL-TO-ANALOG (DAC) CONVERTERS** By Dr. Sanjay Vidhyadharan

63

# **ADC (Analog-to Digital Converter)**

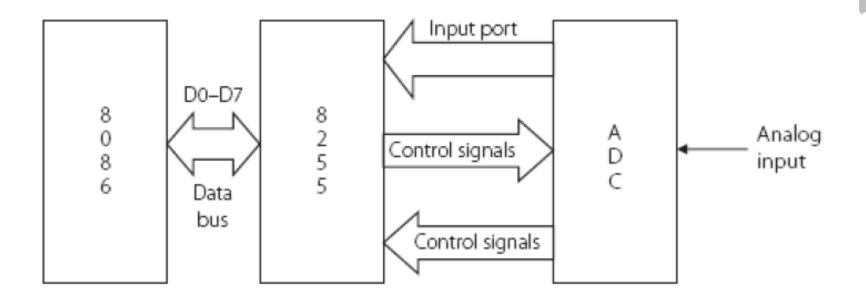

#### **Interface with 8086**

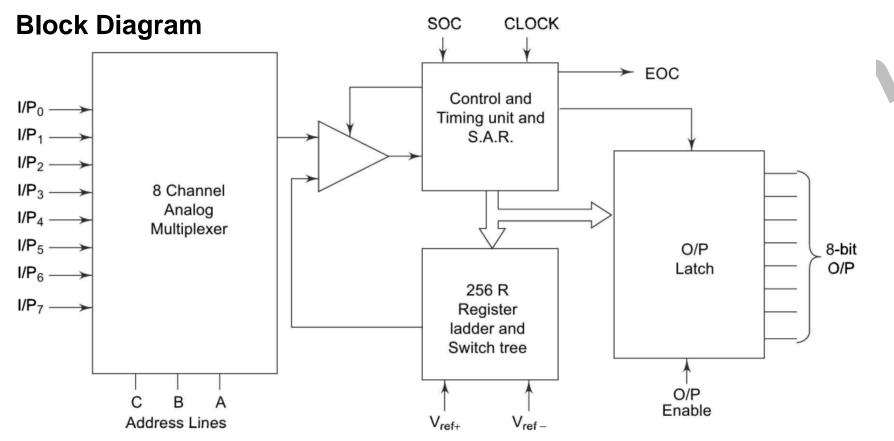

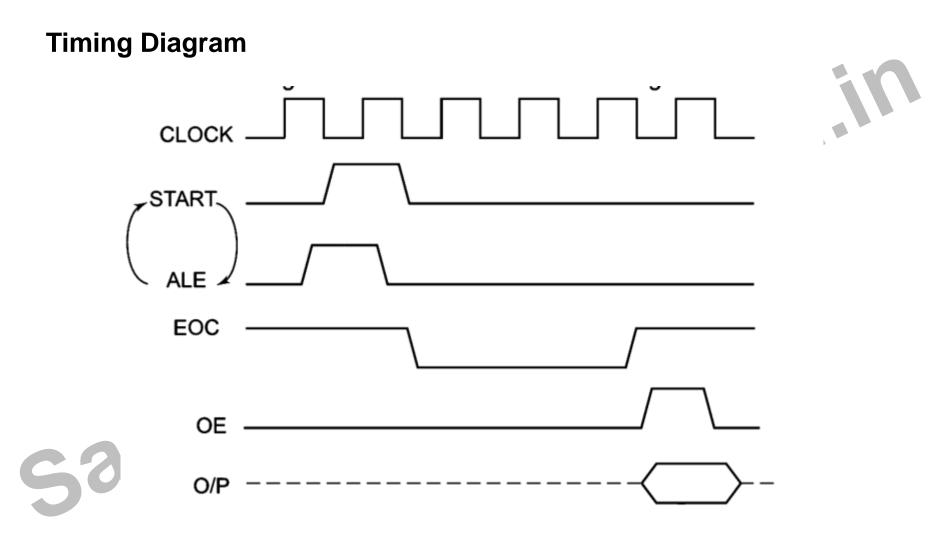

SOC: Start of Conversion EOC : End of Conversion

S311

Low-cost ADC, Power 15 mW, Compatible with a wide range of microprocessors. Power Supply 5 V Moderate speed 100  $\mu$ s

Moderate accuracy Error  $\pm$  LSB

#### Pin Diagram

| $I/P_3 \rightarrow$  | 1  |          | 28 🔫 | -        | I/P2               |                                |     |  |  |  |  |  |      |  |      |                                    |     |

|----------------------|----|----------|------|----------|--------------------|--------------------------------|-----|--|--|--|--|--|------|--|------|------------------------------------|-----|

| $I/P_4 \rightarrow$  | 2  |          | 27 🔫 | -        | I/P1               |                                |     |  |  |  |  |  |      |  |      |                                    |     |

| $I/P_5 \rightarrow$  | 3  |          |      |          |                    |                                |     |  |  |  |  |  | 26 🔫 |  | I/Po | I/P <sub>0</sub> –I/P <sub>7</sub> | Ana |

| $I/P_6 \rightarrow$  | 4  |          | 25 🔫 | <u>.</u> | ADD A              | ADD A, B, C                    | Add |  |  |  |  |  |      |  |      |                                    |     |

| I/P <sub>7</sub> →   | 5  |          | 24 🔫 | -        | ADD B              | O <sub>7</sub> –O <sub>0</sub> | Dig |  |  |  |  |  |      |  |      |                                    |     |

| SOC→                 | 6  |          | 23 🔫 | -        | ADD C              | SOC                            | Sta |  |  |  |  |  |      |  |      |                                    |     |

| EOC→                 | 7  | ADC 0808 | 22 🔫 | _        | ALE                | EOC                            | End |  |  |  |  |  |      |  |      |                                    |     |

| $O_3 \rightarrow$    | 8  | ADC 0809 | 21 🔫 | 5        | O7MSB              | OE                             | Out |  |  |  |  |  |      |  |      |                                    |     |

| OE →                 | 9  |          | 20 🔫 | -        | O <sub>6</sub>     | CLK                            | Clo |  |  |  |  |  |      |  |      |                                    |     |

| CLK ->               | 10 |          | 19 🔫 | -        | O <sub>5</sub>     | V <sub>CC</sub> , GND          | Sup |  |  |  |  |  |      |  |      |                                    |     |

| $V_{cc} \rightarrow$ | 11 |          | 18 🔫 |          | O <sub>4</sub>     | $V_{ref+}$ and $V_{ref-}$      | Ref |  |  |  |  |  |      |  |      |                                    |     |

| $V_{ref^+}$          | 12 |          | 17 🔫 | 5<br>0   | O <sub>0</sub> LSB |                                | and |  |  |  |  |  |      |  |      |                                    |     |

| GND→                 | 13 |          | 16 🔫 | -        | V <sub>ref</sub> - |                                |     |  |  |  |  |  |      |  |      |                                    |     |

| 0 <sub>1</sub> →     | 14 |          | 15 🔫 | -        | O <sub>2</sub>     |                                |     |  |  |  |  |  |      |  |      |                                    |     |

|                      |    |          |      |          |                    |                                |     |  |  |  |  |  |      |  |      |                                    |     |

| Anal  | og inputs                                                                            |

|-------|--------------------------------------------------------------------------------------|

| Addr  | ess lines for selecting analog inputs                                                |

| Digit | al 8-bit output with $O_7$ MSB and $O_0$ LSB                                         |

| Start | of conversion signal pin                                                             |

| End   | of conversion signal pin                                                             |

| Outp  | out latch enable pin, if high enable output                                          |

| Cloc  | k input for ADC                                                                      |

| Supp  | oly pins +5V and GND                                                                 |

|       | rence voltage positive (+5 Volts maximum)<br>Reference voltage negative (0V minimum) |

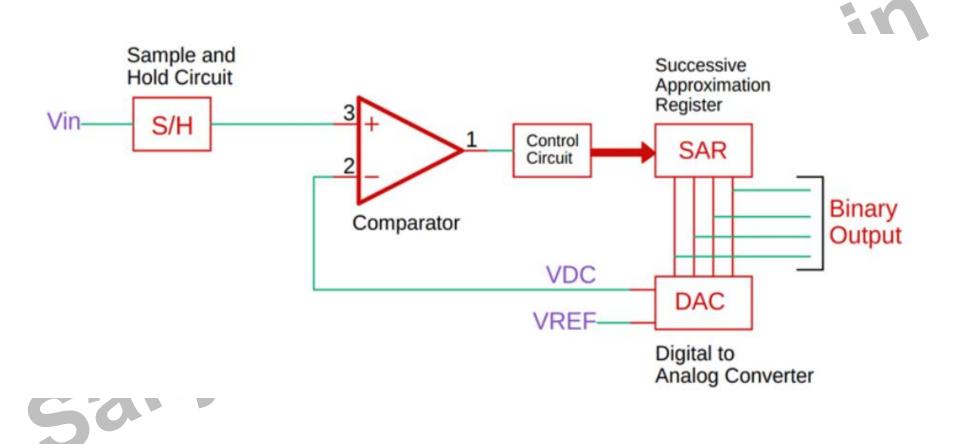

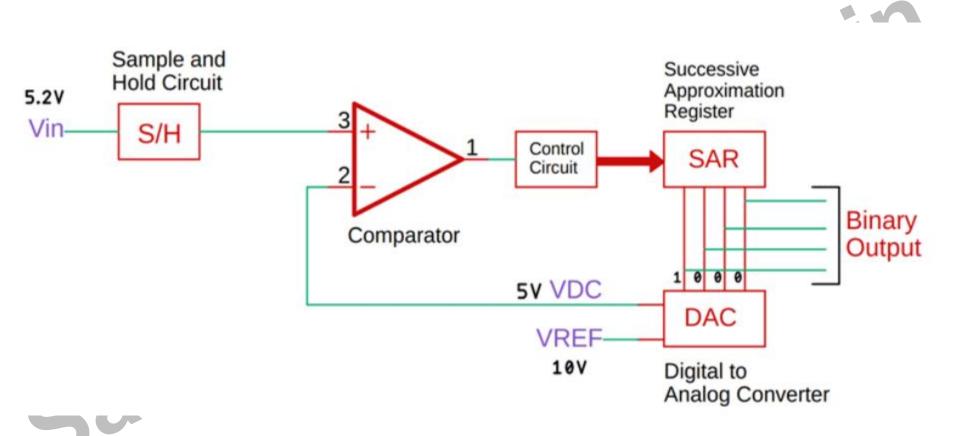

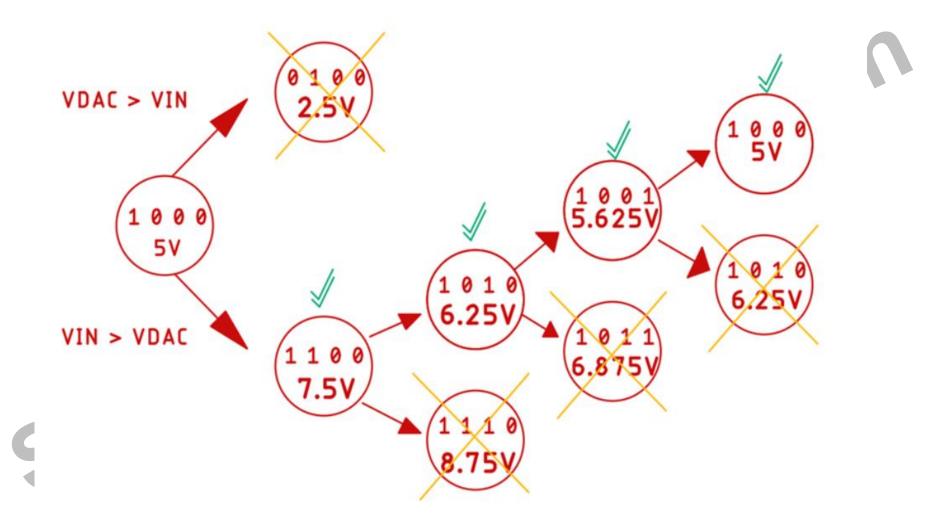

# **Successive Approximation ADC**

# **Successive Approximation ADC**

### **Successive Approximation ADC**

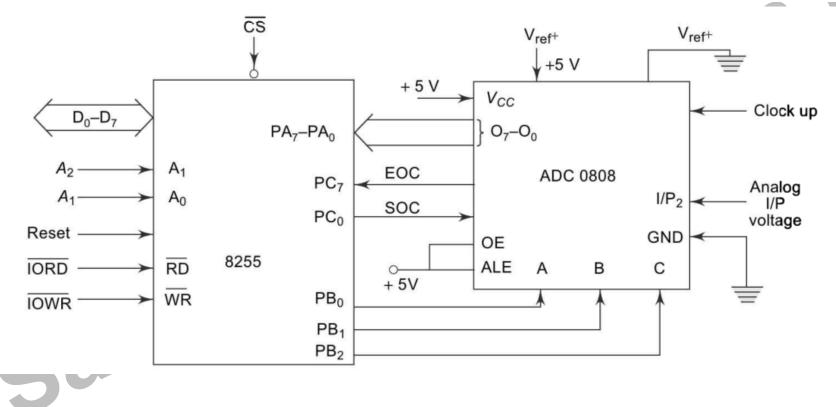

Interface ADC 0808 with 8086 using 8255 ports. Use Port A of 8255 for transferring digital data output of ADC to the CPU and Port C for control signals. Assume that an analog input is present at  $I/P_2$  of the ADC and a clock input of suitable frequency is available for ADC. Draw the schematic and write required ALP.

Interface ADC 0808 with 8086 using 8255 ports. Use Port A of 8255 for transferring digital data output of ADC to the CPU and Port C for control signals. Assume that an analog input is present at  $I/P_2$  of the ADC and a clock input of suitable frequency is available for ADC. Draw the schematic and write required ALP.

|      | D <sub>7</sub> | D <sub>6</sub>                                                                               | $D_5$                                                                                   | D <sub>4</sub> | $D_3$ | $D_2$                                                                                       | D <sub>1</sub>                                     | D <sub>0</sub>                                                               | Control w                               | ord                        |

|------|----------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------|-------|---------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|----------------------------|

|      | 1              | 0                                                                                            | 0                                                                                       | 1              | 1     | 0                                                                                           | 0                                                  | 0                                                                            | = 98 H                                  | D7=1; I/O Mode.            |

|      | The requ       | uired AL                                                                                     | P is give                                                                               | n as follo     | ws:   |                                                                                             |                                                    |                                                                              |                                         | D6=0 and D5=0; Port A Mode |

| WAIT | -<br>:         | OUT CV<br>MOV AI<br>OUT PC<br>MOV AI<br>OUT PC<br>MOV AI<br>OUT PC<br>IN AL<br>RCL<br>JNC WA | L,O2H<br>ORT B,A<br>L,OOH<br>ORT C,A<br>L,O1 H<br>ORT C,A<br>L,OOH<br>ORT C,A<br>,PORTC | L              |       | ; disc<br>; Sele<br>; inpu<br>; Give<br>; puls<br>;<br>;<br>;<br>; Chec<br>; reac<br>; rota | e start<br>se to t<br>ck for<br>ding po<br>ating t | above<br><sub>2</sub> as ar<br>of co<br>he ADC<br>EOC by<br>rt C u<br>hrough | nalog<br>nversion<br>pper and<br>carry. | ivalent in                 |

|      |                | HLT                                                                                          |                                                                                         |                |       | ; Stop                                                                                      | D                                                  |                                                                              |                                         | 10                         |

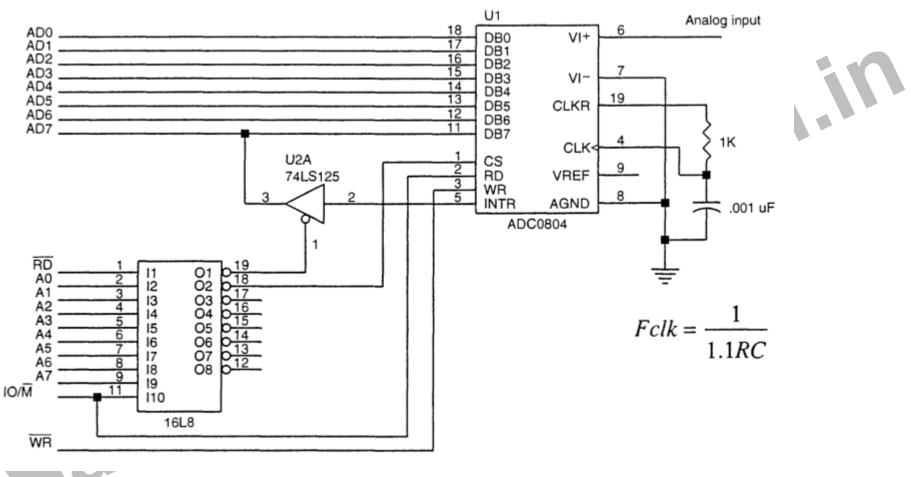

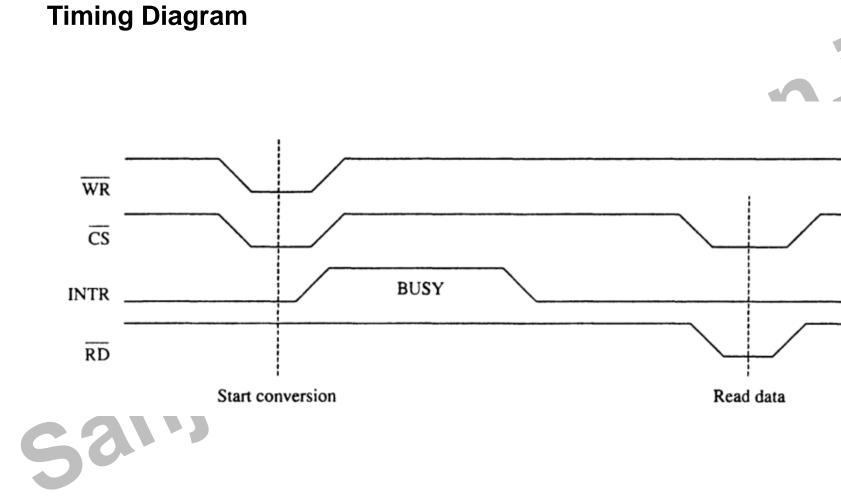

SOC: Start of Conversion WR' and CS' EOC : End of Conversion INTR

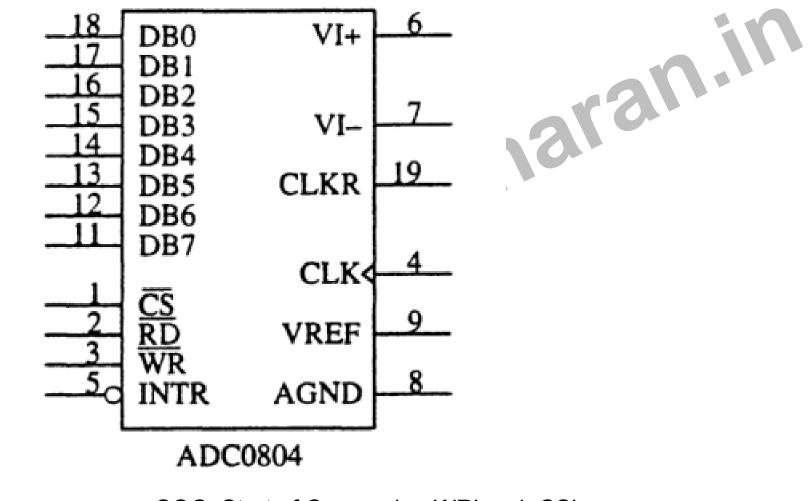

#### ADC 0804

Permissible range of clock frequencies is 100 KHz - 1460 KHz. desirable to use a frequency as close as possible to 1460 KHz so conversion time is minimized

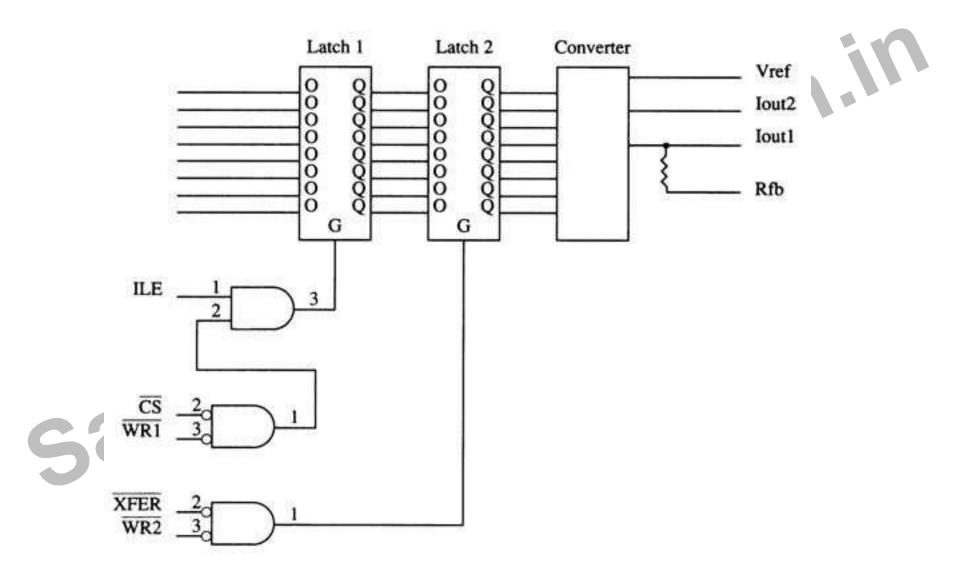

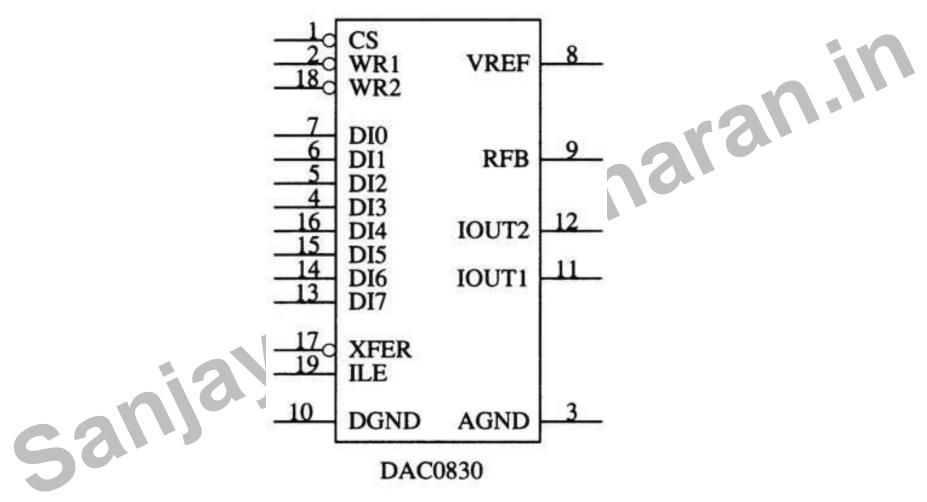

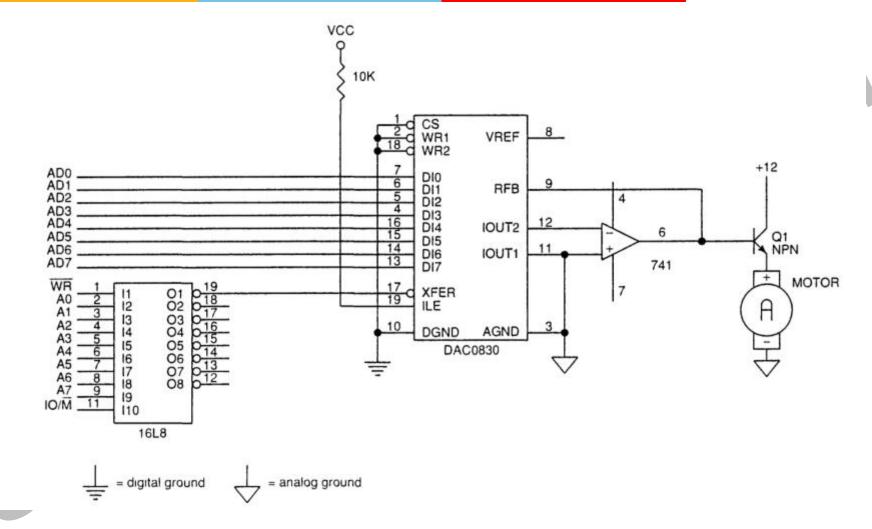

- A fairly common and low-cost digital-to-analog converter is the DAC0830.

- An 8-bit converter that transforms an 8-bit binary number into an analog voltage.

- Other converters are available that convert from 10-, 12-, or 16-bit binary numbers into analog voltages.

- The number of voltage steps generated by the converter is equal to the number of binary input combinations.

- an 8-bit converter generates 256 voltage levels

- a 10-bit converter generates 1024 levels

- The DAC0830 is a medium-speed converter that transforms a digital input to an analog output in approximately  $1.0 \,\mu$ s.

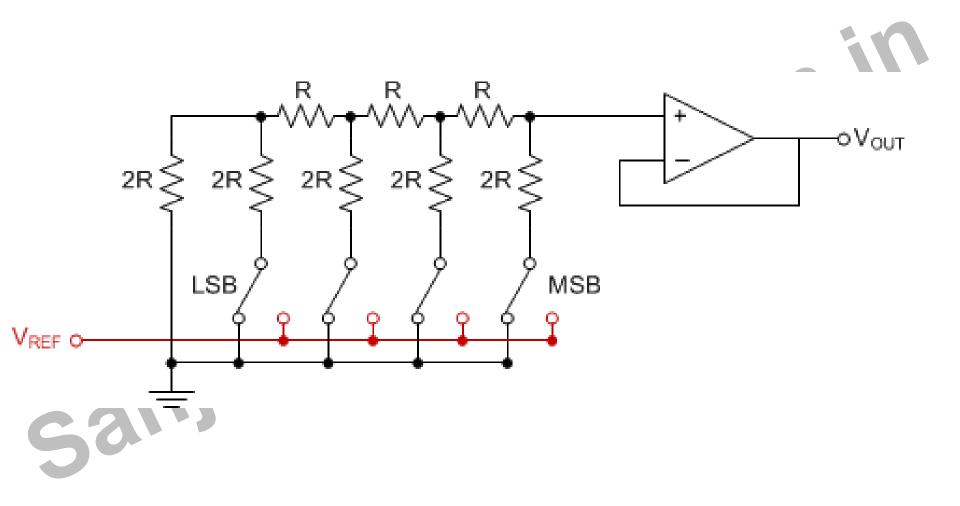

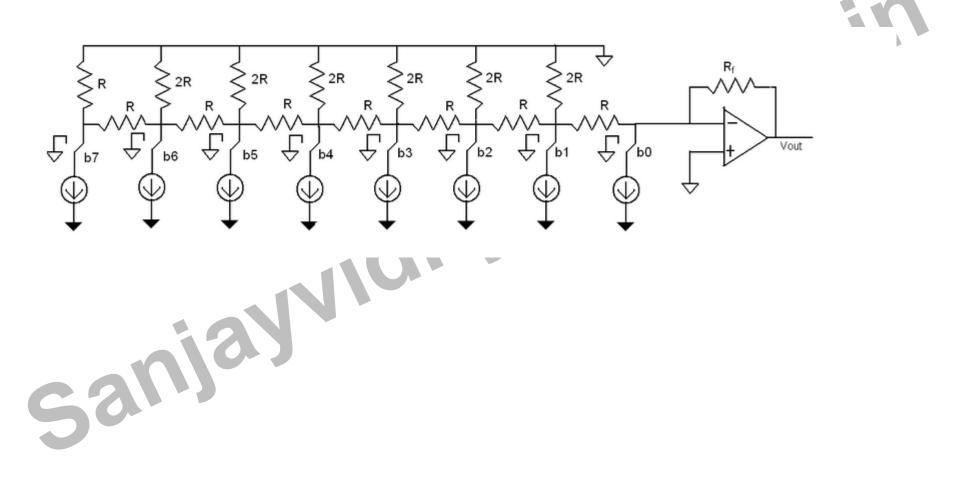

### **R-2R Ladder DAC**

### **R-2R Ladder DAC**

Because this is an 8-bit converter, its output step voltage is defined as  $-V_{REF}$  (reference voltage), divided by 255. The step voltage is often called the resolution of the converter

Analog outputs labeled IOUT1 & IOUT2 are inputs to an external operational amplifier.