# Microprocessors and Interfaces: 2021-22 Lecture 3 8086 Pin Diagram and Architecture

# By Dr. Sanjay Vidhyadharan

**S**311

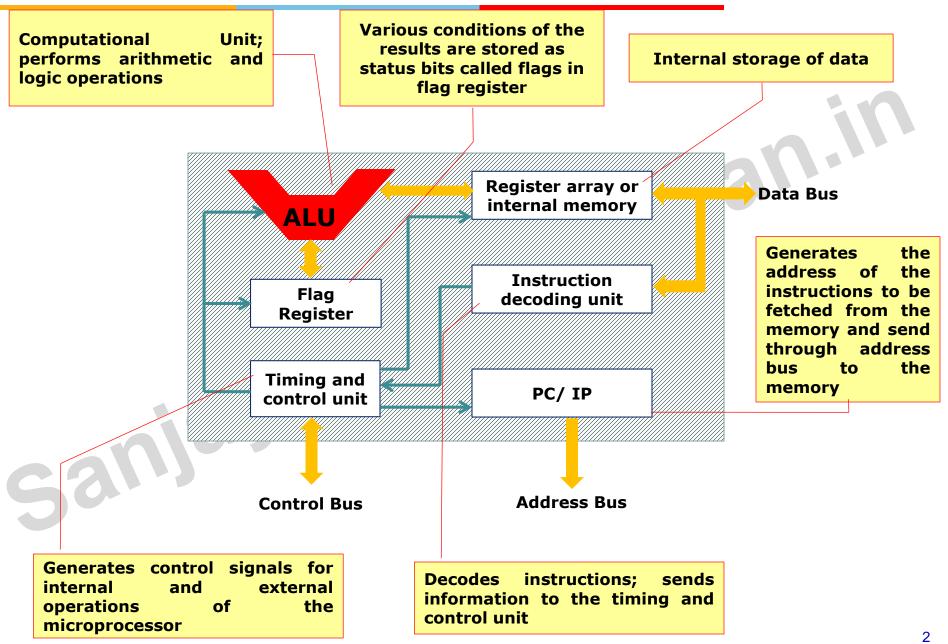

# **Functional blocks**

# **Functional blocks**

First 16- bit processor released by INTEL in the year 1978

Originally HMOS, now manufactured using HMOS III technique

Approximately 29, 000 transistors, 40 pin DIP, 5V supply

Does not have internal clock; external asymmetric clock source with 33% duty cycle

**20-bit address to access memory**  $\Rightarrow$  can address up to  $2^{20} = 1$  megabytes of memory space.

Addressable memory space is organized in to two banks of 512 kb each; Even (or lower) bank and Odd (or higher) bank. Address line  $A_0$  is used to select even/odd bank and control signal BHE to select 16 bit data.

Uses a separate 16 bit address for I/O mapped devices  $\Rightarrow$  can generate  $2^{16} = 64$  k addresses.

Operates in two modes: minimum mode and maximum mode, decided by the signal at MN and  $\overline{MX}$  pins.

### **Common signals**

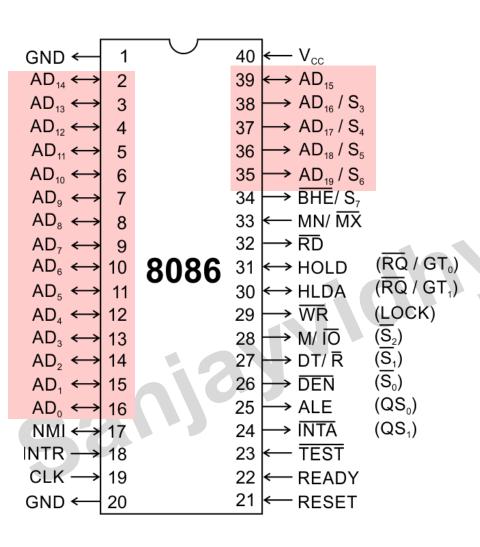

### AD<sub>0</sub>-AD<sub>15</sub> (Bidirectional)

### Address/Data bus

Low order address bus; these are multiplexed with data.

When AD lines are used to transmit memory address the symbol A is used instead of AD, for example  $A_0$ - $A_{15}$ .

When data are transmitted over AD lines the symbol D is used in place of AD, for example  $D_0-D_7$ ,  $D_8-D_{15}$  or  $D_0-D_{15}$ .

$A_{16}/S_{31}$   $A_{17}/S_{41}$   $A_{18}/S_{51}$   $A_{19}/S_{61}$

High order address bus. These are multiplexed with status signals

### **Common signals**

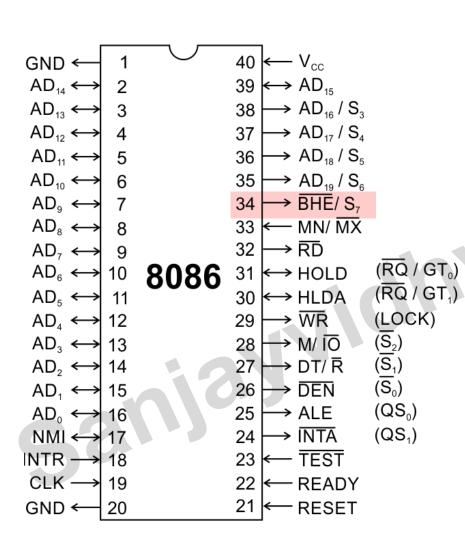

BHE (Active Low)/S<sub>7</sub> (Output)

### **Bus High Enable/Status**

It is used to enable data onto the most significant half of data bus,  $D_8-D_{15}$ . 8-bit device connected to upper half of the data bus use BHE (Active Low) signal. It is multiplexed with status signal  $S_7$ .

### MN/ MX

### MINIMUM / MAXIMUM

This pin signal indicates what mode the processor is to operate in.

### RD (Read) (Active Low)

The signal is used for read operation. It is an output signal. It is active when low.

### **Common signals**

### TEST

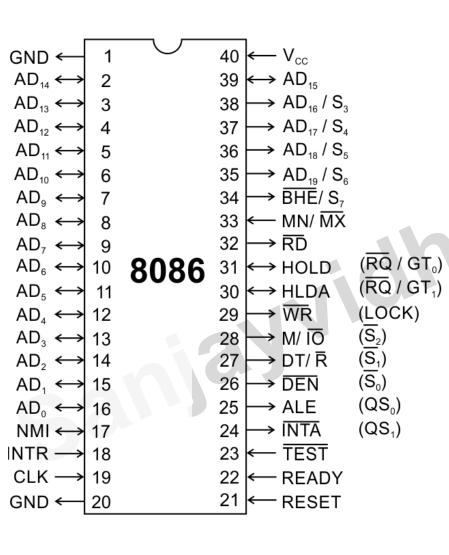

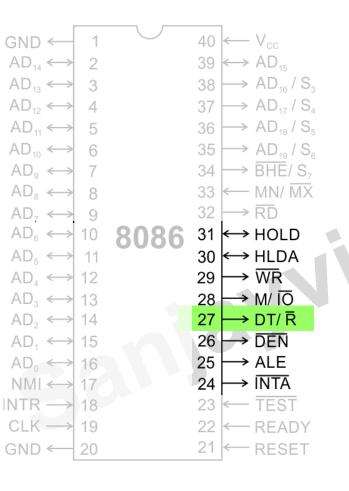

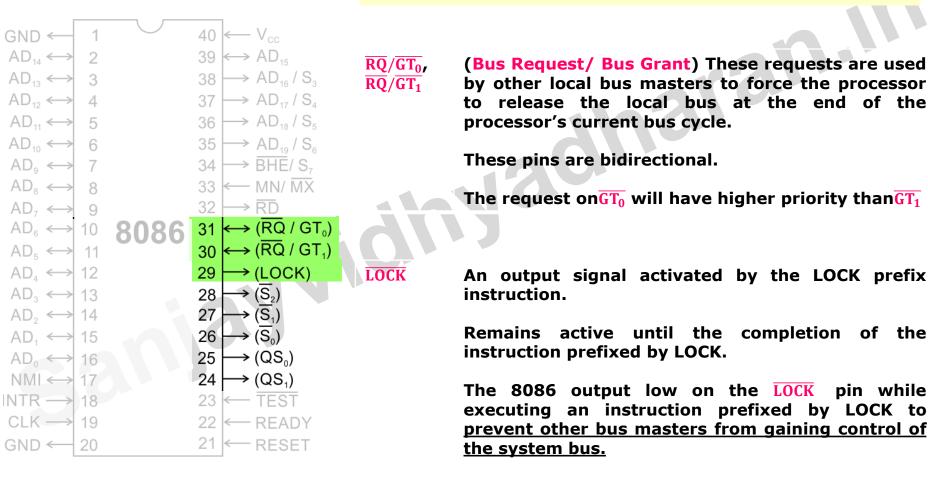

$GND \leftarrow 1$ 40 ← V<sub>cc</sub>  $39 \leftrightarrow AD_{15}$  $AD_{14} \leftrightarrow 2$  $AD_{13} \leftrightarrow 3$  $38 \rightarrow AD_{16} / S_3$  $AD_{12} \leftrightarrow 4$  $37 \mapsto AD_{17} / S_{4}$  $AD_{11} \leftrightarrow 5$  $36 \rightarrow AD_{18} / S_5$  $AD_{10} \leftrightarrow 6$  $35 \rightarrow AD_{19} / S_6$  $AD_9 \leftrightarrow 7$  $34 \rightarrow \overline{BHE}/S_{7}$  $AD_8 \leftrightarrow 8$ 33 ← MN/ MX  $32 \longrightarrow \overline{RD}$  $AD_7 \leftrightarrow 9$  $(RQ / GT_0)$  $AD_6 \leftrightarrow 10$ 8086  $31 \leftrightarrow HOLD$ (RQ / GT.)  $AD_5 \leftrightarrow 11$  $30 \leftrightarrow HLDA$ (LOCK)  $AD_4 \leftrightarrow 12$  $29 \longrightarrow \overline{WR}$  $(S_2)$  $28 \rightarrow M/\overline{10}$  $AD_3 \leftrightarrow 13$ (S<sub>1</sub>)  $AD_2 \leftrightarrow 14$  $27 \rightarrow DT/\overline{R}$  $(\overline{S}_0)$  $26 \rightarrow \overline{\text{DEN}}$  $AD_1 \leftrightarrow 15$  $(QS_0)$  $25 \mapsto ALE$  $AD_0 \leftrightarrow 16$  $(QS_1)$  $NMI \leftrightarrow 17$  $24 \mapsto \overline{\text{INTA}}$ 23 ← TEST  $INTR \rightarrow 18$  $CLK \longrightarrow 19$ 22 ← READY  $GND \leftarrow 20$ 21 ← RESET

TEST input is tested by the 'WAIT' instruction.

8086 will enter a wait state after execution of the WAIT instruction and will resume execution only when the TEST is made low by an active hardware.

This is used to synchronize an external activity to the processor internal operation.

### READY

This is the acknowledgement from the slow device or memory that they have completed the data transfer.

The signal made available by the devices is synchronized by the 8284A clock generator to provide ready input to the 8086.

The signal is active high.

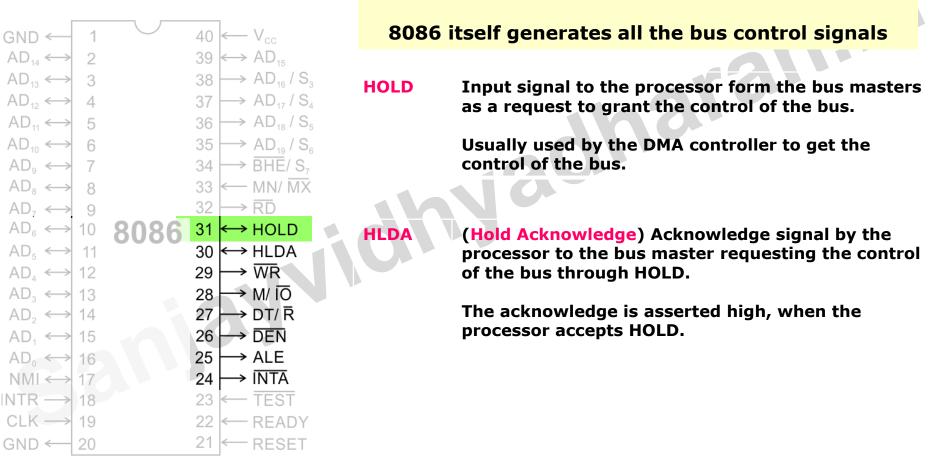

### Min/ Max Pins

The 8086 microprocessor can work in two modes of operations : Minimum mode and Maximum mode.

In the <u>minimum mode</u> of operation the microprocessor <u>do not</u> associate with any co-processors and can not be used for multiprocessor systems.

In the <u>maximum mode</u> the 8086 <u>can work</u> in multi-processor or co-processor configuration.

Minimum or maximum mode operations are decided by the pin MN/ MX(Active low).

When this pin is <u>high</u> 8086 operates in <u>minimum mode</u> otherwise it operates in Maximum mode.

Pins 24 -31

# For minimum mode operation, the MN/ $\overline{MX}$ is tied to VCC (logic high)

8086 itself generates all the bus control signals DT/R (Data Transmit/ Receive) Output signal from the processor to control the direction of data flow through the data transceivers **DEN** (Data Enable) Output signal from the processor used as out put enable for the transceivers (Address Latch Enable) Used to demultiplex the **ALE** address and data lines using external latches  $M/\overline{10}$ Used to differentiate memory access and I/O access. For memory reference instructions, it is high. For IN and OUT instructions, it is low. WR Write control signal; asserted low Whenever processor writes data to memory or I/O port **INTA** (Interrupt Acknowledge) When the interrupt request is accepted by the processor, the output is

low on this line.

Pins 24 -31

# For minimum mode operation, the MN/ $\overline{MX}$ is tied to VCC (logic high)

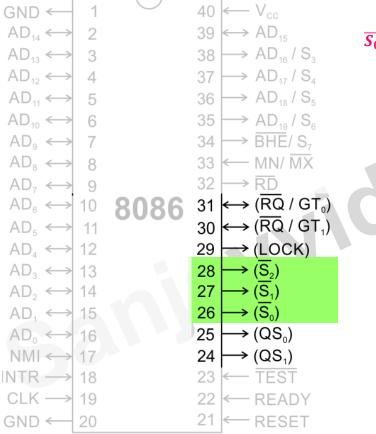

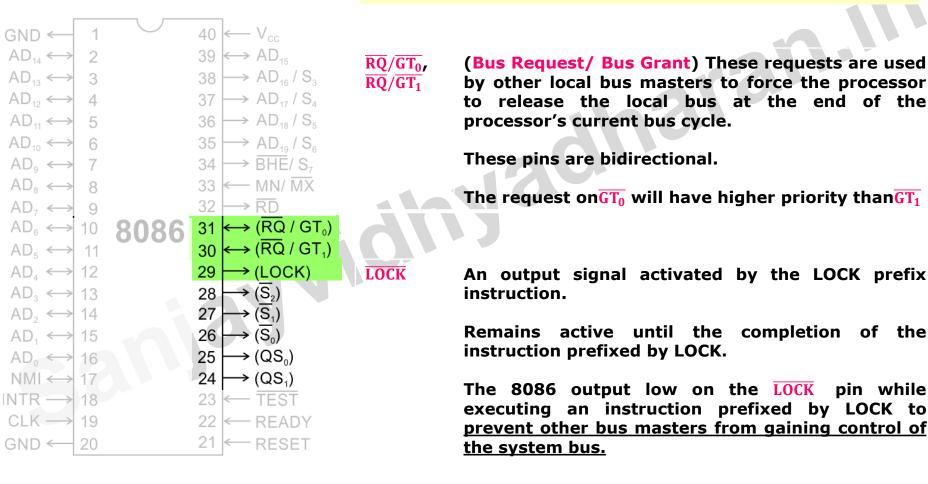

## During maximum mode operation, the MN/ MX is grounded (logic low)

Pins 24 -31 are reassigned

$\overline{S_0}$ ,  $\overline{S_1}$ ,  $\overline{S_2}$

Status signals; used by the 8086 bus controller to generate bus timing and control signals. These are decoded as shown.

| Status Signal    |                             |                  | Mashina Cuala         |

|------------------|-----------------------------|------------------|-----------------------|

| $\overline{S}_2$ | $\overline{\mathbf{S}}_{1}$ | $\overline{S}_0$ | Machine Cycle         |

| 0                | 0                           | 0,               | Interrupt acknowledge |

| 0                | 0                           | 1                | Read I/O port         |

| 0                | 1                           | 0                | Write I/O port        |

| 0                | 1                           | 1                | Halt                  |

| 1                | 0                           | 0                | Code access           |

| 1                | , <b>0</b> °                | 1                | Read memory           |

| 1                | 1                           | 0                | Write memory          |

| 1                | 1                           | 1                | Passive/Inactive      |

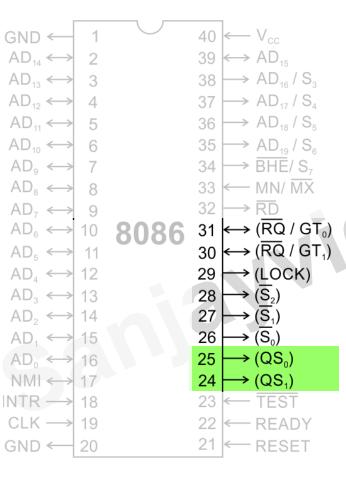

During maximum mode operation, the MN/ MX is grounded (logic low)

Pins 24 - 31 are reassigned

$\overline{QS_0}, \overline{QS_1}$

(Queue Status) The processor provides the status of queue in these lines.

The queue status can be used by external device to track the internal status of the queue in 8086.

The output on  $QS_0$  and  $QS_1$  can be interpreted as shown in the table.

| Queue status    |                 |                                    |  |

|-----------------|-----------------|------------------------------------|--|

| QS <sub>1</sub> | QS <sub>0</sub> | Queue operation                    |  |

| 0               | 0               | No operation                       |  |

| 0               | 1               | First byte of an opcode from queue |  |

| 1               | 0               | Empty the queue                    |  |

| 1               | 1               | Subsequent byte from queue         |  |

# During maximum mode operation, the MN/ MX is grounded (logic low)

Pins 24 - 31 are reassigned

# During maximum mode operation, the MN/ MX is grounded (logic low)

Pins 24 - 31 are reassigned

# Thankyou dharan.in Sanjayyidhya