# Microprocessors and Interfaces: 2021-22 Lecture 27:

8255 Programmable Peripheral Interface Part:1

By Dr. Sanjay Vidhyadharan

#### 8255- PPI

#### 8255- PPI

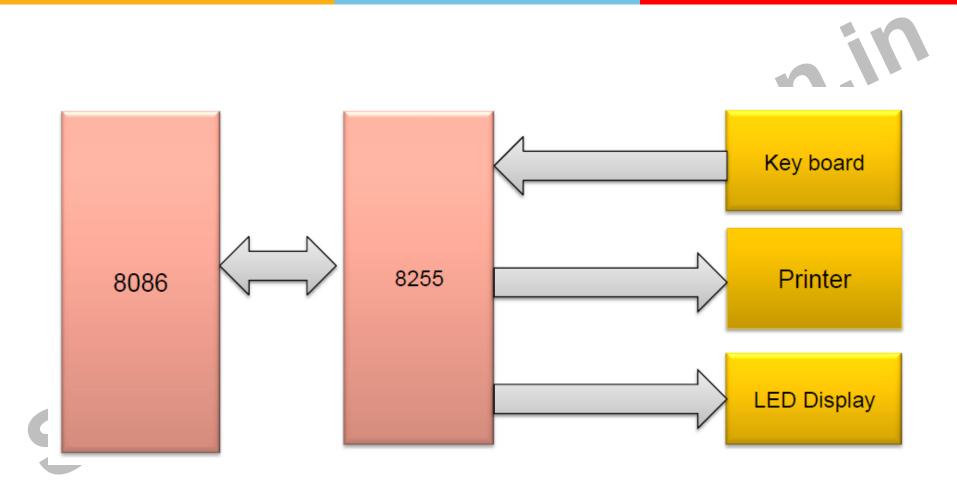

Intel has developed several peripheral control chips for 80x86 family

-provide complete I/O interface to x86 chip

#### 8255 PPI

PPI provides 3, 8-bit I/O ports (A, B and C) in one package Chip can be directly interfaced to the data bus of 8086.

#### Other Peripheral Devices

8253/8254 –Programmable Interval Timer (PIT)

8259 – Programmable Interrupt Controller (PIC)

8237 – Direct memory Access Controller (DMAC)

#### 8255- PPI

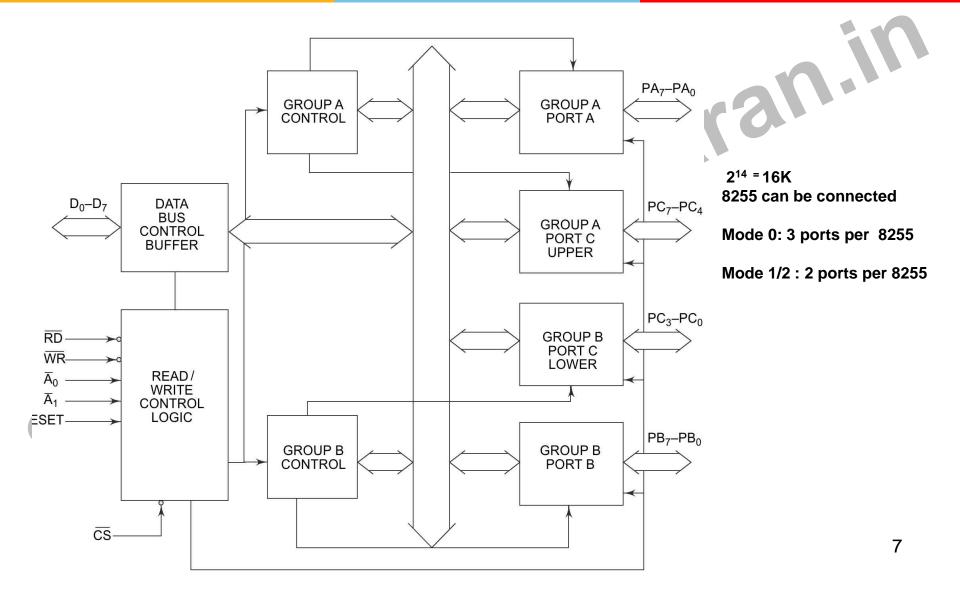

- 82C55 programmable peripheral interface (PPI) is a popular, low-cost interface component

- The PPI has 24 pins for I/O, programmable in groups of 8/12 pins (Group A,B,C)

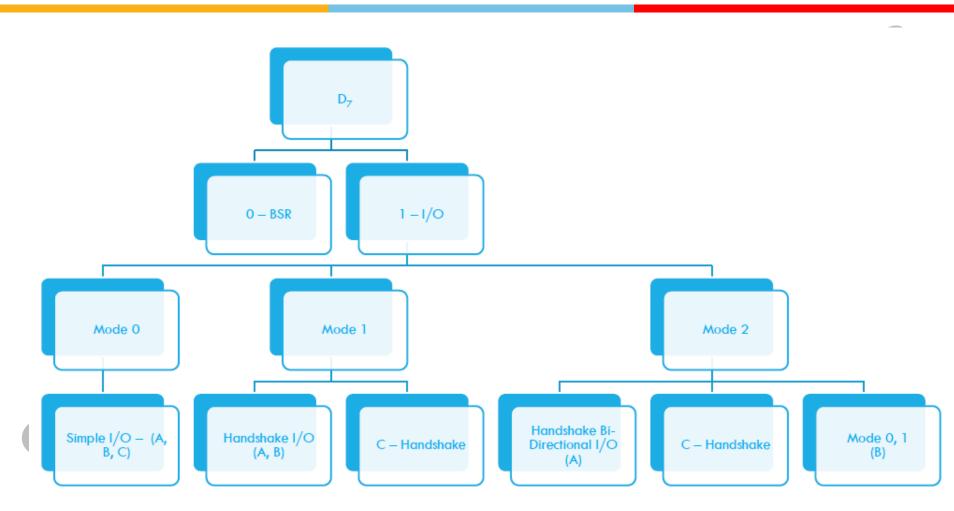

- The groups operate in three distinct modes of operation (Mode 0, Mode 1 and Mode 2)

- The 82C55 (CMOS version) requires wait states if operated with a processor using higher than an 8 MHz clock.

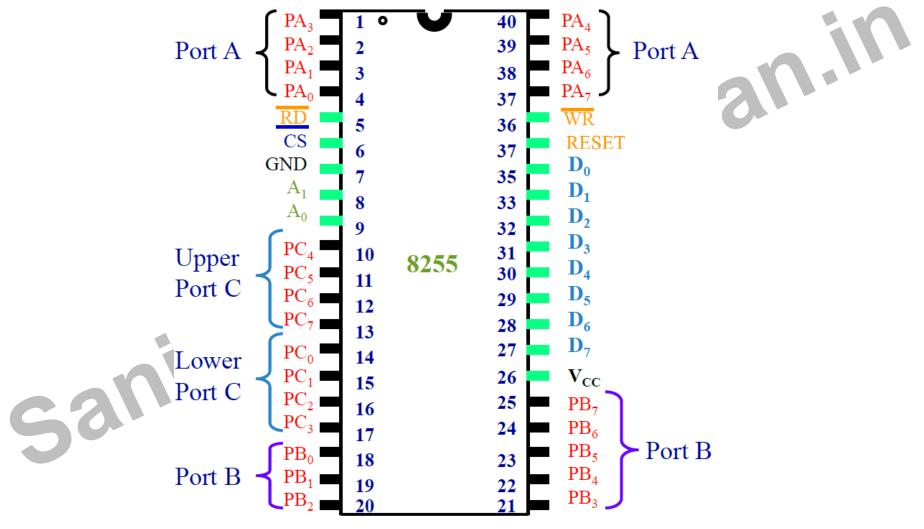

## Pin Diagram of 8255

# **Selection of ports**

| CS' | $\mathbf{A}_1$ | A <sub>o</sub> | Selected          |  |  |

|-----|----------------|----------------|-------------------|--|--|

| 0   | 0              | 0              | Port A            |  |  |

| 0   | 0              | 1              | Port B            |  |  |

| 0   | 1              | 0              | Port C            |  |  |

| 0   | 1              | 1              | Control Register  |  |  |

| 1   | X              | X              | 8255 Not Selected |  |  |

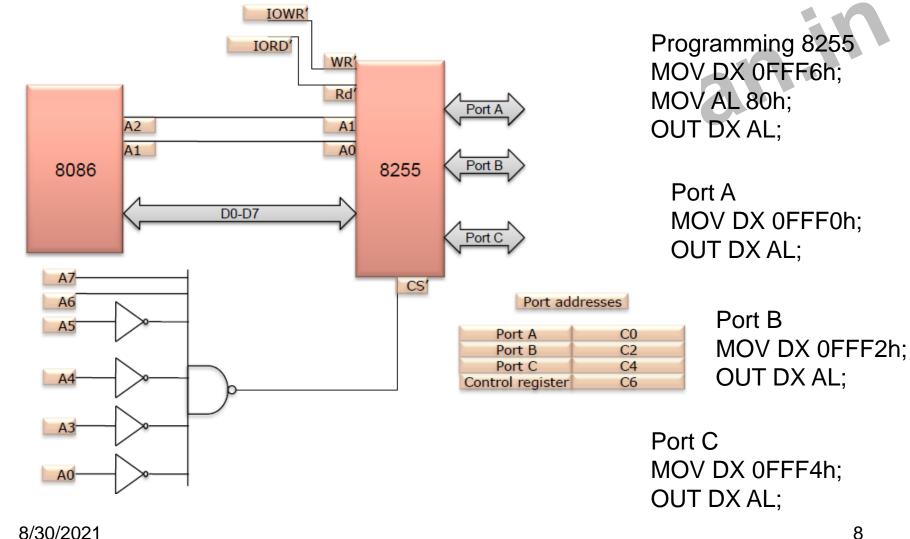

**Selecting Port / Programming 8255**

# Internal block diagram of 8255

## **Interfacing with 8086**

8

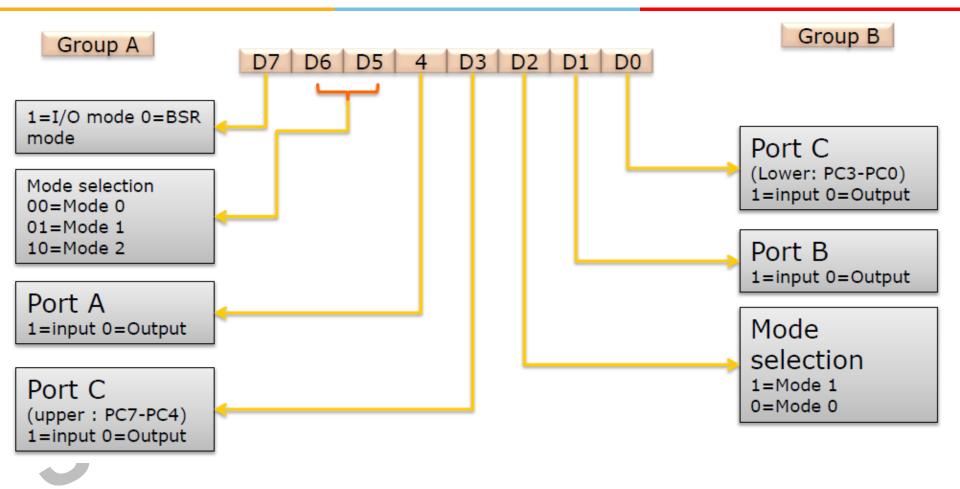

#### **Control word Format**

#### **Control word Format**

|        | $D_7$                          | $D_6$                                        | $D_5$ | $D_4$              | $D_3$              | $D_2$              | $D_{i}$           | $D_{o}$            |

|--------|--------------------------------|----------------------------------------------|-------|--------------------|--------------------|--------------------|-------------------|--------------------|

|        |                                | Port A Mode                                  |       | Port A             | Port C<br>Upper    | Port B<br>Mode     | Port              | Port C<br>Lower    |

|        | Always<br>1 for<br>I/O<br>Mode | 0 0 - Mode 0<br>0 1 - Mode 1<br>1 x – Mode 2 |       | 1 - I/P<br>o - O/P | 1 - I/P<br>o - O/P | o-Modeo<br>1-Mode1 | 1 - I/P<br>o -O/P | 1 - I/P<br>o - O/P |

| 1<br>1 |                                |                                              | Gro   | up A               | Group B            |                    |                   |                    |

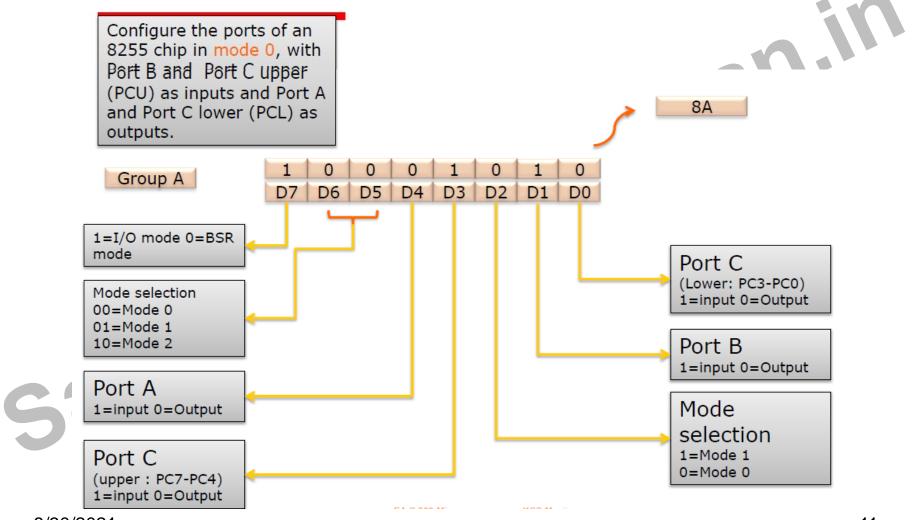

## **Example**

# Modes of operation of 8255

8/30/2021 12

# Thank You