**Digital Design**

Digital Design

Lecture 15: Sequential Logic & SR Latch sanjayvidi

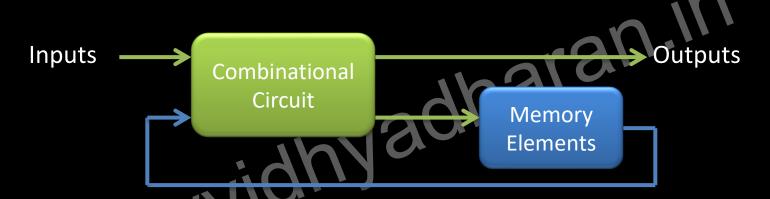

Combinational circuits – The outputs are entirely dependent on current inputs

Sequential circuits

The outputs are dependent on current inputs as well as present state of storage elements

Next state = external inputs + present state

Classification

**Synchronous Sequential circuits**

Asynchronous Sequential circuits

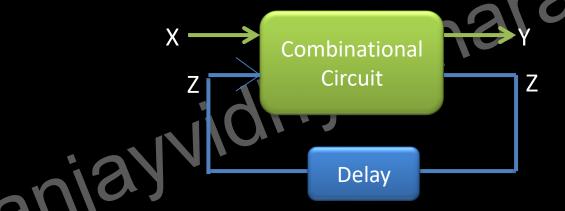

Asynchronous sequential circuits

The transition from one state to another is initiated by the change in the primary inputs there is no external synchronization

The memory commonly used are time-delayed devices

May be regarded as combinational circuits with feedback.

May become unstable

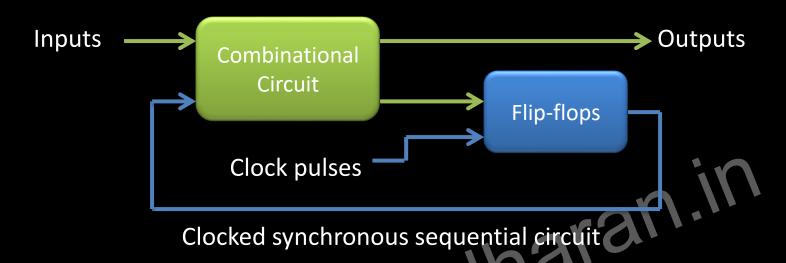

Synchronous sequential circuit

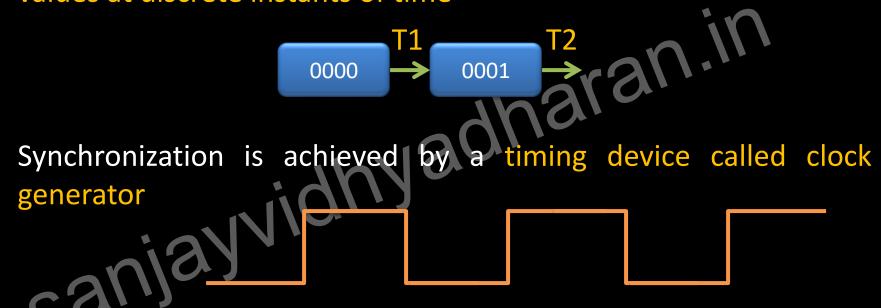

Synchronous sequential circuits change their states and output values at discrete instants of time

Clock generator generates a clock signal having the form of a periodic train of pulses

Storage elements are flip-flops

Output value stored in flip-flop when clock occurs

Prior to the occurrence of the clock the combinational output must be stable

Speed of the combinational logic is critical

Maintains a binary state indefinitely until directed by an input signal to switch states

#### Latches

Storage elements that operate with signal levels (rather than Nighlagu signal transitions) Latch active

**Level Sensitive**

Flip-Flops

Storage elements that are controlled by clock transitions

**Edge Sensitive**

Maintains a binary state indefinitely until directed by an input signal to switch states

#### Latches

Maduales Storage elements that operate with signal levels (rather than signal transitions)

**Level Sensitive**

Storage elements that are controlled by clock transitions

**Edge Sensitive**

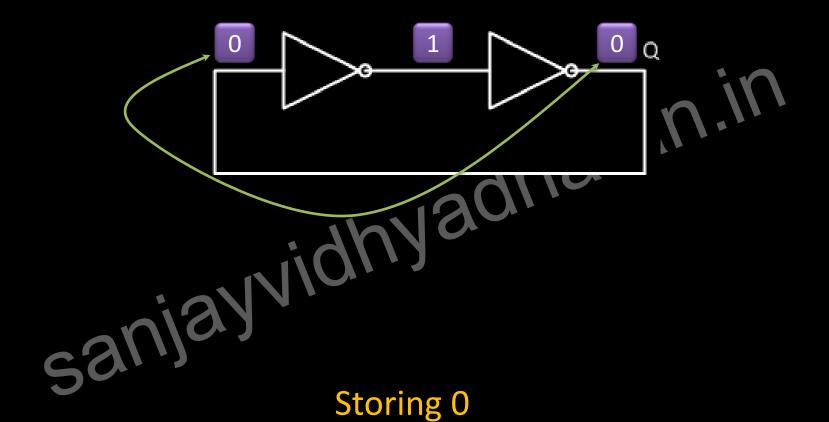

Is there any way to control the storage value?

## **NOR-NAND**

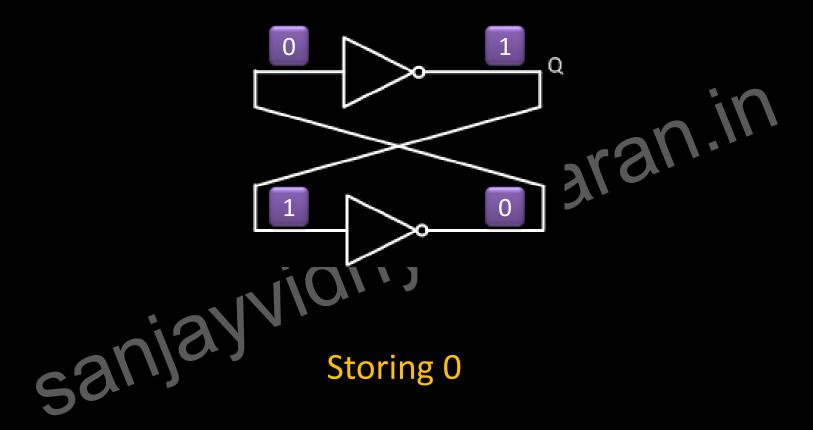

### **SR Latch**

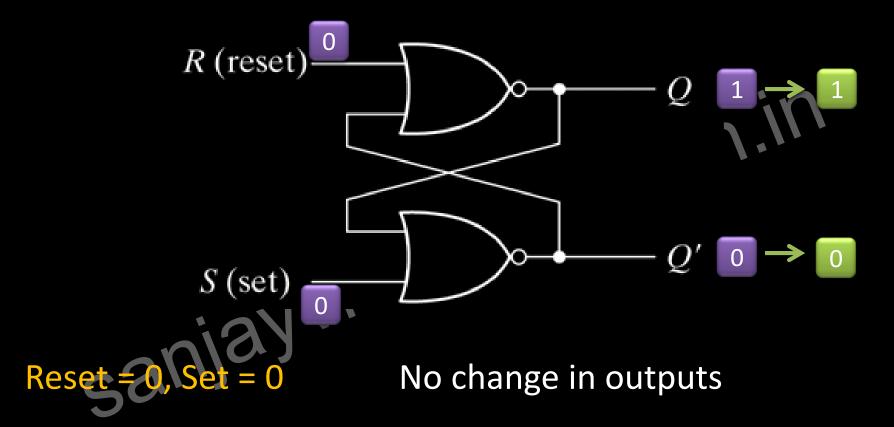

New state = Old state

### **SR Latch**

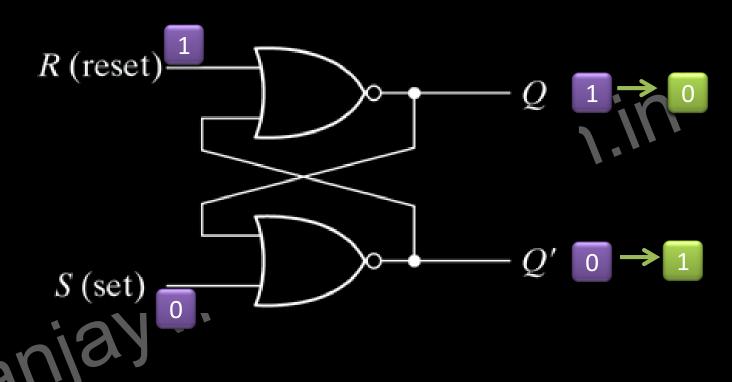

Reset =

$$1$$

, Set =  $0$

$$Q = 0$$

and  $Q' = 1$

Reset operation

### **SR Latch**

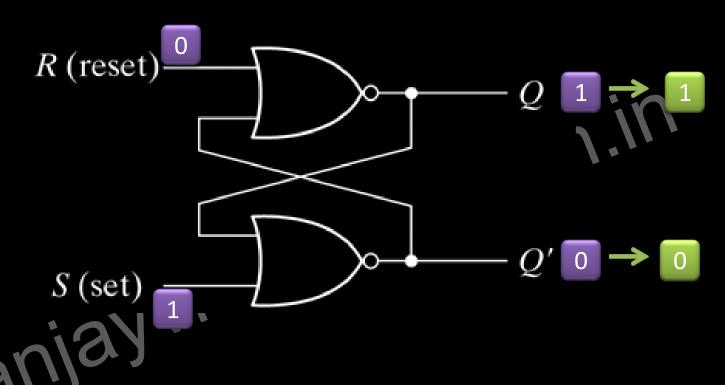

Reset = 0, Set = 1 Q = 1 and Q' = 0

Set operation

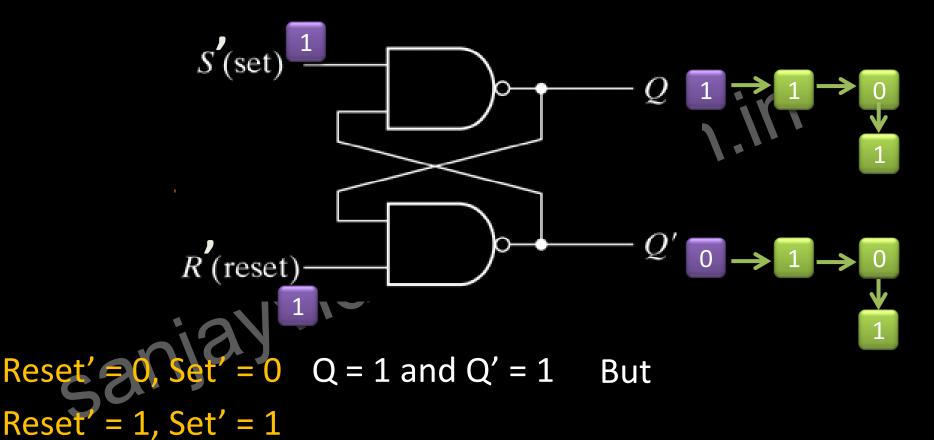

#### **SR Latch**

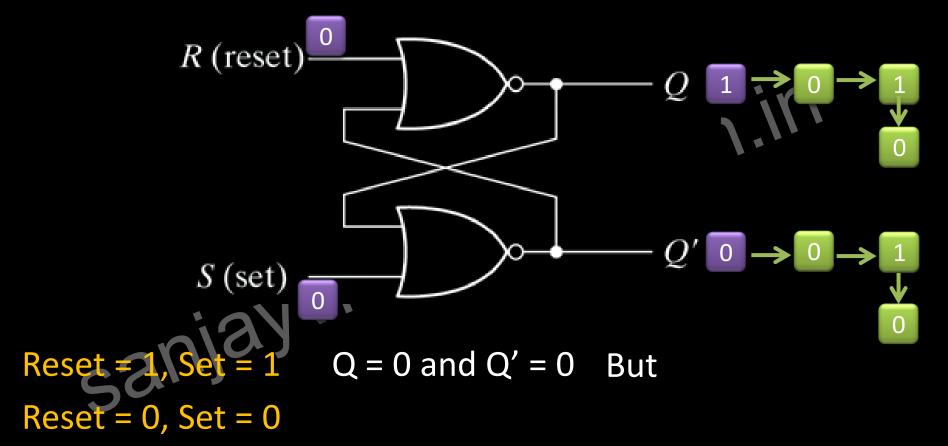

Cant predict output - > metastable state

#### **SR Latch**

Cant predict output - > metastable state

Set = 1, reset = 1 is thus forbidden state

|      | S | R | Q | Q' |

|------|---|---|---|----|

|      | 0 | 0 | Q | Q' |

| :01  | 0 | 1 | 0 | 1  |

| anla | 1 | 0 | 1 | 0  |

| 50.  | 1 | 1 | 0 | 0  |

No change

Reset

set

Forbidden

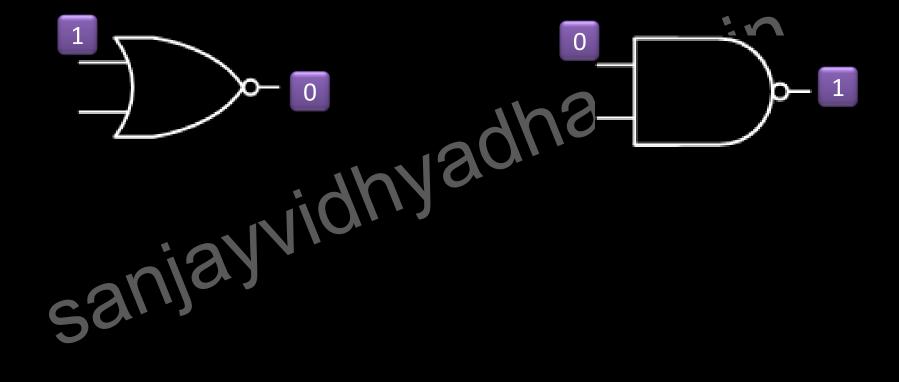

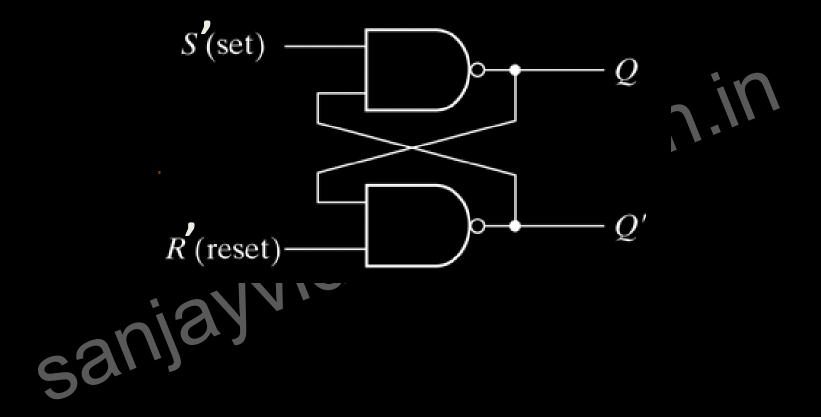

# S'R' Latch

## S'R' Latch

|             | S | R | Q | Q' |  |  |  |

|-------------|---|---|---|----|--|--|--|

|             | 0 | 0 | 1 | 1  |  |  |  |

|             | 0 | 1 | 1 | 0  |  |  |  |

|             | 1 | 0 | 0 | 1  |  |  |  |

|             | 1 | 1 | Q | à  |  |  |  |

| sanjayvidny |   |   |   |    |  |  |  |

Forbidden

Reset

No change

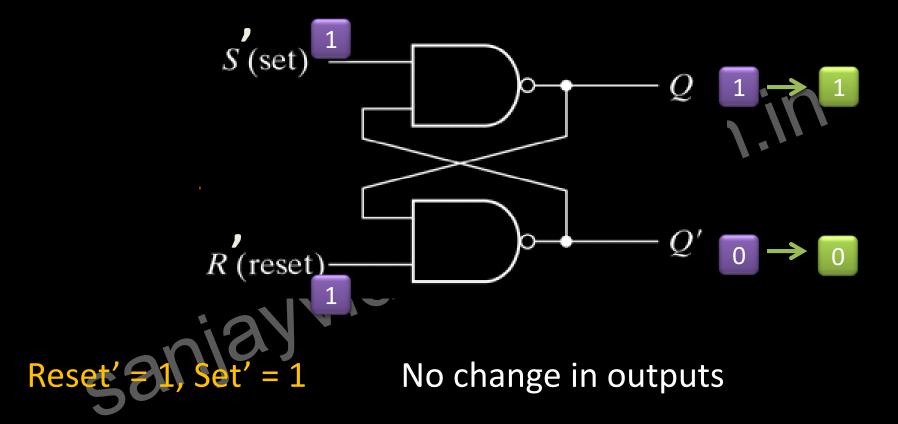

### S'R' Latch

New state = Old state

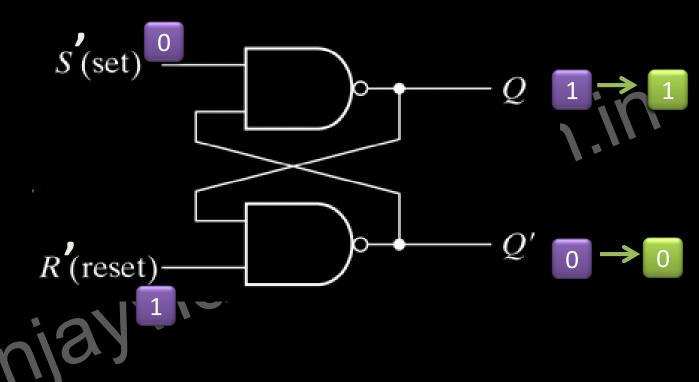

### S'R' Latch

Reset = 1, Set' = 0 Q = 1 and Q' = 0

set operation

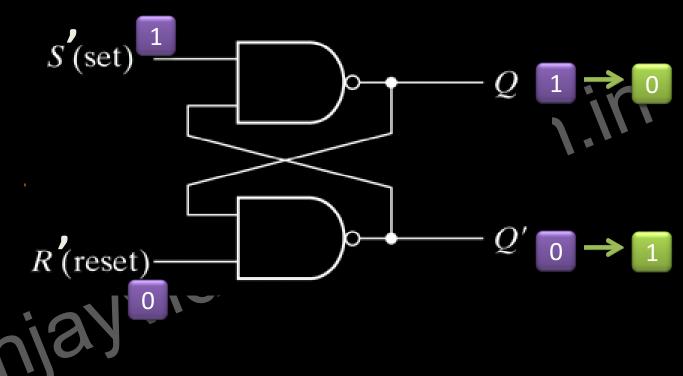

### **SR Latch**

Reset' = 0, Set' = 1 Q = 0 and Q' = 1

Reset operation

#### **SR Latch**

Cant predict output - > metastable state

## S'R' Latch

|             | S | R | Q | Q' |  |  |  |

|-------------|---|---|---|----|--|--|--|

|             | 0 | 0 | 1 | 1  |  |  |  |

|             | 0 | 1 | 1 | 0  |  |  |  |

|             | 1 | 0 | 0 | 1  |  |  |  |

|             | 1 | 1 | Q | à  |  |  |  |

| sanjayvidny |   |   |   |    |  |  |  |

Forbidden

Reset

No change

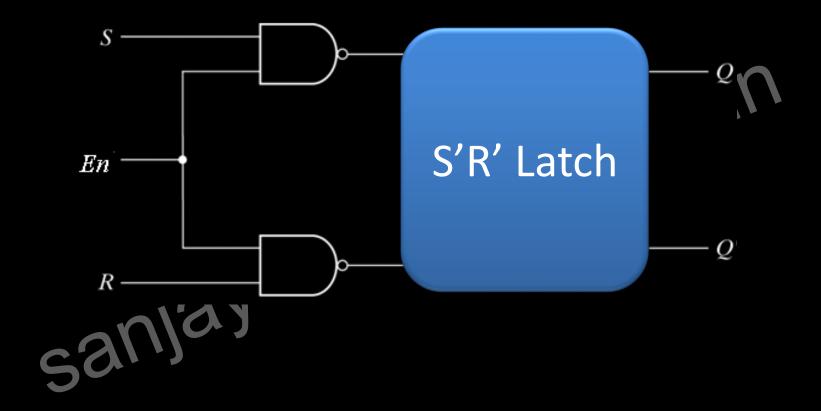

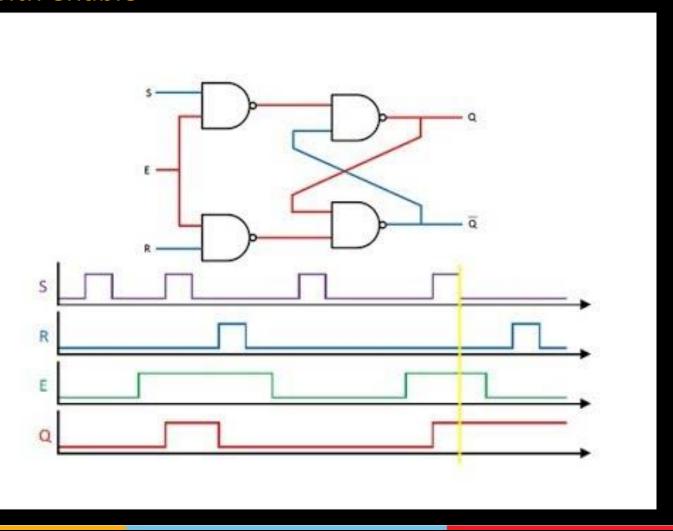

## SR Latch with enable

# SR Latch with enable

Thank Youran.in sanjayvidhyadharan.in