# By Dr. Sanjay Vidhyadharan

### Sanjay

### **Outline**

- > Review of Digital Gates

- Digital Logic families

- Few 74XX series TTL Digital ICs

- > Procedure for installation of LT SPICE

- Problem definition for DD: Lab 1

- > Demonstration of LT SPICE installation and simulation.

Jaran

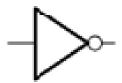

### **Review of Digital Gates**

| INPUT | ОПТРИТ |

|-------|--------|

| Α     | OUIFUI |

| 0     | 0      |

| 1     | 1      |

| INPUT | OUTPUT |  |

|-------|--------|--|

| А     | OUIPUI |  |

| 0     | 1      |  |

| 1     | 0      |  |

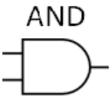

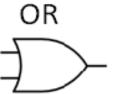

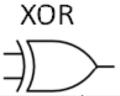

### **Review of Digital Gates**

| INF | PUT | CUTRUT |  |

|-----|-----|--------|--|

| Α   | В   | ОИТРИТ |  |

| 0   | 0   | 0      |  |

| 1   | 0   | 0      |  |

| 0   | 1   | 0      |  |

| 1   | 1   | 1      |  |

| INI | PUT | OUTDUT |  |

|-----|-----|--------|--|

| Α   | В   | OUTPUT |  |

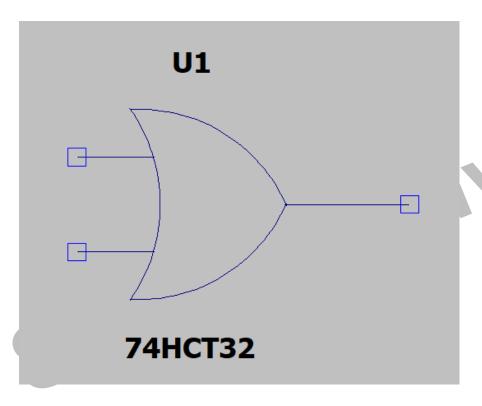

| 0   | 0   | 0      |  |

| 1   | 0   | 1      |  |

| 0   | 1   | 1      |  |

| 1   | 1   | 1      |  |

| INI | PUT | OUTPUT |

|-----|-----|--------|

| Α   | В   | OOIFOI |

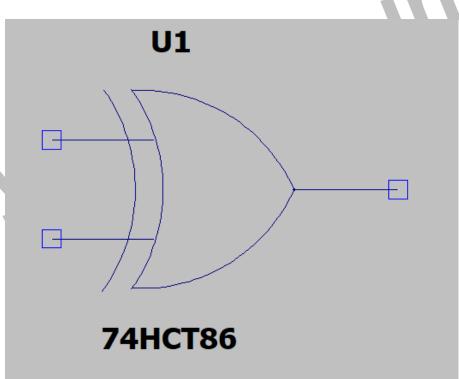

| 0   | 0   | 0      |

| 1   | 0   | 1      |

| 0   | 1   | 1      |

| 1   | 1   | 0      |

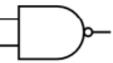

### **Review of Digital Gates**

| INI | PUT | OUTDUT |  |

|-----|-----|--------|--|

| Α   | В   | OUTPUT |  |

| 0   | 0   | 1      |  |

| 1   | 0   | 1      |  |

| 0   | 1   | 1      |  |

| 1   | 1   | 0      |  |

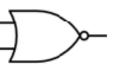

NOR

| INI | PUT | OUTPUT |

|-----|-----|--------|

| Α   | В   | 001701 |

| 0   | 0   | 1      |

| 1   | 0   | 0      |

| 0   | 1   | 0      |

| 1   | 1   | 0      |

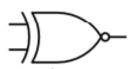

**XNOR**

| INI | PUT | OUTPUT |  |  |

|-----|-----|--------|--|--|

| Α   | В   | OUIPUI |  |  |

| 0   | 0   | 1      |  |  |

| 1   | 0   | 0      |  |  |

| 0   | 1   | 0      |  |  |

| 1   | 1   | 1      |  |  |

### **Digital Logic families**

Diode Transistor Logic : 1959

Resistor Transistor Logic : 1961

> Transistor Transistor Logic : 1963 Discrete IC

Emitter-coupled logic : First Microprocessor 360

> CMOS:

> 1974 Intel 4004 which had 2000 Transistors

Channel Length of 10 µm.

**2020 AMB 7 nm has billions of Transistors Channel Length of 7 nm.**

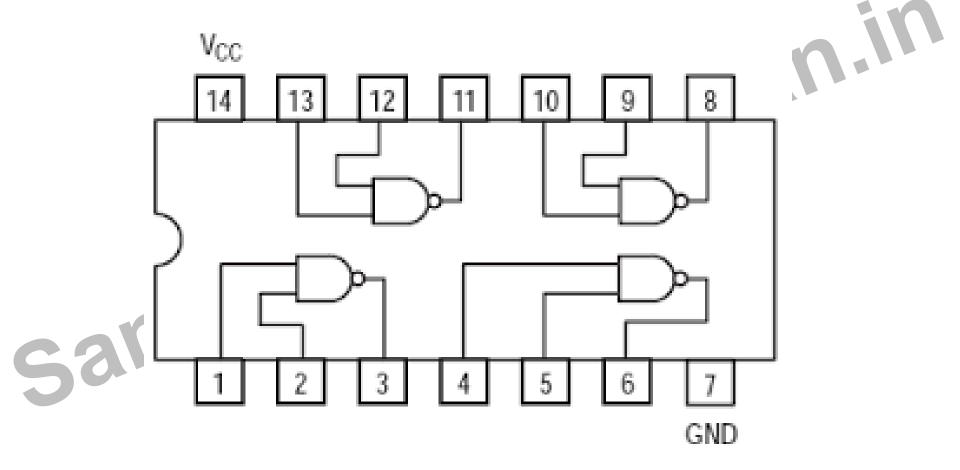

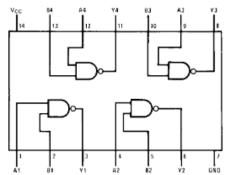

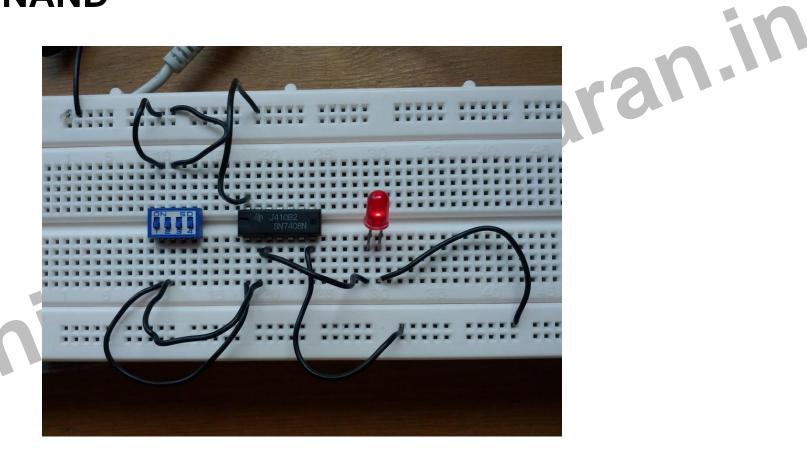

### 7400 Quad 2 Input NAND

### **7400 NAND**

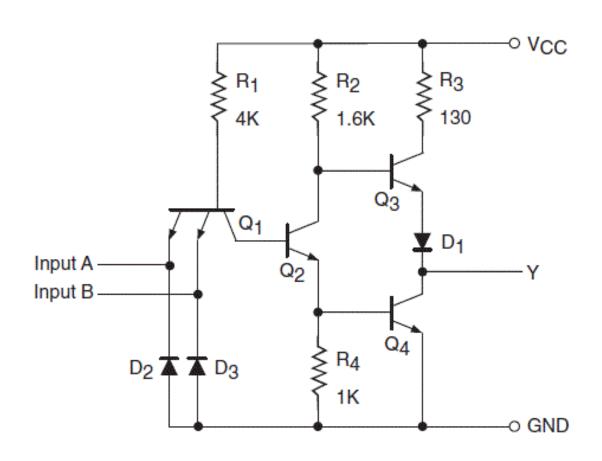

### **TTL Gate**

**TTL 2 input NAND Gate**

### 7400 NAND DATA SHEET

September 1986 Revised July 2001

### **DM7400**

### Quad 2-Input NAND Gates

### **General Description**

This device contains four independent gates each of which performs the logic NAND function.

### **Ordering Code:**

|                                                                               | Order Number | Package Number                                                         | Package Description                                                          |

|-------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------|------------------------------------------------------------------------------|

|                                                                               | DM7400M      | M14A                                                                   | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| DM7400N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 |              | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide |                                                                              |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

### **Connection Diagram**

### **Function Table**

| Inputs |   | Output |

|--------|---|--------|

| A B    |   | Y      |

| L      | L | Н      |

| L      | н | н      |

| н      | L | н      |

| н      | н | L      |

$Y = \overline{AB}$

H = HIGH Logic Level L = LOW Logic Level

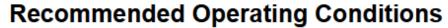

### 7400 NAND DATA SHEET

| Symbol          | Parameter                      | Min  | Nom | Max  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage       | 2    |     |      | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |      |     | 0.8  | V     |

| Гон             | HIGH Level Output Current      |      |     | -0.4 | mA    |

| l <sub>OL</sub> | LOW Level Output Current       |      |     | 16   | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0    |     | 70   | °C    |

### **7400 NAND**

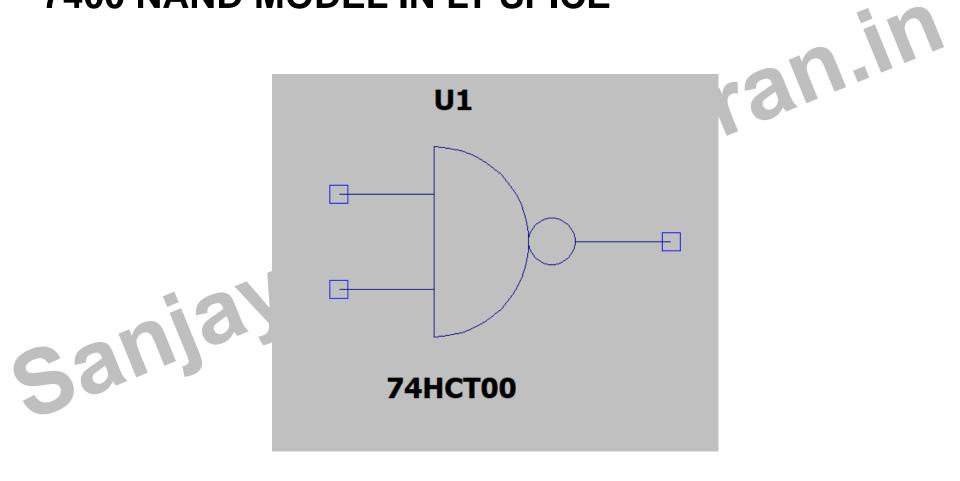

### 7400 NAND MODEL IN LT SPICE

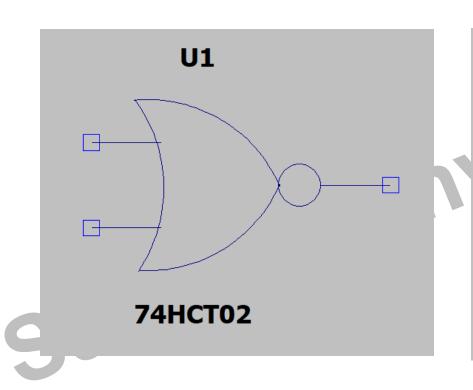

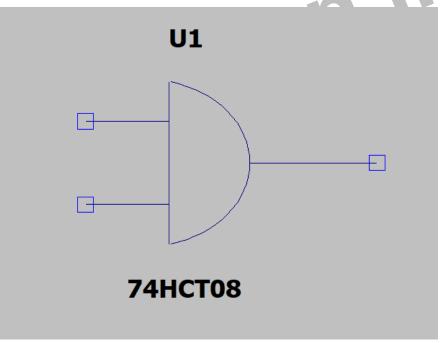

### **MODELS IN LT SPICE**

### **MODELS IN LT SPICE**

### **Installing 74XX SPICE Model in LT SPICE**

- 1. Download file "LT\_SPICE\_Installation\_Files.zip" from <a href="https://sanjayvidhyadharan.in/Downloads">https://sanjayvidhyadharan.in/Downloads</a>

- 2. Unzip the file. It contains the following files/folder

- (a) Itspiceiv.exe

- (b) 74hct.lib

- (c) Sym (Folder)

- (d) Example1.asc

- 3. Run the Itspiceiv.exe file to install LTSPICE on to your PC/laptop.

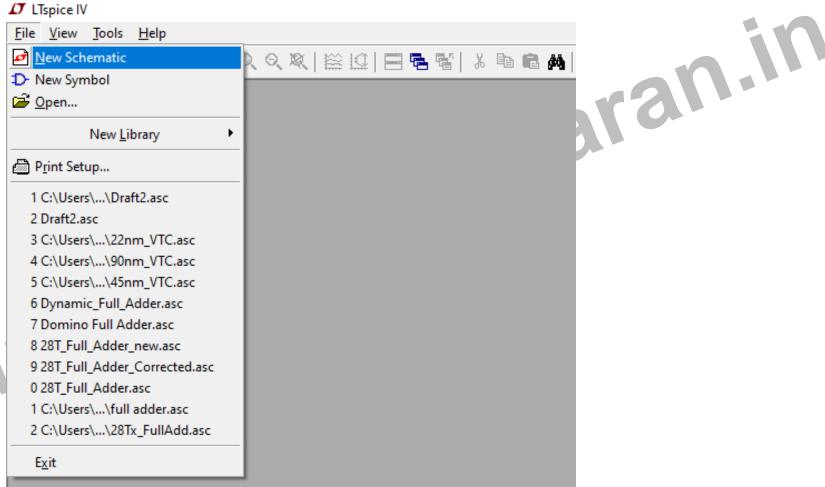

4. Open LtSpice. And open a New Schematic from File tab.

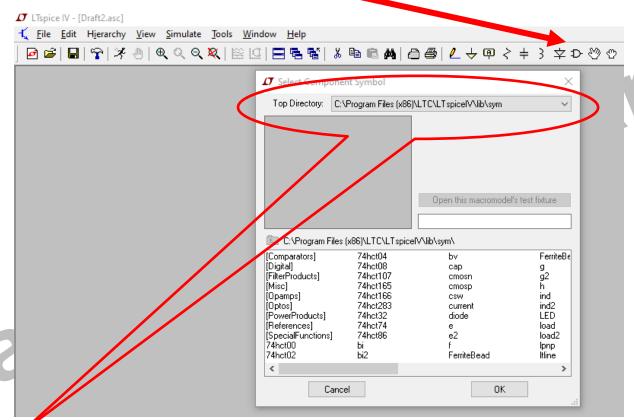

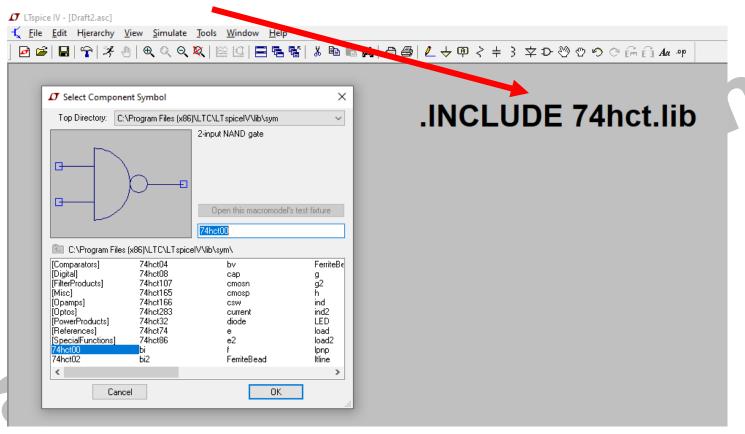

5. Click on the Component tab (looks like a AND gate) on the new schematic window

6. Note the path of the LT SPICE lib file

7. Copy paste 74ct.lib file in the folder

C:\Program Files\LTC\LTspiceIV\lib\sub

aran.ii 8. Copy paste all the files contained in downloaded folder "Sym" into

C:\Program Files\LTC\LTspiceIV\lib\sym

sansi

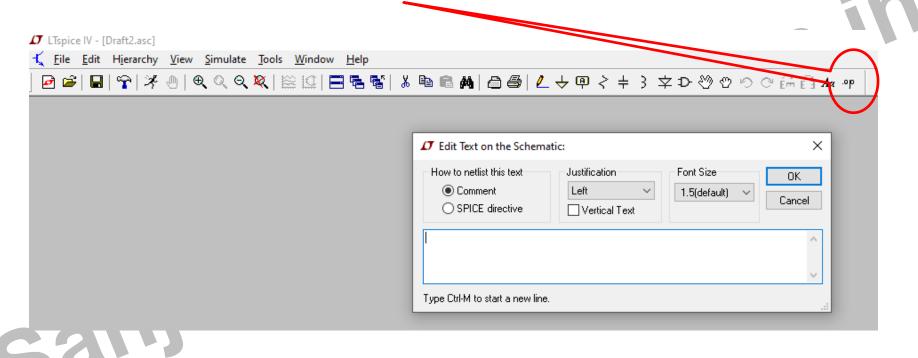

9. Click on the SPICE Directive tab as shown below:-

9. Click on the SPICE Directive tab as shown below:-

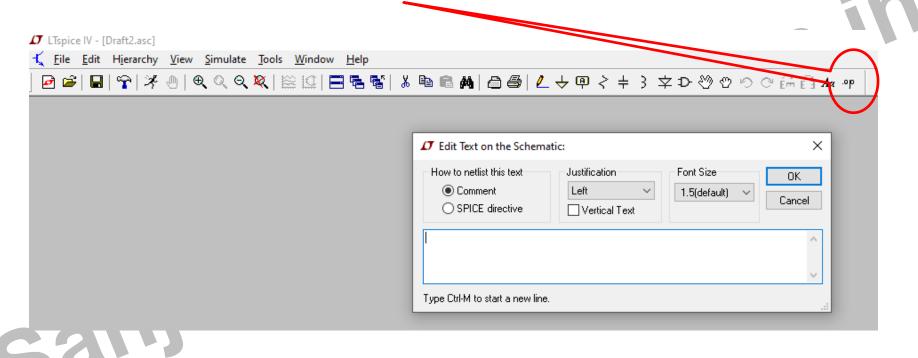

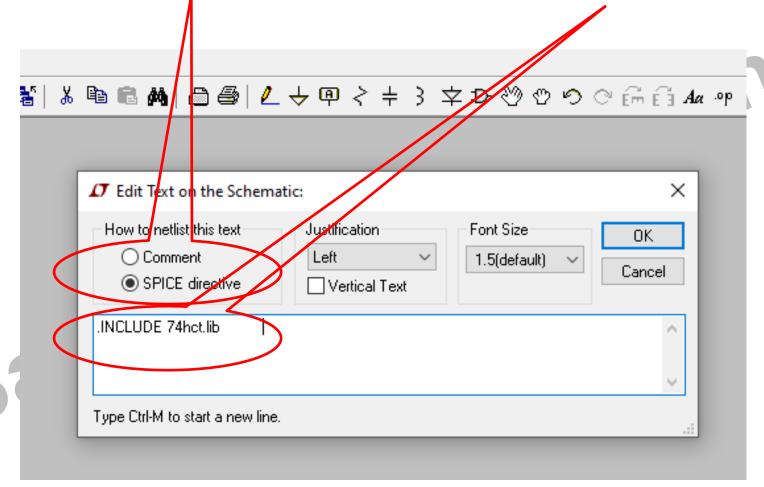

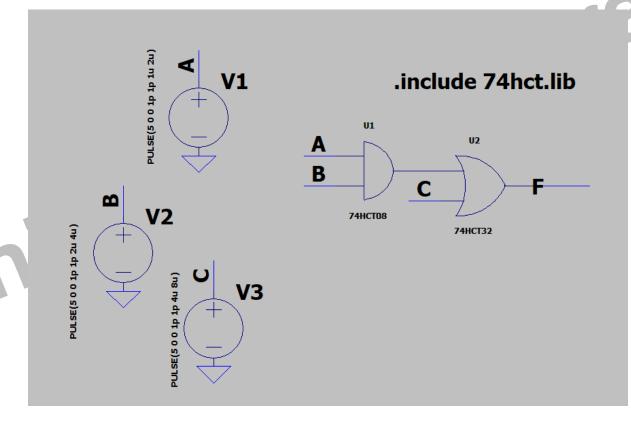

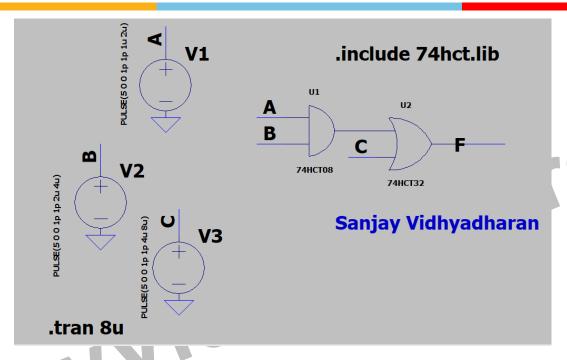

10. Select SPICE Directive and Type .INCLUDE 74hct.lib

10. Place the SPICE directive on the schematic

11. Select the component tab and you will be able to see the 74XX series gates.

1

### Sample Run

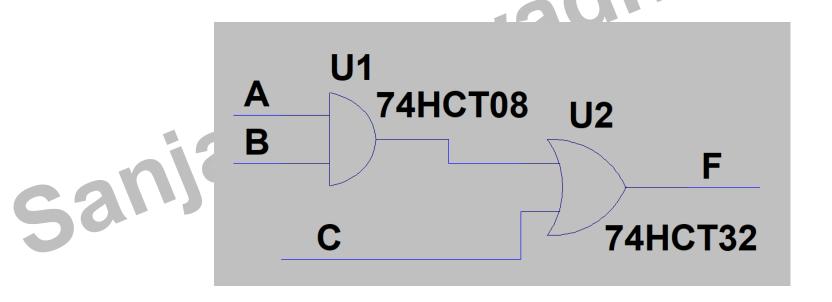

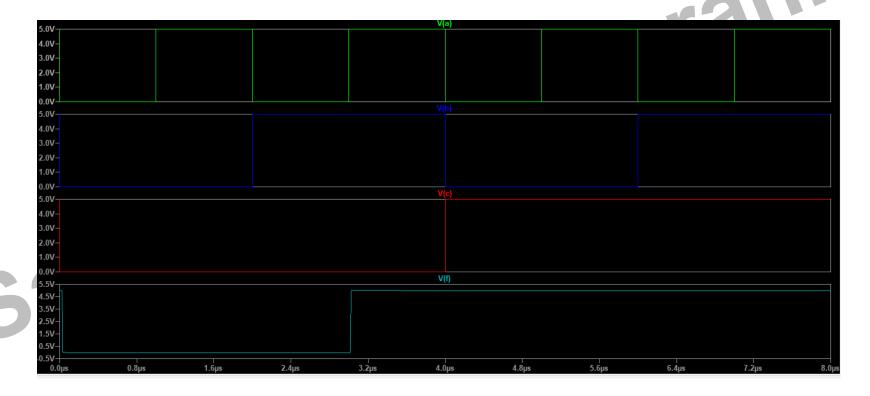

F= AB+C (Implementation with AND & OR Gates)

1

### Sample Run

F=AB+C (Implementation with AND & OR Gates)

ELECTRICAL

**ELECTRONICS**

1

### Sample Run

F=AB+C (Implementation with AND & OR Gates)

**ELECTRICAL**

1

### Sample Run

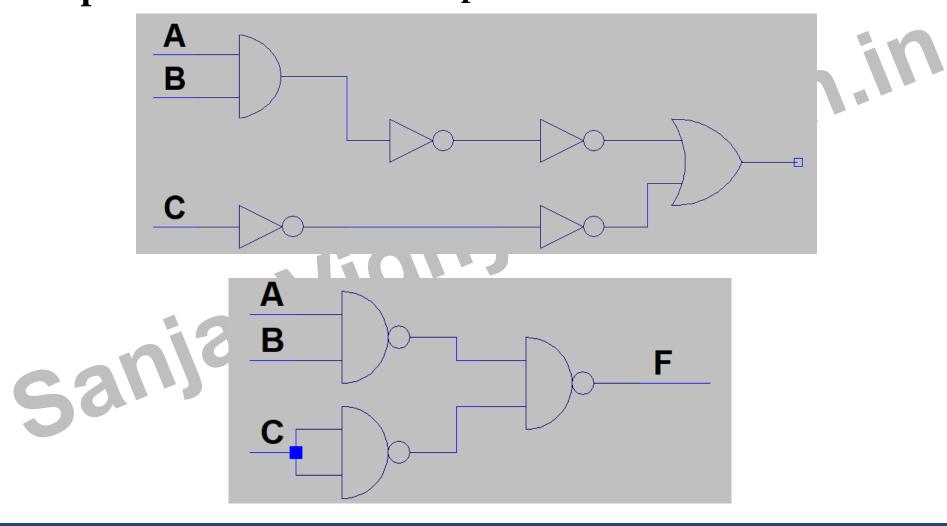

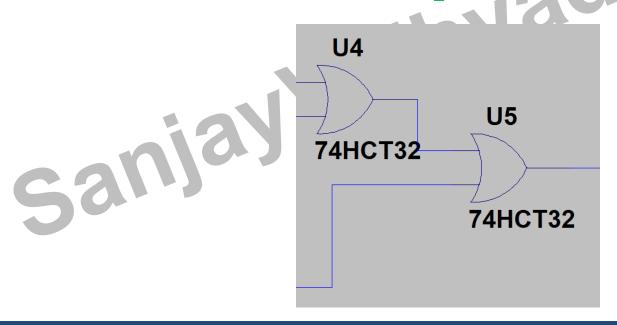

F= AB+C (Implementation with NAND Gates)

1

### **Sample Run** F=AB+C Implementation with NAND Gates

1

### **Problem 1: Implement the Majority Circuit**

| Α | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

$$F = AB + BC + CA + ABC$$

$$F = AB + BC + CA$$

### Problem 1: Implement the Majority Circuit

Run1: Implement F with AND & OR gates

Check output for all combinations of Input

F = AB + BC + CA

Hint: Use Three 2 i/p AND & Two 2 i/p OR GATE

**Problem 1: Implement the Majority Circuit**

**Run1: Implement F with NAND gates**

F = AB + BC + CA

Check output for all combinations of Input

Hint: Use Three 2 i/p NAND & One 3 i/p NAND GATE

### **Submission**

Upload LTSPICE file to the folder given by your Lab instructor

- 1. With your name in the schematic as shown above

- 2. LT Spice File name indicating your Roll number

Eg. 2019H1240056H.asc

## Demonstration

8/24/2021

Sanjay