2023

| Sl No | Authors | Title | Journal/Book Chapter |

|---|---|---|---|

| 22 | Abhay S. Vidhyadharan, Gangavarapu Anuhya, Shivangi Shukla Sanjay Vidhyadharan , | Fast and Low-Power CMOS and CNFET based Hysteresis Voltage Comparator | IETE Journal of Research DOI: 10.1080/03772063.2023.2165176 |

2022

| Sl No | Authors | Title | Journal/Book Chapter |

|---|---|---|---|

| 21 | Abhay S. Vidhyadharan,Aiswarya Satheesh, Kilari Pragnaa Sanjay Vidhyadharan , | High-Speed and Area-Efficient CMOS and CNFET-Based Level-Shifters | Springer Circuits, Systems, and Signal Processing https://doi.org/10.1007/s11277-021-09135-2 |

| 20 | Abhay S. Vidhyadharan, Sanjay Vidhyadharan , | CNFET Based Ultra-Low-Power Schmitt Trigger SRAM for Internet of Things (IoT) Applications | Springer Wireless Personal Communications Jan 2022. Vol. 123, pp. 357–373 |

2021

| Sl No | Authors | Title | Journal/Book Chapter |

|---|---|---|---|

| 19 | R. Yadav, S. S. Dan, S. Vidhyadharan , and S. Hariprasad | Suppression of Ambipolar Behavior and Simultaneous Improvement in RF Performance of Gate-Overlap Tunnel Field Effect Transistor | Springer Silicon. Jul 2020. Vol. 13, pp. 1185–1197, Jul 2021 |

| 18 | S. Vidhyadharan and S. S. Dan | An Efficient Ultra-Low Power and Superior Performance Design of Ternary Half Adder Using CNFET and Gate-Overlap TFET Devices | IEEE Transactions on Nano Technology. Vol. 20, pp. 365-376, 2021 |

| 17 | Abhay SV andS. Vidhyadharan | An ultra-low-power CNFET based dual VDD ternary dynamic Half Adder | Microelectronics Journal, Volume 107, 2021 |

| 16 | Abhay SV , Kasturi Bha andS. Vidhyadharan | CNFET-Based Ultra-Low-Power Dual-VDD Ternary Half Adder | Springer Circuits, Systems, & Signal Processing. Vol.40 pp. 4089-4105, Aug 2021 |

| 15 | Abhay SV andS. Vidhyadharan | An Ultra-Low-Power CNFET based Improved Schmitt Trigger Design for VLSI Sensor Applications | International Journal of Numerical Modelling: Electronic Networks, Devices and Fields. Volume 32, Issue 4, July/August 2021 |

| 14 | Abhay SV andS. Vidhyadharan | Improved Hetero-Junction TFET based Schmitt Trigger Designs for Low-Voltage VLSI Application | World Journal of Electronics , 2021 DOI: 10.1108/WJE-08-2020-0367. |

| 13 | Abhay SV andS. Vidhyadharan | Mux Based Ultra-Low-Power Ternary Adders and Multiplier implemented with CNFET and 45 nm MOSFETs | Taylor and Francis Journal of Electronics , 2021, DOI: 10.1080/00207217.2021.1908616, |

| 12 | Abhay SV andS. Vidhyadharan | A Novel Ultra-Low-Power CNFET and 45 nm CMOS based Ternary SRAM | Microelectronics Journal, Volume 111, 2021. |

| 11 | Abhay SV andS. Vidhyadharan | Memristor -CMOS Hybrid Ultra-Low-Power High-SpeedMultivibrators | Springer Analog Integrated Circuits and Signal Processing. 2021, DOI: 10.1 007/s10470-021-01856-5. |

| 10 | Sanjay Vidhyadharan and SS Dan | Gate-Overlap Tunnel Field-Effect Transistors (GOTFETs) for Ultra-Low-Voltage and Ultra-Low-Power VLSI Applications | Microelectronics and Signal Processing Chapter 8 pages 137-164 CRC Press June 7, 2021 |

2020

| Sl No | Authors | Title | Journal/Book Chapter |

|---|---|---|---|

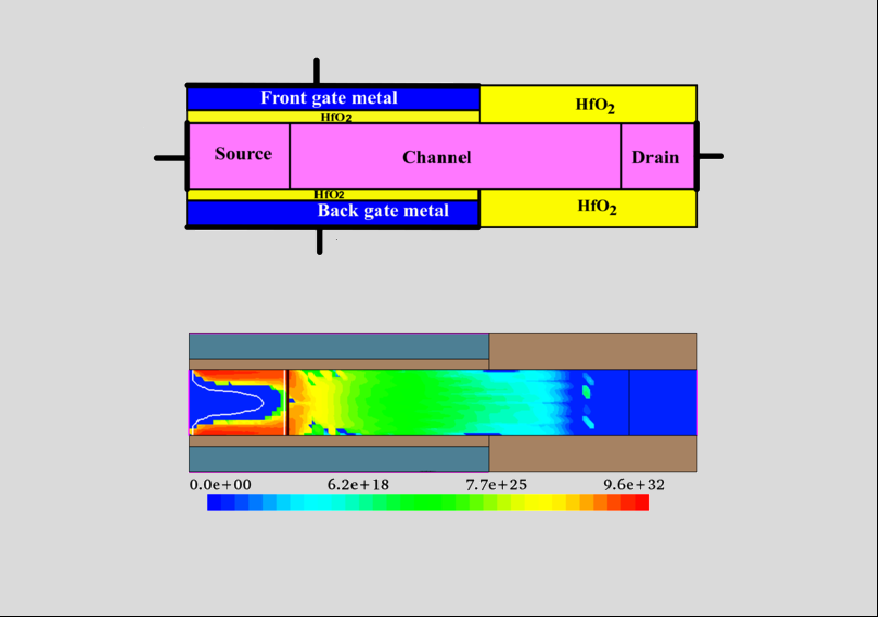

| 9 | S. Vidhyadharan , R. Yadav, S. Hariprasad, and S. S. Dan | An advanced adiabatic logic using Gate Overlap Tunnel FET (GOTFET) devices for ultra-low power VLSI sensor applications | Springer Analog Integrated Circuits and Signal Processing, 2020, Vol. 102, pp-111-123. |

| 8 | S. Vidhyadharan S. S. Dan, R.Yadav, and S. Hariprasad | A Novel Ultra-Low Power Gate-Overlap Tunnel FET (GOTFET) Dynamic Adder | Taylor & Francis Journal of Electronics. Vol. 107, Issue 10. 2020 |

| 7 | S. Vidhyadharan , S. S. Dan , Abhay S,V, R. Yadav and S. Hariprasad | Novel Gate-Overlap Tunnel FET based Innovative Ultra-Low Power Ternary Flash ADC | Integration: The VLSI Journal, Vol.73C, pp101-113 , 2020 |

| 6 | R. Yadav, S. S. Dan, S. Vidhyadharan , and S. Hariprasad | An innovative multi-threshold gate-overlap tunnel fet (GOTFET) devices for superior ultra-low power digital, ternary and analog circuits at 45 nm technology node.for low power VLSI applications | Springer Journal of Computational Electronics. Vol 19, pp-291-303, 2020 |

| 5 | S. Vidhyadharan , R. Yadav, S. Hariprasad, and S. S. Dan | An Innovative Ultra-Low Voltage GOTFET based Regenerative-Latch Schmitt Trigger | Microelectronics Journal, Volume 104, October 2020 |

| 4 | Abhay SV andS. Vidhyadharan | TiO2−x–TiO2 Memristor Applications for Programmable Analog VLSI Circuits at 45 nm CMOS Technology Node | Springer Transactions on Electrical and Electronic Materials, October 2020. |

2019

| Sl No | Authors | Title | Journal/Book Chapter |

|---|---|---|---|

| 3 | S. Vidhyadharan, R. Yadav, G. Akhilesh, V. Gupta, A. Ravi, and S. S. Dan | Benchmarking the Performance of Optimized TFET-Based Circuits with the Standard 45 nm CMOS Technology Using Device & Circuit Co-simulation Methodology | The Physics of Semiconductor Devices, R. K. Sharma and D. Rawal, Eds. Springer International Publishing, 2019, Vol. 215, Chap 96, pp. 619-628. |

| 2 | R. Yadav, S. Vidhyadharan, G. Akhilesh, V. Gupta, A. Ravi, and S. S. Dan | Optimization of the Tunnel FET Device Structure for Achieving Circuit Performance Better Than the Current Standard 45 nm CMOS Technology | The Physics of Semiconductor Devices, R.K. Sharma and D. Rawal, Eds. Springer International Publishing, 2019, Vol. 215, Chap 95, pp. 611-618. |

| 1 | S. Vidhyadharan , R. Yadav, S. Hariprasad, and S. S. Dan | A Nanoscale Gate-Overlap Tunnel FET (GOTFET) Based Improved Double Tail Dynamic Comparator for Ultra-Low-Power VLSI Applications | Springer Analog Integrated Circuits and Signal Processing, Vol.101, pp-109-117, 2019. |

Conferences

- S. Vidhyadharan, R. Yadav, G. Akhilesh, V. Gupta, A. Ravi, and S. S. Dan, "Part-II:Benchmarking the Performance of Optimized TFET-Based Circuits with the Standard45 nm CMOS Technology Using Device & Circuit Co-simulation Methodology," XIXth International Workshop on Physics of Semiconductor Devices (IWPSD 2017), Delhi.

- R. Yadav, S. Vidhyadharan, G.Akhilesh, V.Gupta, A.Ravi, and S.S.Dan, Part-I: Optimization of the Tunnel FET Device Structure for Achieving Circuit Performance Better Than the Current Standard 45 nm CMOS Technology," in XIXth International Workshop

on Physics of Semiconductor Devices (IWPSD 2017), Delhi. - S. Vidhyadharan, R. Ramakant, A. S. Vidhyadharan, A. K. Shyam, M. P. Hirpara, and S. S. Dan, An Efficient Design Approach for Implementation of 2 Bit Ternary Flash ADC Using Optimized Complementary TFET Devices," 32nd International Conference on VLSI

Design and 18th International Conference on Embedded Systems (VLSID), January, 2019, Delhi - R. Yadav, S. Vidhyadharan, A. K. Shyam, M. P. Hirpara, T. Chaudhary, and S. S.Dan, "Novel Low and High Threshold TFET Based NTI and PTI Cells Benchmarked with Standard 45 nm CMOS Technology for Ternary Logic Applications," 32nd International

Conference on VLSI Design and 18th International Conference on Embedded Systems (VLSID), January, 2019, Delhi. - Simhadri Hariprasad, S. S. Dan, Ramakant Yadav, S. Vidhyadharan, "Innovative Strained SiGe Nanoscale Low & High VT Gate Overlap TFET Structures at 45 nm Standard CMOS Technology for Ultra-Low Power Yet High Performance Analog, Digital and Ternary VLSI Applications", XXth International Workshop on Physics of Semiconductor Devices (IWPSD 2019), Kolkata.

Category : About Me

Date : 01 Sep 2021