#### **Digital Design**

#### Lecture 11: Combinational Logic and Arithmetic Circuits

achleve

097

Innovate

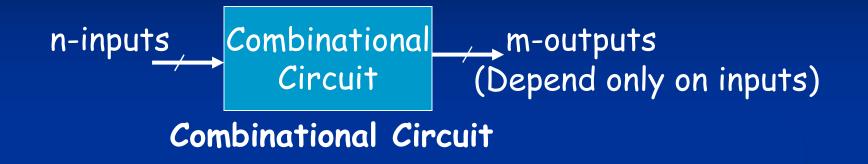

## **Combinational Circuits**

- A combinational circuit consists of logic gates whose outputs, at <u>any time</u>, are determined by combining the values of the inputs.

- For n input variables, there are 2<sup>n</sup> possible binary input combinations.

For each binary combination of the

- input variables, there is one possible output.

## **Combinational Circuits (cont.)**

- Hence, a combinational circuit can be described by:

- 1. A truth table that lists the output values for each combination of the input variables, or

- 2. *m* Boolean functions, one for each output variable.

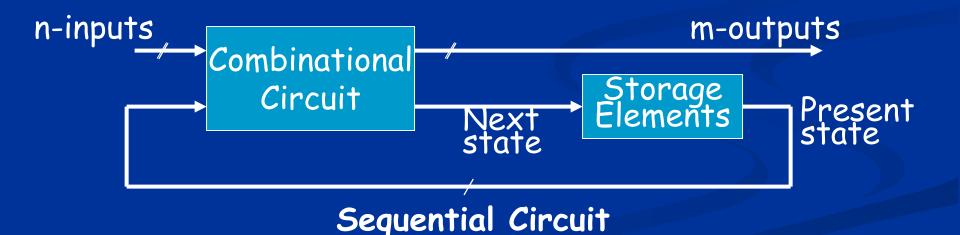

#### Combinational vs. Sequential Circuits

- Combinational circuits are <u>memory-less</u>. Thus, the output value depends ONLY on the current input values.

- Sequential circuits consist of combinational logic as well as memory elements (used to store certain circuit states). Outputs depend on BOTH current input values and previous input values (kept in the storage elements).

#### Combinational vs. Sequential Circuits

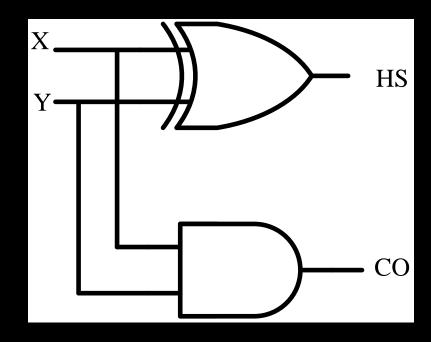

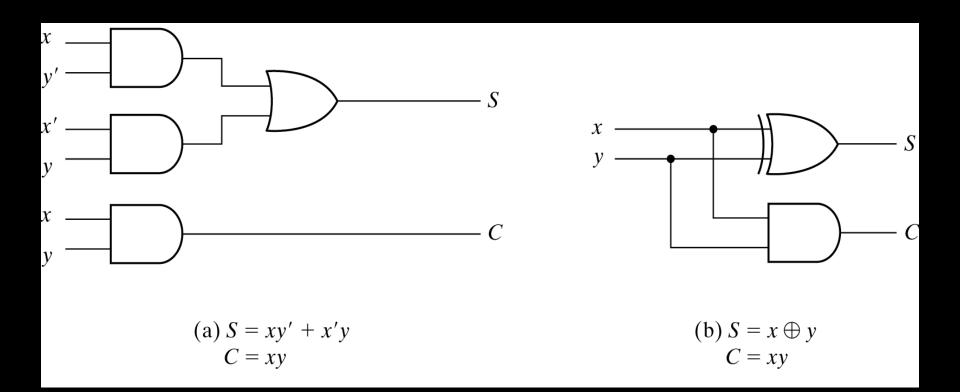

## Half Adder

#### Input is limited to 2 bits HS = X xor Y $= X \cdot Y' + X' \cdot Y$ $CO = X \cdot Y$

#### Time for the Half Adder?

- 1 gate delay

- A gate delay of an xor for the half sum

- A gate delay of an AND gate for the carry out

#### Half Adder

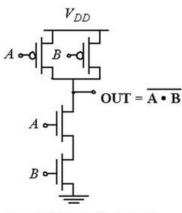

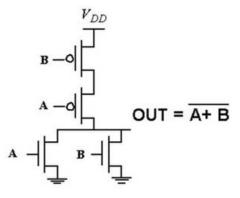

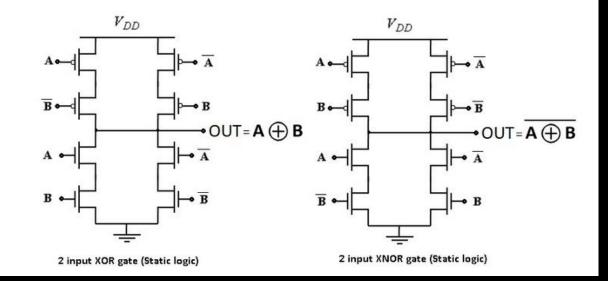

#### NAND vs. XOR

2 input NAND gate (Static Logic)

2 input NOR gate (Static Logic)

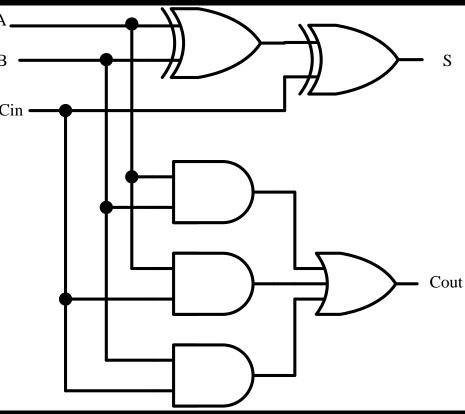

#### Input is now X Y and the Carry in. So have

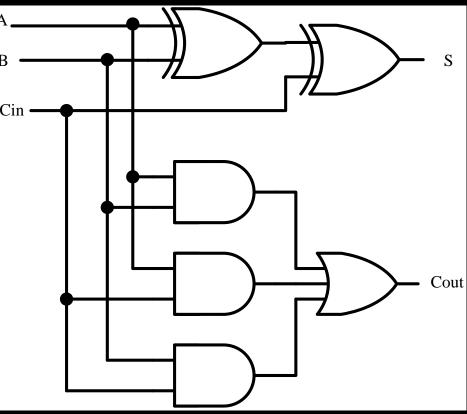

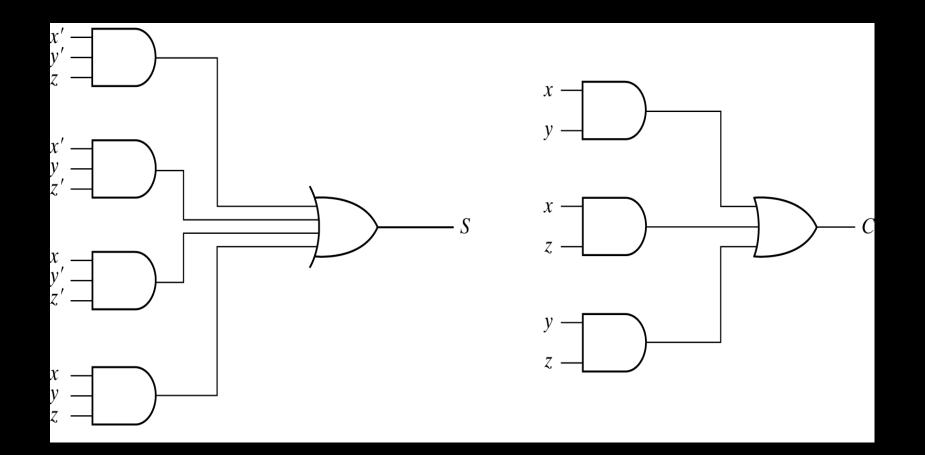

#### S =X•Y'•Cin'+X'•Y•Cin'+X'•Y'•Cin+X•Y•Cin = X xor Y xor Cin Cout = X•Y + X•Cin + Y•Cin

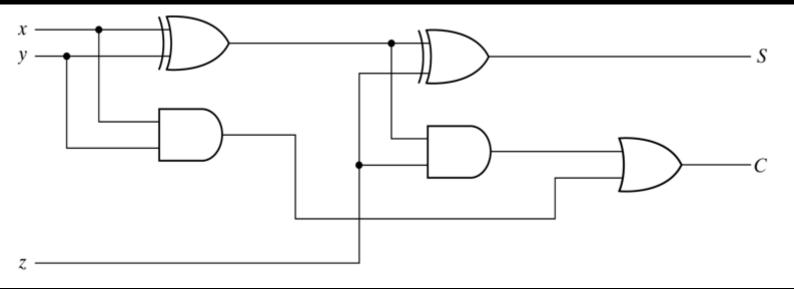

Two level logic **Output delay** Cin A, B Cin  $\rightarrow$  Sum Delay through 2 xor gates  $t_s = 2 t_{xor}$ A, B Cin  $\rightarrow$  Cout Delay through an AND gate and an OR gate  $t_{Cout} = t_{and} + t_{or}$

Two level logic **Output delay** Cin A, B Cin  $\rightarrow$  Sum Delay through 2 xor gates  $t_s = 2 t_{xor}$ A, B Cin  $\rightarrow$  Cout Delay through an AND gate and an OR gate  $t_{Cout} = t_{and} + t_{or}$

#### Delay= 2 Gate Delay ?

10/1/2020

Full-adder can also implemented with two half adders and one OR gate.

$$S = z \bigoplus (x \bigoplus y)$$

= z'(xy' + x'y) + z(xy' + x'y)'

= xy'z' + x'yz' + xyz + x'y'z

$$C = z(xy' + x'y) + xy = xy'z + x'yz + xy$$

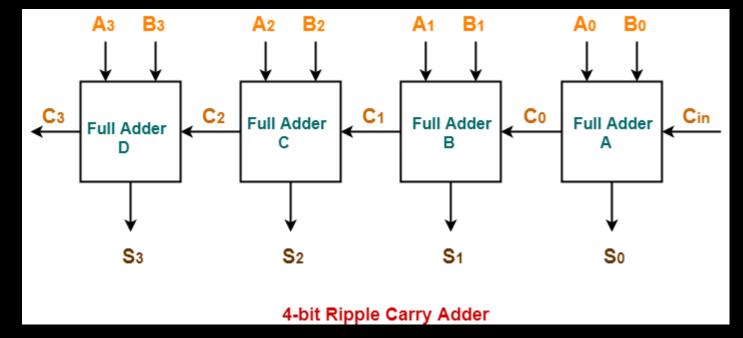

# **Ripple Carry Adder**

This is called Ripple Carry Adder ,because of the construction with full adders are connected in cascade.

Delay= 4 X Full Adder Delay

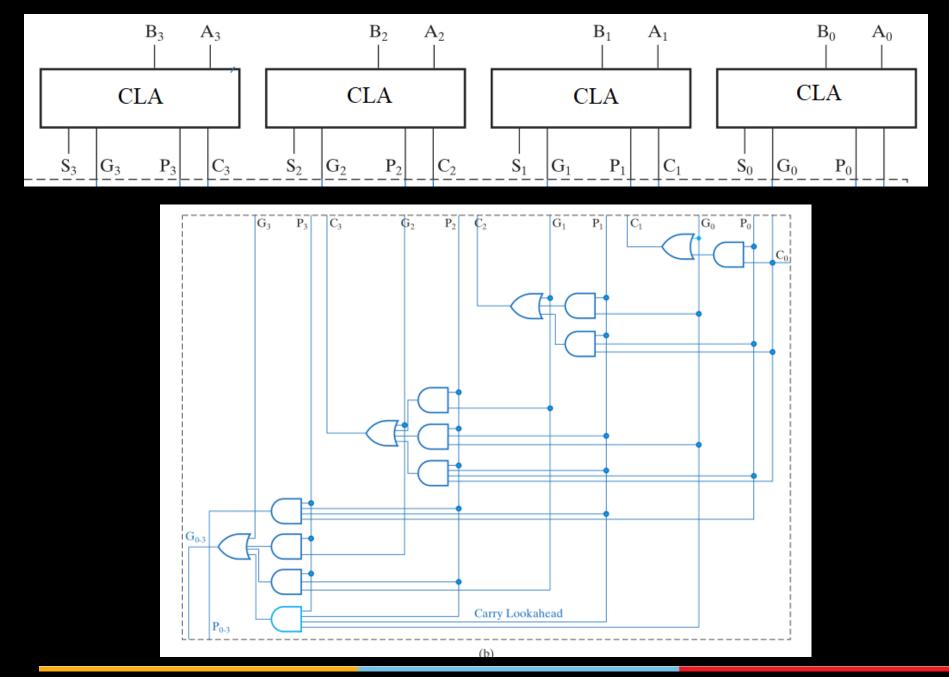

## **Carry Look-Ahead Adder**

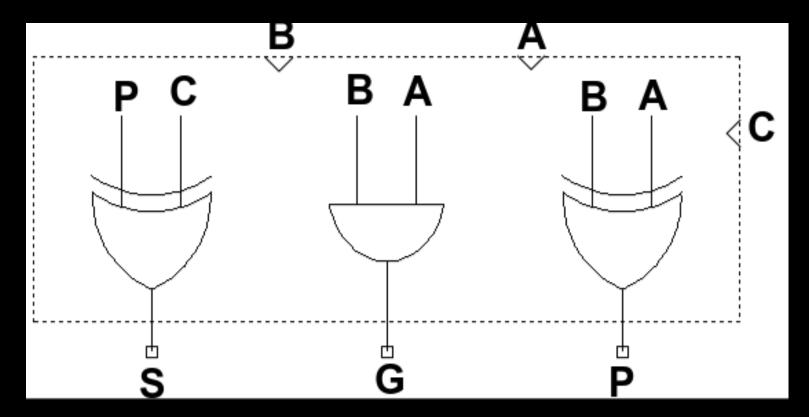

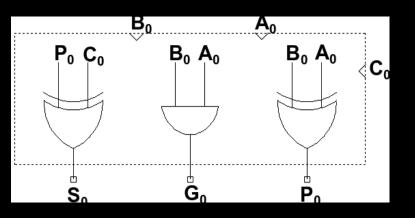

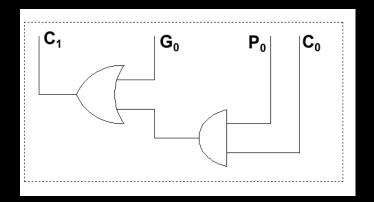

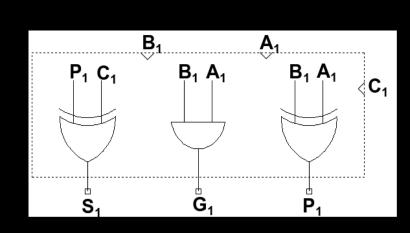

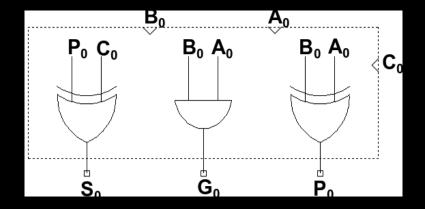

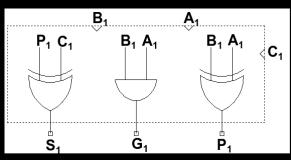

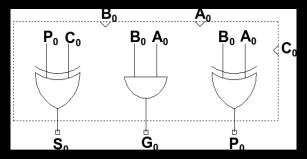

#### 1-bit CLA

## **Carry Look-Ahead Adder**

#### CLA

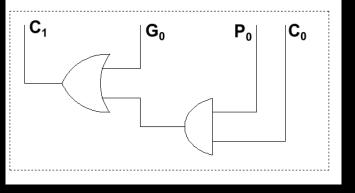

CLLB

$\mathbf{C}_{1} = \mathbf{G}_{0} + \mathbf{P}_{0}\mathbf{C}_{0}$

# $C_{2}=G_{1}+P_{1}C_{1}$ $C_{2}=G_{1}+P_{1}.(G_{0}+P_{0}C_{0})$ $C_{2}=G_{1}+P_{1}G_{0}+P_{1}P_{0}C_{0}$

#### $\mathbf{C}_1 = \mathbf{G}_0 + \mathbf{P}_0 \mathbf{C}_0$

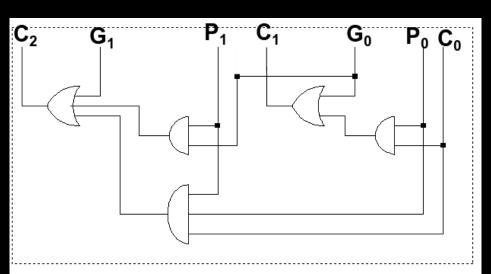

## **Carry Look-Ahead Adder**

#### $C_2 = G_1 + P_1 G_0 + P_1 P_0 C_0$

#### $C_1 = G_0 + P_0 C_0$

## **Carry Look-Ahead Adder**

#### $C_4 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 C_0$

## $C_3 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$

#### $\mathbf{C}_2 = \mathbf{G}_1 + \mathbf{P}_1 \mathbf{G}_0 + \mathbf{P}_1 \mathbf{P}_0 \mathbf{C}_0$

#### $\mathbf{C}_1 = \mathbf{G}_0 + \mathbf{P}_0 \mathbf{C}_0$

**Carry Look-Ahead Adder**