## Microprocessors and Interfaces: 2021-22 Lecture 29 : 8253/8254 Timer Part:1

## By Dr. Sanjay Vidhyadharan

## **Features of 8253/8254**

- consists 8254 three independent • The of 16-bit programmable counters (timers).

- Each counter is capable of counting in binary or binarycoded decimal (BCD).

- Maximum allowable input frequency to any counter is 10 MHz

- the Useful where microprocessor must control real-time events. Ex: real-time clocks, event counters, and motor speed/direction control.

8253 Its operating frequency is 0 - 2.6 MHz Its operating frequency is 0 - 10 MHz It uses N-MOS technology

Read-Back command is not available 4/15/2021

8254

It uses H-MOS technology

Read-Back command is available

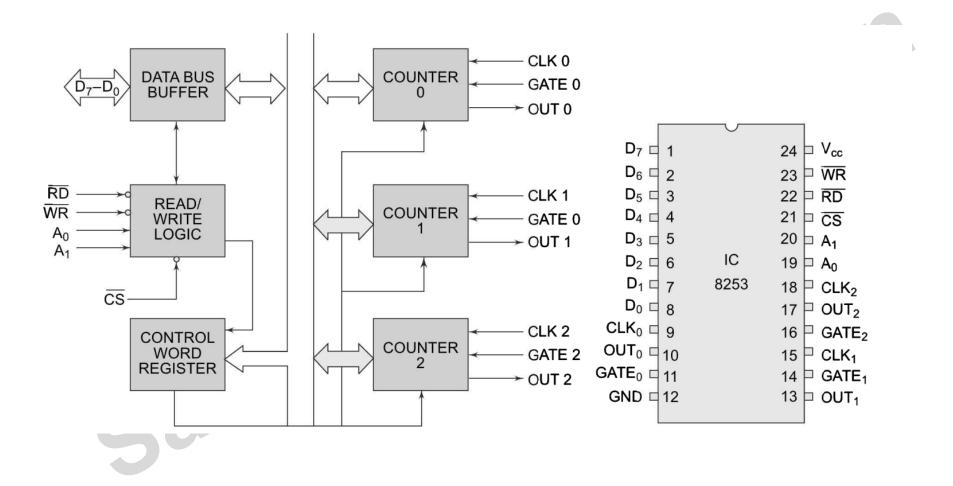

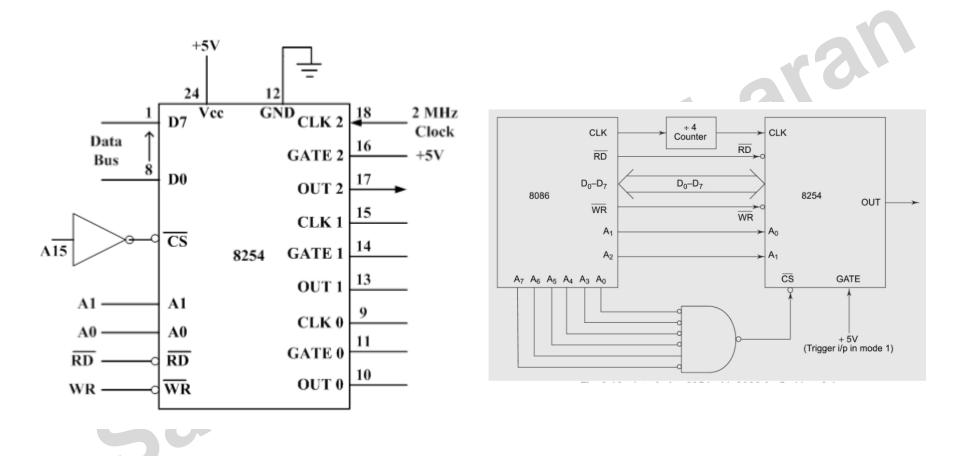

# Pin diagram of 8253/8254

## **Features of 8253/8254**

- Each timer contains:

- a CLK input which provides the basic operating frequency to the timer

- a Gate input pin which controls the timer in some modes.

- an output (OUT) connection to obtain the output of the timer.

## **Memory mapping**

| CS' | <b>A</b> <sub>1</sub> | A <sub>o</sub> | Selected               |

|-----|-----------------------|----------------|------------------------|

| 0   | 0                     | 0              | Counter 0              |

| 0   | 0                     | 1              | Counter 1              |

| 0   | 1                     | 0              | Counter 2              |

| 0   | 1                     | 1              | Control Register       |

| 1   | X                     | X              | 8253/8254 Not Selected |

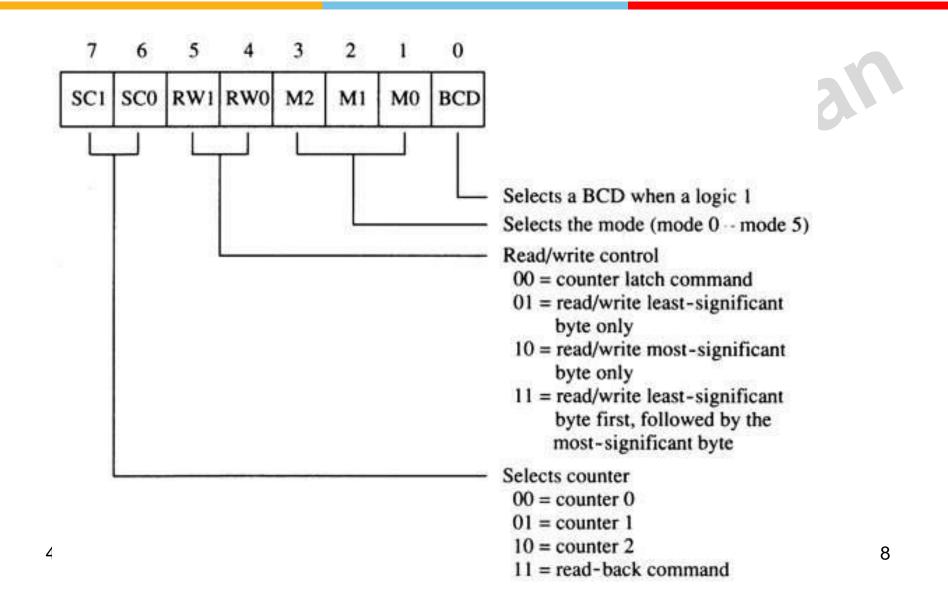

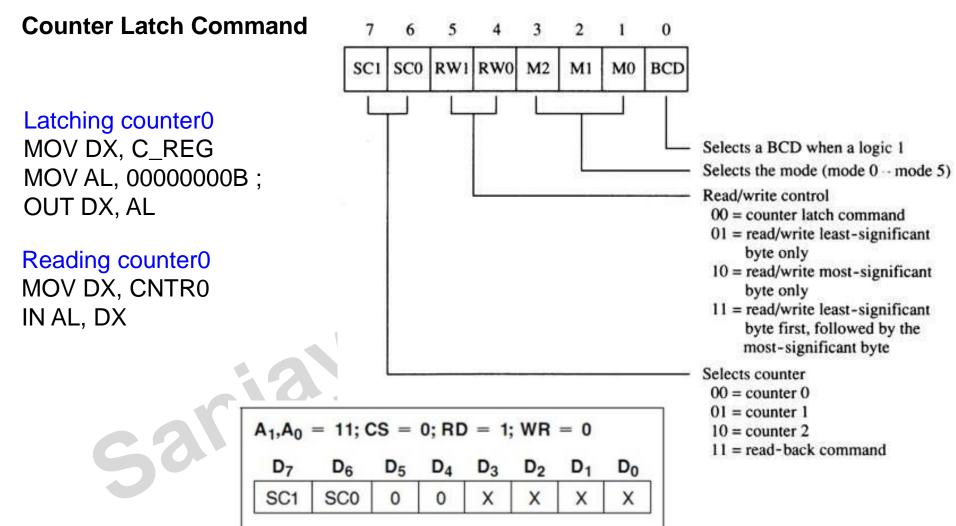

## **Control word Format**

#### 4/15/2021

## **Programming the Counters**

Before you can use.....

- 1. Initialize the mode of every counter planned to be used

- This is done by sending individual command words for every counter

- 3. These CWs are sent at  $A_1A_0 = 11$

- 4. Send counts to the counters

- 5. This is done at counter addresses

- 6. Enable gates for counting to start

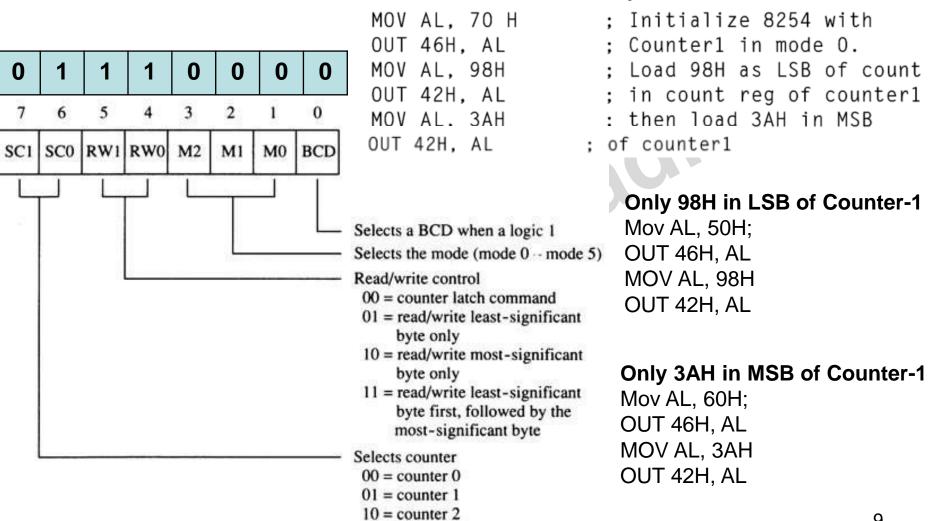

## **Control word Format**

## **Control word Format**

Counter-1 Mode 0, Binary, N= 3A98H

11 = read-back command

# **Reading the Counters**

#### Simple Read Operation

Counter selected with the A1, A0 inputs, the CLK input of the selected Counter must be inhibited by using either the GATE input or external logic. Otherwise, the count may be in the process of changing when it is read, giving an undefined result. Two I/O read operation are performed by the MPU

1. The first I/O operation reads the low order byte.

2. The second I/O operation reads high order byte.

#### **Counter Latch Command**

This allows reading the contents of the Counters "on the fly" without affecting counting in progress.

The selected Counter's output latch (OL) latches the count at the time the Counter Latch Command is received. This count is held in the latch until it is read by the CPU (or until the Counter is reprogrammed). The count is then unlatched automatically and the OL returns to "following" the counting element (CE).

# **Reading the Counters**

4/15/2021

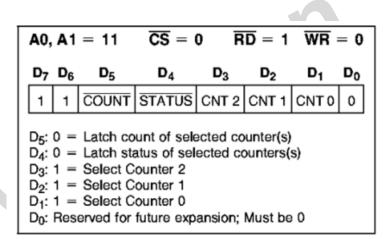

## **Read-Back Command**

This command is used to read several counters at a time. It eliminates the need of writing separate counter-latch commands for different counters. It allows the user to check the count value, programmed Mode, and current states of the OUT pin and Null Count flag of the selected counter/ counters. The read back command is written to the Control Word Register. is reprogrammed). The counter is automatically unlatched when read, but other counters remain latched until they are read.

| A0,                                                                          | <b>A</b> 1               | = 11                                          | $\overline{\text{CS}} = 0$ | 0 R            | <u>D</u> = 1   | WR             | = 0            |

|------------------------------------------------------------------------------|--------------------------|-----------------------------------------------|----------------------------|----------------|----------------|----------------|----------------|

| D7                                                                           | D <sub>6</sub>           | <b>D</b> 5                                    | $D_4$                      | $\mathbf{D}_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

| 1                                                                            | 1                        | COUNT                                         | STATUS                     | CNT 2          | CNT 1          | CNT 0          | 0              |

| D <sub>4</sub> :<br>D <sub>3</sub> :<br>D <sub>2</sub> :<br>D <sub>1</sub> : | 0 =<br>1 =<br>1 =<br>1 = | Latch sta<br>Select C<br>Select C<br>Select C | ounter 1                   | ected co       | ounters(       | s)             |                |

4/15/2021

#### Figure Read-Back Command Format

## **Read-Back Command**

The read-back command may be used to latch multiple counter output latches (OL) by setting the COUNT bit D5 =0 and selecting the desired counter(s). A single read back command is functionally equivalent to several counter latch commands.

Each counter's latched count is held in the OL until it is read (or the counter is reprogrammed). The counter is automatically unlatched when read, but other counters remain latched until they are read.

The read-back command may also be used to latch status information of selected counter(s) by setting STATUS bit D4 = 0. Status must be latched to be read; status of a counter is accessed by a read from that counter.

The counter status format is shown in Figure below.

4/15/2021

| D7       | D <sub>6</sub>   | D <sub>5</sub> | D4   | D <sub>3</sub> | D <sub>2</sub> | <u> </u> | D <sub>0</sub> |  |

|----------|------------------|----------------|------|----------------|----------------|----------|----------------|--|

| Output   | Null<br>Count    | RW1            | RW0  | M2             | M1             |          | BCD            |  |

|          | 1 = OU<br>0 = OU |                |      |                | -              |          |                |  |

| <u> </u> | 1 = Nu<br>0 = Co |                | - TO | for r          | eadi           | ng       |                |  |

| D5-D0    | Counter          | progr          | amme | d ma           | de             |          | **             |  |

## **Read-Back Command**

Example:

Count and Status latched for counter 0 MOV DX, C\_REG MOV AL, 11000010B ; count latched for counter 0 OUT DX, AL

Reading the latched status for count 0 MOV DX, TRM0 IN AL, DX ; Reading Status MOV AH, AL Reading the latched count for counter 0 IN AL, DX ; Reading LSB of counter 0 MOV BL, AL IN AL, DX ; Reading MSB of counter 0 MOV BH, AL

#### Figure Read-Back Command Format

## **Control word Format**

| <b>D</b> <sub>7</sub> |     | <b>D</b> <sub>6</sub> | <b>D</b> <sub>5</sub> |                       | <b>D</b> <sub>4</sub> | D <sub>3</sub> |            | D <sub>2</sub>                         | D       | Do   |  |

|-----------------------|-----|-----------------------|-----------------------|-----------------------|-----------------------|----------------|------------|----------------------------------------|---------|------|--|

| SC1                   |     | SC0                   | RW                    | 1                     | RWO                   | M2             |            | M1                                     | мо      | BCD  |  |

| Selects Counter       |     |                       | Rea                   | Read/Write<br>Control |                       | Time           | Timer Mode |                                        |         |      |  |

|                       |     |                       | 000                   |                       |                       | Inte           | errupt on  | binary                                 |         |      |  |

| 00                    | Cou | unter 0               | 00                    | Late                  | h<br>nter             | 001            | h/v<br>sho | 0000 <sub>h</sub><br>FFFF <sub>h</sub> |         |      |  |

| 01                    | Cou | nter 1                | 01                    |                       | LSB                   | 010            | rat        | e generat                              | 1 - BCD |      |  |

| 10                    | Cou | nter 2                | 10                    | R/W                   | MSB                   | 011            | Squ        | Square wave generator                  |         | 0000 |  |

| 11                    |     | Read Back<br>Command  |                       | 11 R/W LSE<br>followe |                       | 1x0            | s/v        | s/w triggered strobe                   |         | 9999 |  |

|                       |     |                       | MSB                   |                       | 1x1                   | h/v            | v triggere |                                        |         |      |  |

|                       |     |                       |                       |                       |                       |                |            |                                        |         |      |  |

## Programming of 8253/8254

- Each counter is programmed by writing a control word, followed by the initial count.

- > The control word allows the programmer to select

- the counter,

- mode of operation, and

- type of operation (read/write).

- also selects either a binary or BCD count

# **Mode of Operation**

-Six modes (Mode 0–Mode 5) of operation are available to each of the 8254 counters

-each mode functions with the CLK input, the gate (G) control signal, and OUT signal.

sanić

## **Modes of counting**

- Interrupt on terminal count

- Programmable one shot

- Square wave generator

- Rate generator

san

- Software triggered strobe

- Hardware triggered strobe

| 130 |  |

|-----|--|

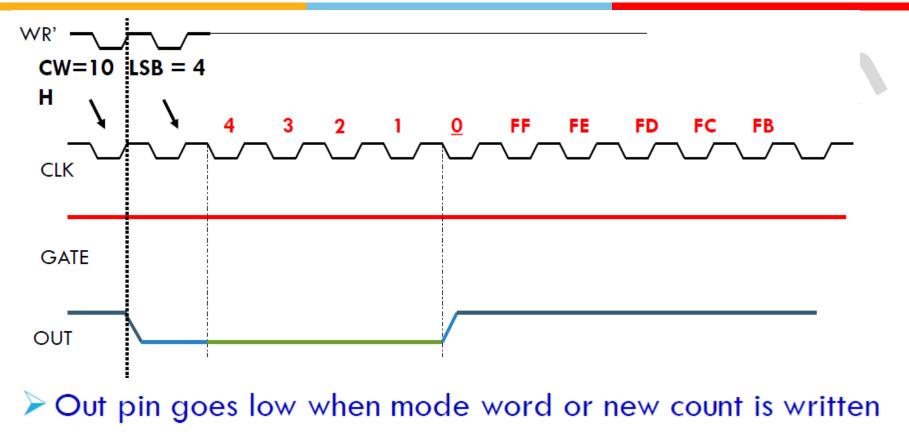

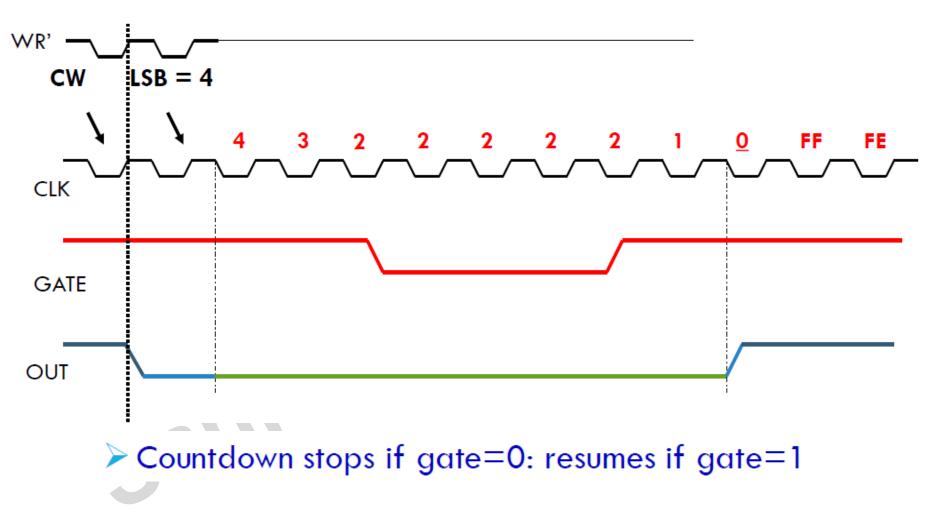

## **Mode 0 – Interrupt on Terminal count**

### Interrupt on terminal count (event counter)

- Out pin goes low when mode word or new count is written

- Now if clock is applied and gate=1, countdown begins

- Countdown stops if gate=0: resumes if gate=1

- If count written is N then OUT becomes high after N+1 clocks

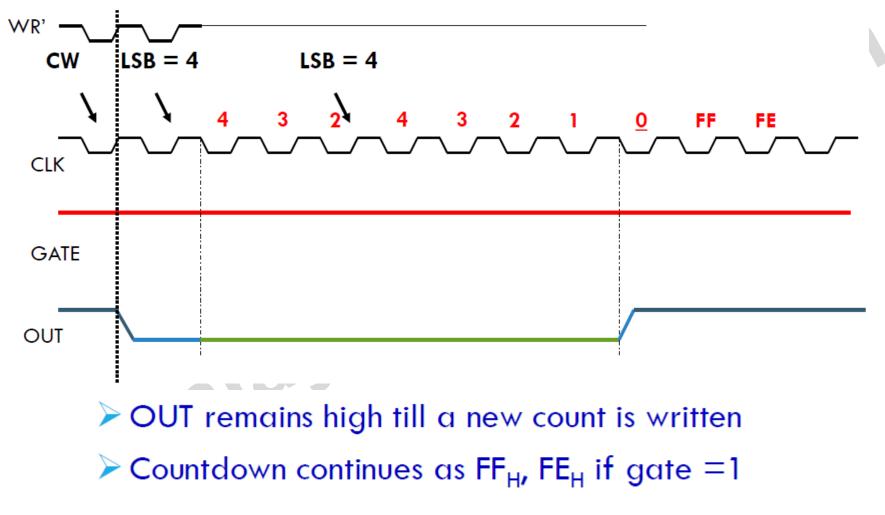

- > OUT remains high till a new count is written

- $\geq$  Countdown continues as FF<sub>H</sub>, FE<sub>H</sub> if gate =1

- Application object counting

## **Mode 0 – Interrupt on Terminal count**

- Output goes high when TC is reached.

- Remains high till counter is re-loaded

- Writing first byte stops counting.

- Writing second byte starts new count.

use:

- 1. Self generated interrupt.

- Programmable delayed event.

4/15/2021

## Mod 0 : Case 1

Now if clock is applied and gate=1, countdown begins

If count written is N then OUT becomes high after N+1 clocks 4/15/2021

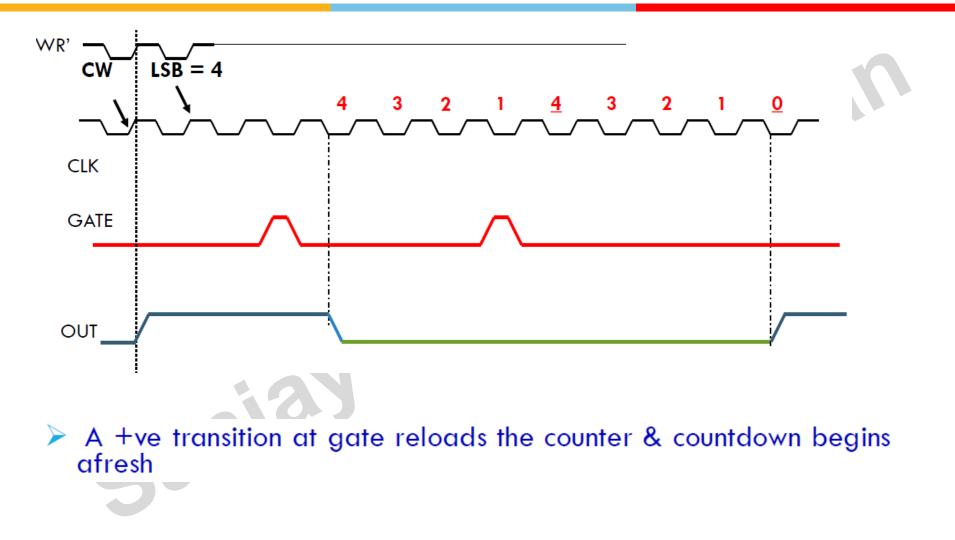

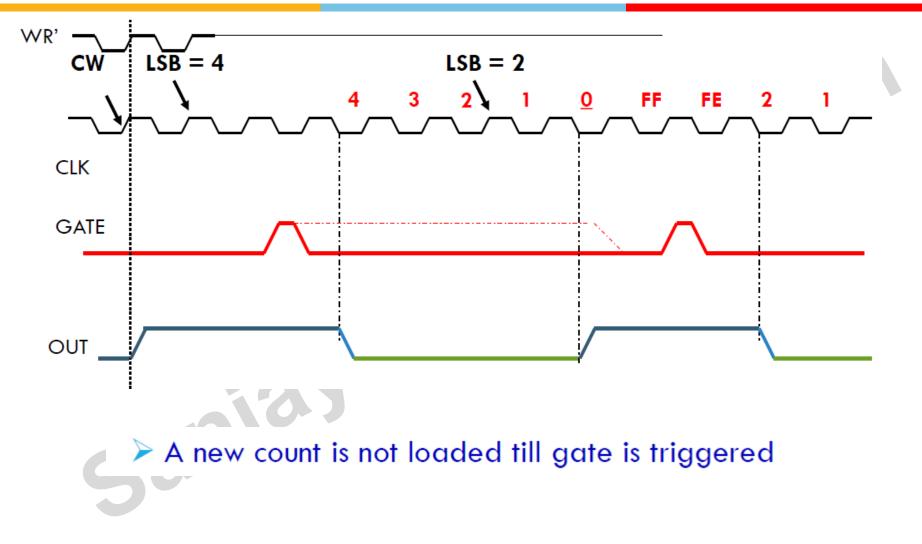

## Mod 0 : Case 2

## Mod 0 : Case 3

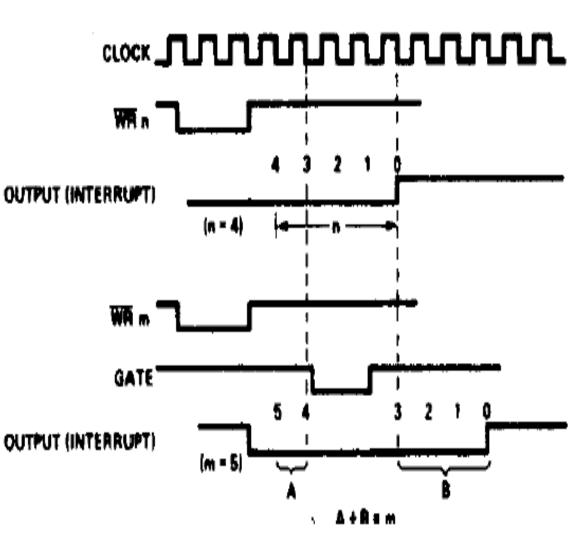

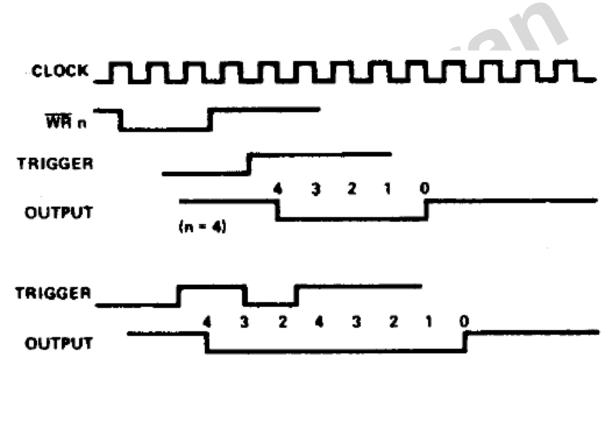

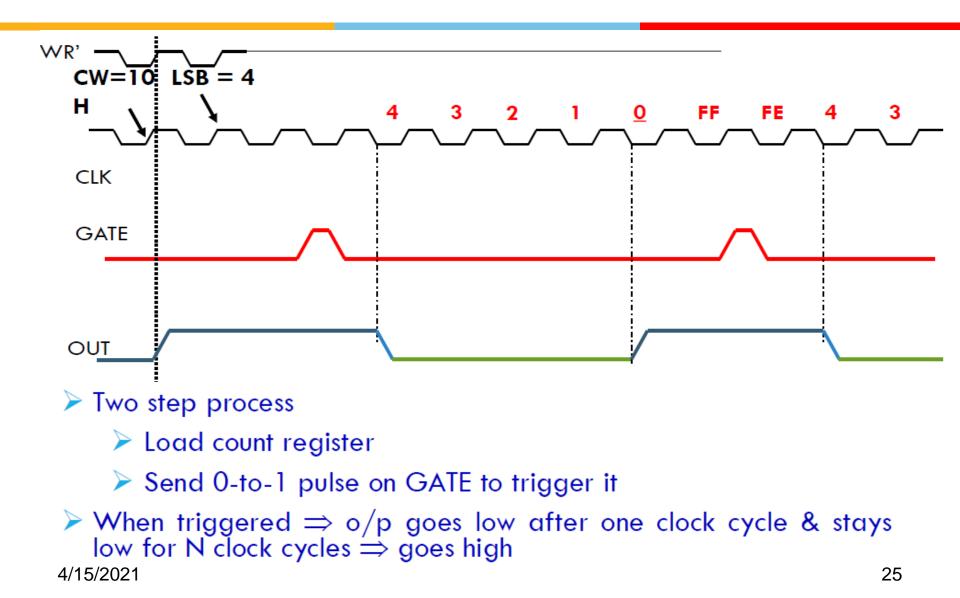

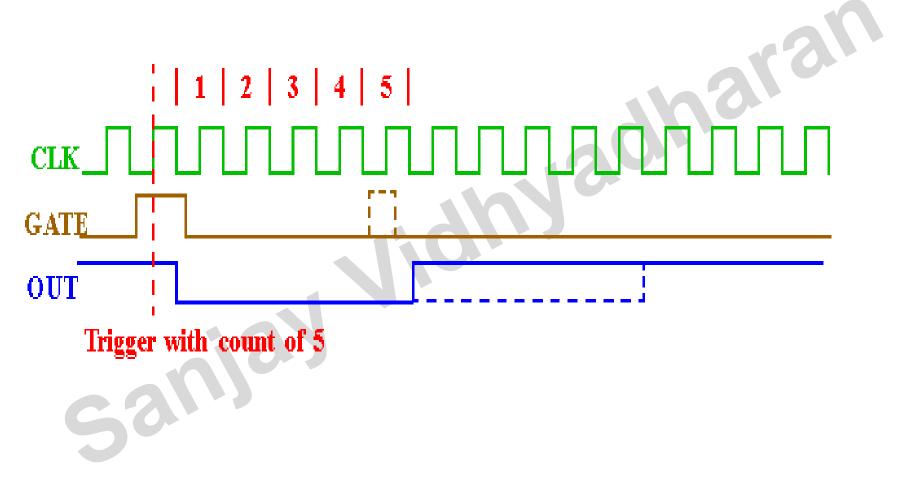

## Mode 1 – Hardware retriggerable one-shot

- Output goes low following raising edge on gate

Output goes high when

- Output goes high when TC is reached.

- Current output not effected by reloading count.

- 4. Re-triggerable

- Use: 1. To create a time window for valid operations 2. Programmable

- 2. Programmable pulse width.

- To measure no activity (silence) for the given period.

## Mod 1: Case 1

## Mod 1: Case 2

## Mod 1: Case 3

## **Modes of counting : Mode 1**

# Thank You

sania