### Microprocessors and Interfaces: 2021-22 Lecture 24 : 8086 Bus Cycle and Loop Delay Calculations

### By Dr. Sanjay Vidhyadharan

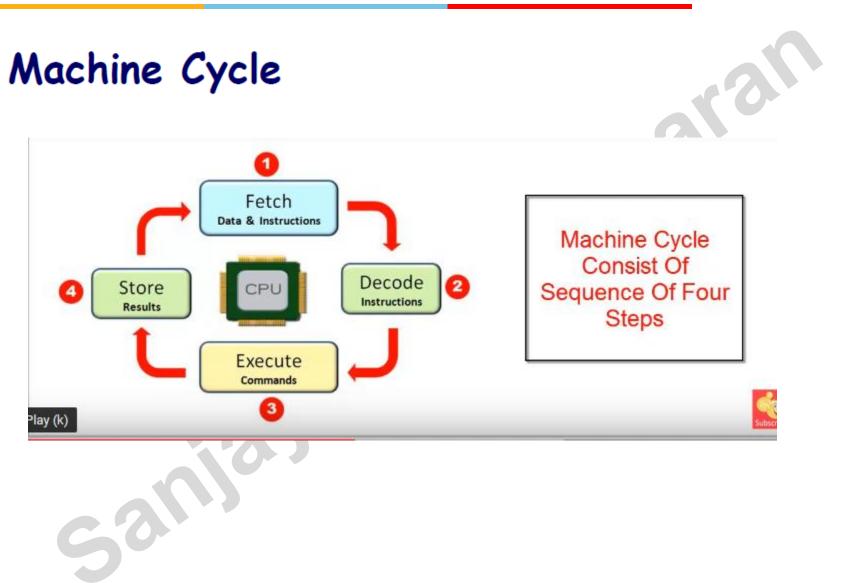

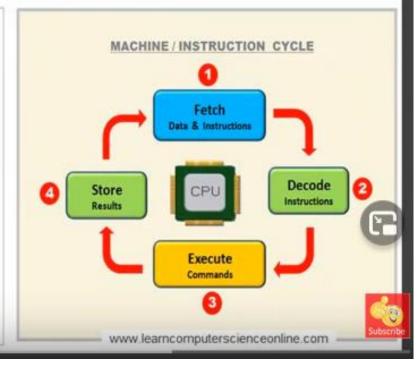

### Instruction Cycle

# Machine Cycle

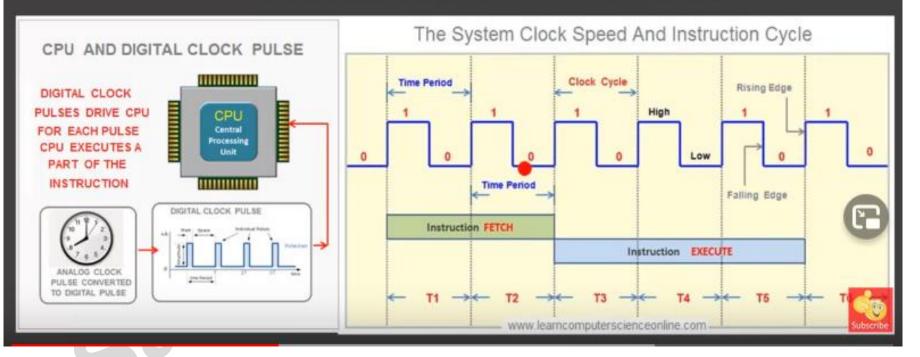

### T states

$\overline{}$

**53**0'

### **Instruction Cycle**

Has more than 1 Machine Cycles

### CPU - Instruction Cycle / Machine Cycle.

The CPUs instruction cycle is executed sequentially and each instruction is processed by CPU which consist of following steps :

- Read an Instruction from memory .

- Decode the instruction as per OPCODE

- Find the address of operand .

- Retrieve an operand.

- Perform the desired operation

- Find the address of destination memory .

- Store the result into the destination memory

www.learncomputerscienceonline.com

### T states

### CPU - The Is Driven By Stream Of Clock Pulses

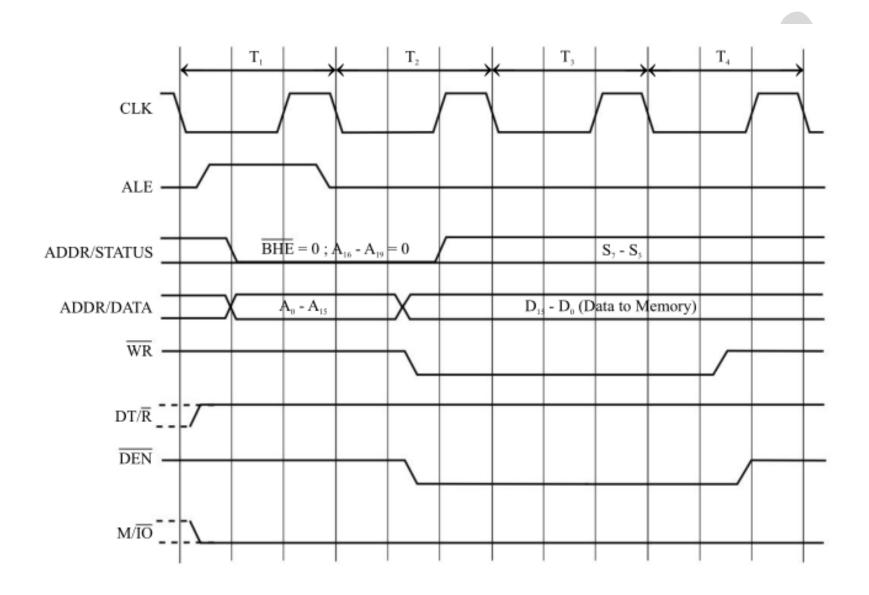

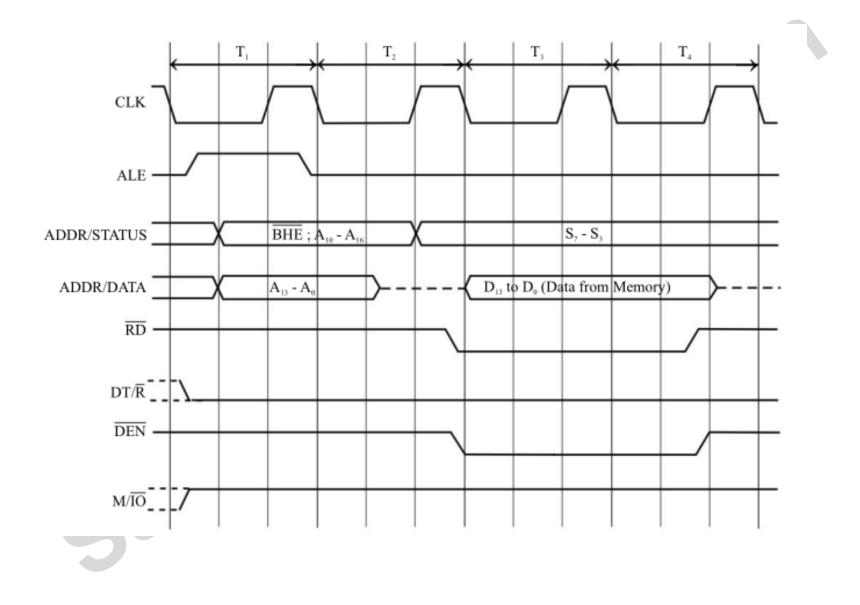

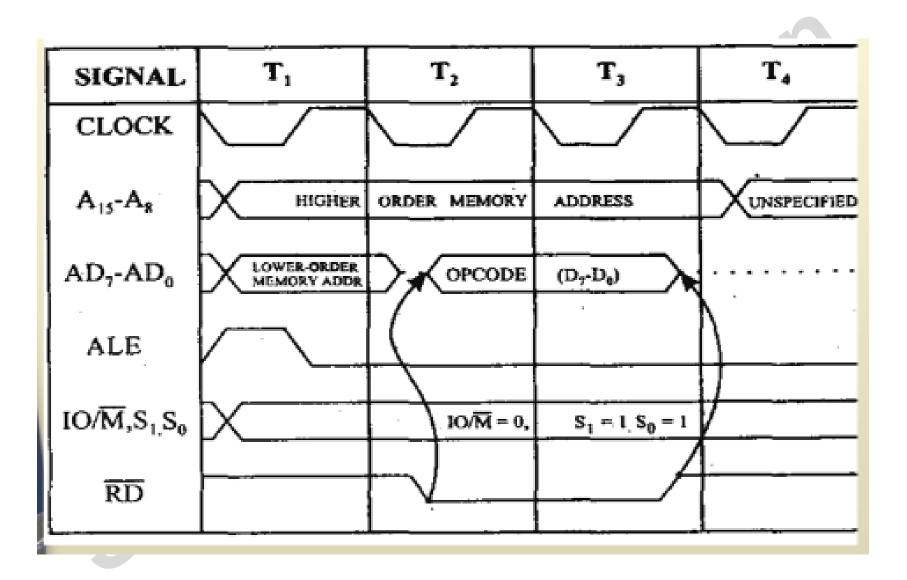

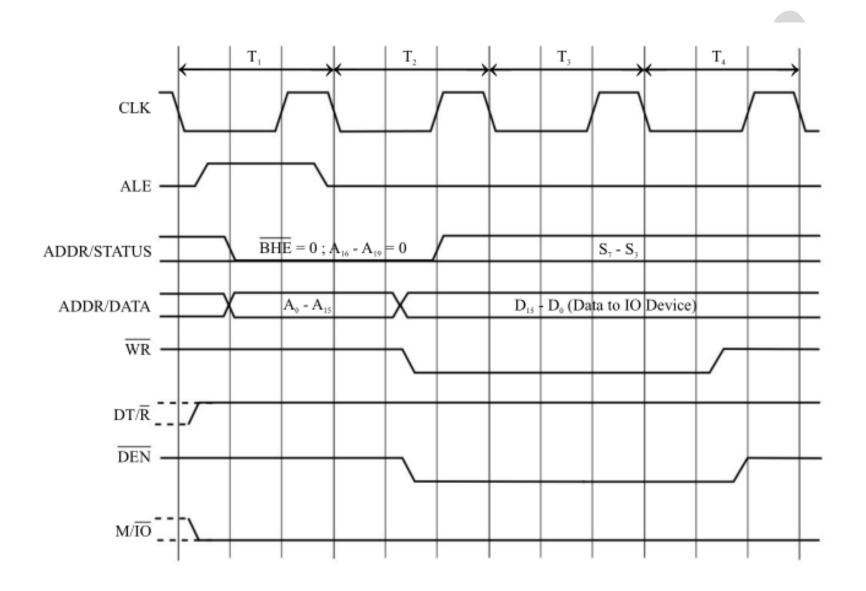

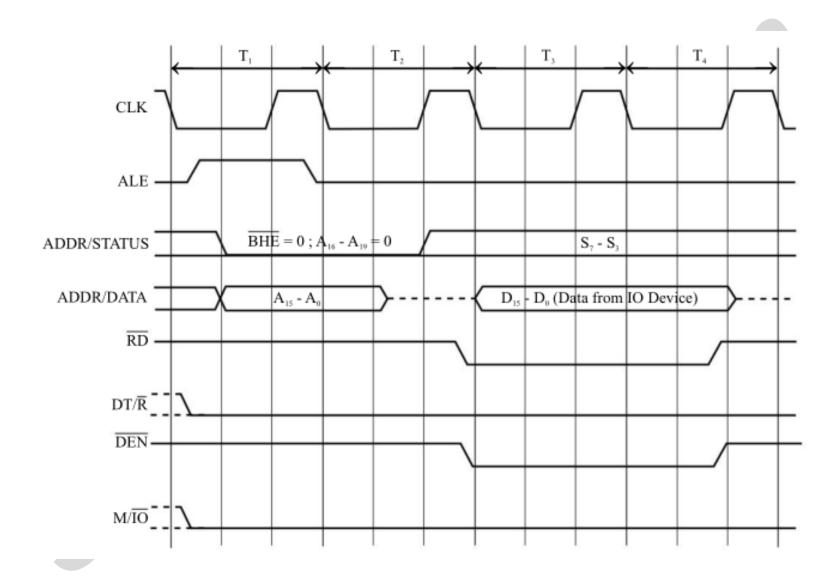

### MACHINE CYCLES OF 8086

1.Opcodefetch cycle (4T) 2.Memory read cycle (4 T) 3.Memory write cycle (4 T) 4.I/O read cycle (4 T) 5.I/O write cycle (4 T)

### **Memory Write Operation**

### **Memory Read Operation**

### **OPCODE FETCH MACHINE CYCLE**

### **IO Write Operation**

### **IO Read Operation**

### **Instruction Cycle**

Time taken by processor to execute an instruction-specified in terms of no. clock cycles needed to do it.

Once instruction is fetched and ready to be executed, then it can be decoded and execution can be set.

| Instruction cycle                                                             |                                                            |

|-------------------------------------------------------------------------------|------------------------------------------------------------|

| Fetch cycle                                                                   | Execute cycle                                              |

| <ul> <li>Control unit obtains an<br/>instruction from memory</li> </ul>       | <ul> <li>Operand is obtained<br/>from memory</li> </ul>    |

| <ul> <li>The instruction is decoded</li> </ul>                                | <ul> <li>Operation is performed<br/>on operands</li> </ul> |

| <ul> <li>Memory is given the address<br/>of the operand to be used</li> </ul> |                                                            |

### FETCH CYCLE

Rules to identify number of machine cycles in an instruction:

1. If an addressing mode is direct, immediate or implicit then No. of machine cycles = No. of bytes/Word.

E.g. INC AX 40h , PUSHF 9Ch, POP AX 58H E.g. MOV AX, BX 8BC3h, MOV AX, [2001h] A10120h

2. If the addressing mode is indirect then No. of machine cycles = No. of Words + 1.

E.g. MOV AX,[BX] 8B07h (Machine cycles = 01+1)

### **Instruction Cycle**

| No | Instruction      | No of clock cycles for execution |

|----|------------------|----------------------------------|

| 1  | MOV AX, BX       | 2                                |

| 2  | ADD AX, BX       | 2                                |

| 3  | MUL BX           | 133                              |

| 4  | MOV BX, N        | 4                                |

| 5  | CMP AX, [BX][SI] | 9+ EA                            |

| 6  | JNZ label        | 16/4                             |

| 7  | LOOP Label       | 17/5                             |

Bus Cycle : No of Machine Cycles required for execution of the Instruction

- MOVAX, BX

- 8B C3

231

• 1 MEMR (OPCODE FETCH)

Bus Cycle : No of Machine Cycles required for execution of the Instruction

- ADD BX, [0110]

- 03 1E 10 01

- 2 MEMR (OPCODE FETCH)

- i.e. 2 Machine cycles

- To execute the instruction

- 1 Machine cycle---- Read Data from [0110]

- Total 3 Machine Cycles

Bus Cycle : No of Machine Cycles required for execution of the Instruction

- ADD [0110], BX

- 01 1E 10 01

- To instruction fetch:

- 2 MEMR (OPCODE FETCH )

- 2 Machine cycle

- To execute the Instruction

- 1 Machine cycle---- Read Data from [0110]

- 1 Machine cycle---- Store Results in DS:0110 -(1 MEMW)

- Total 4 Machine Cycles

Bus Cycle : No of Machine Cycles required for execution of the Instruction

- CBW

- 98

c31

• 1 MEMR (OPCODE FETCH)

### **DELAY LOOPS**

Certain amount of time or delay is associated with the execution of an Instruction.

•Thus instruction execution gives us a means of generating a delay . Consider instructions below,

MOV CX, 100 HERE: LOOP HERE 4 cycles 17/5 cycles

• Total no. of clock cycles required is 4+(100\*17) -12 =1692 cycles

•In a system with 12 MHz clock, clock period is .083 $\mu$  Sec - Total delay in this case .083 \*1692 =140  $\mu$  Sec •It is possible to fix the value of N so as to get a desired value of delay .

### **DELAY LOOPS**

```

MOV CX,N 4

HERE: NOP 3

LOOP HERE 17/5

```

Most of the delay occurs within the loop the total cycles of delay is  $=[(3+17) \times N]-12$ .

```

•

```

Total delay time =1 m sec =20N x 0.083 µsecs

For 1 msec delay ,the value of N =602 or 25AH

•

This value of N is inserted into program to create a delay of 1msec

•

Generating delays in this manner is called software delays.

# **MEMORY ACCESS TIME**

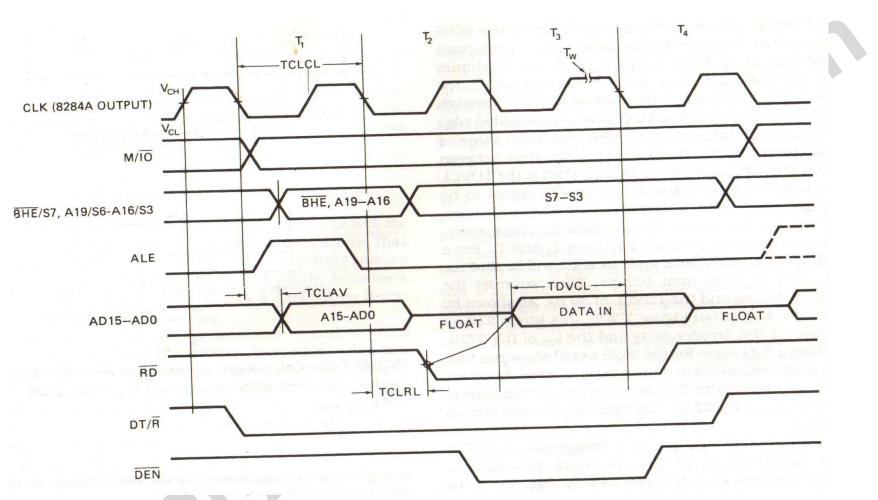

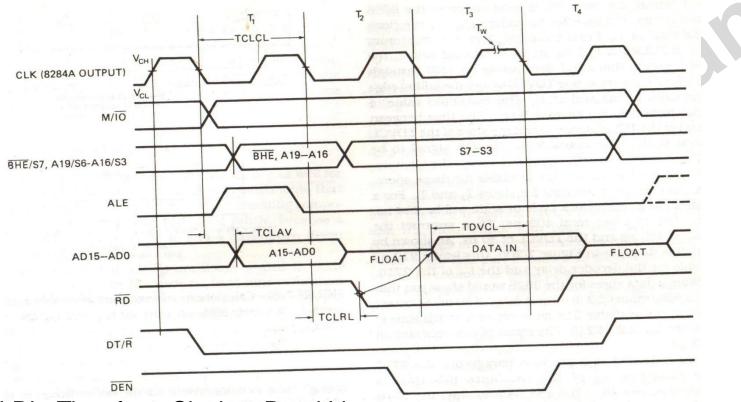

TCLAV- Time from Clock to Address Valid ; 110 ns for MHz Clock Memory Access Time : TCLAV time must be subtracted from the three clocking states (600 ns) separating the appearance of the address ( $T_1$ ) and the sampling of the data ( $T_3$ ).

# **MEMORY ACCESS TIME**

- TCLRL- Time from Clock to Read Line

- TDVCL Time Data Valid to Clock 30ns

- Memory Access Time : 600 ns-110ns-30ns = 460 ns

- A wait state (T<sub>w</sub>) is an extra clocking period between T<sub>2</sub> and T<sub>3</sub> to lengthen bus cycle

- On one wait state, memory access time of 460 ns, is lengthened by one clocking period (200 ns) to 660 ns, based on a 5 MHz clock.

# • Thankyou

sai